基于HDLC幀的零開銷帶內管控設計與實現*

劉 遠,譚 覓,王綱領

(中國電子科技集團公司第三十研究所,四川 成都 610041)

0 引言

高級數據鏈路控制(High Level Data Link Control,HDLC)協議,由于其封裝簡單,且具有良好的流量控制能力和差錯檢測能力,被廣泛應用于各類數字通信領域中[1]。

為滿足信道兩端對數據通信的有效管控,需構建管控數據通道,由于HDLC幀通信的同步傳輸特性[2],帶內管控是較為有效和簡單的管理方式,既可以簡化用戶的網絡拓撲,又具備較好的可靠性。由于HDLC幀數據承載著用戶的關鍵通信信息,因此帶內管控數據通道的構建不應對用戶數據造成損壞。

現有的HDLC幀帶內管控數據通道構建技術[3]無法滿足在HDLC幀滿帶寬傳輸條件下,管控數據即時傳遞且對HDLC幀零損壞的要求。本文提出的零開銷帶內管控技術,可以有效解決此設計難點,提高HDLC幀數據的傳輸效率。此外,管理幀采用偽隨機序列,可實現管控信道誤碼糾錯。使用現場可編輯邏輯門陣列(Field Programmable Gate Array,FPGA)方案實現設計,可提高功能實現的可靠性,降低引入的信道時延。

1 HDLC幀結構

HDLC協議以幀作為單位傳輸數據,基本的幀結構如圖1所示[4]。

圖1 HDLC幀結構

標志F為開始或結束標志字。固定為16進制碼“7E”,當信道處于空閑狀態時,標志F也作為幀與幀之間的空閑填充。如果開始和結束標志位之間的幀數據含有“7E”,需對數據進行轉譯[5]。地址域為接收端的地址。控制域用于構成各種命令和響應,以便對業務鏈路進行監視和控制。信息域為幀的凈荷數據部分,根據不同的行業標準,長度限制也有所不同。幀校驗域為兩個標志位之間數據的CRC校驗結果[6]。

本文所設計的HDLC幀的零開銷帶內管控技術,不需要解析HDLC幀的內容。本文中的“HDLC數據”是指HDLC幀去掉開始和結束標志“7E”后的數據內容。

2 管控幀示例

端到端通信設備之間傳遞的控制數據,以自定義幀的方式傳遞。本文提供一個管控幀結構的示例,如圖2所示。

圖2 管控幀示例

幀頭設定為偽隨機m序列[7],用于指示管控幀的起始位置。本文使用的m序列生成多項式為:

初值設置為0,截取使用其前8字節數,即16進制數“83CA90BB7DCF897A”。長度字段L代表整個管控幀的字節數,自定義位為1字節長度;凈荷數據為管控幀內承載的管控信息數據,用戶自定義其最大長度;校驗和字段用于驗證管控幀數據傳輸的正確性,本文使用1個字節的累加和進行校驗。

3 實現原理

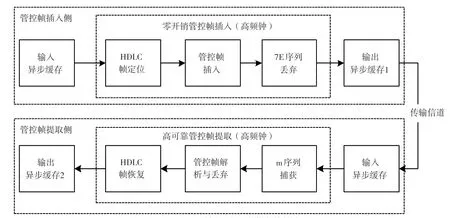

根據HDLC幀的特點,幀頭幀尾的標志位都是“7E”,結合自定義管控幀的數據結構,設計基于HDLC幀的零開銷帶內管控方案如圖3所示。

圖3 基于HDLC幀的零開銷帶內管控實現原理

3.1 輸入輸出緩存

采用對HDLC幀進行隨路鐘緩存、高頻鐘處理的方式[8],構建管控數據通道。輸入輸出緩存用于隨路鐘與高頻鐘的隔離,同時保證管控幀插入和提取處理時,不影響數據通信的連續性。

輸出異步緩存1中需緩存2個字節數據,用于預留判斷HDLC幀標志位時產生的延時。輸出異步緩存2中需緩存管控幀最大長度字節數,確保在管控幀解析與丟棄的時候,輸出數據不被間斷。異步緩存的設計,將會引入信道傳輸延時,延時的計算公式為Lmax×8/R,其中,Lmax表示用戶自定義的管控幀最大長度字節數,R表示隨路鐘的波特率。

3.2 零開銷管控幀插入

零開銷管控幀插入工作在高頻時鐘域,由3個模塊組成,其中,HDLC幀定位模塊根據HDLC幀結構特點檢測HDLC幀的標志位。管控幀插入模塊,使用高頻時鐘實現管控幀數據的一次性插入,插入管控幀的位置在HDLC幀定位模塊檢測到2個標志位后的位置,保證在管控幀插入位置的HDLC幀間隔內至少有2個標志位,從而滿足HDLC幀恢復模塊的實現要求。

“7E”序列丟棄模塊使用高頻時鐘,在插入管控幀之后的“7E”位置,根據管控幀插入的總長度,完成對“7E”數據的丟棄,以保證管控幀的插入不會對鏈路引入新的開銷。根據HDLC數據間標志位“7E”的個數,分兩種情況完成“7E”序列的丟棄。

情況1:當管控幀插入位置的HDLC數據間的“7E”字節數大于或等于L+2時,如圖4所示,在一次性插入管控幀數據后,可以連續完成管控幀長L的“7E”數據丟棄。

情況2:當管控幀插入位置的HDLC數據間“7E”字節數小于L+2時,如圖5所示,在一次性插入管控幀數據后,不能連續完成管控幀長度L的“7E”數據丟棄,需要在后續HDLC幀間繼續丟棄“7E”,并且保證HDLC數據間至少留有1個“7E”,用于指示HDLC幀間隔。

圖5 管控插入的幀間空閑L<+2(含滿帶寬情況)

3.3 高可靠管控幀提取

高可靠管控幀提取,工作在高頻時鐘域,由3個模塊組成。其中,m序列捕獲模塊通過自相關計算實現m序列定位[9],設置相關判決門限為60,8字節m序列可以實現3比特糾錯[10];管控幀解析和丟棄模塊基于管控幀格式完成幀解析,并根據解析出的長度完成管控幀數據的丟棄,刪除對HDLC幀空閑的占用;HDLC幀恢復模塊,根據HDLC數據間標志位“7E”的數量和進入方向“7E”序列丟棄模塊的原理,分以下幾種情況完成HDLC幀的恢復。

情況1:當管控幀丟棄后,數據仍為“7E”,則可以一次性回填管控幀長度L的“7E”,此過程為圖4的逆向。

圖4 管控插入的幀間空閑≥L+2

情況2:當管控幀丟棄后,數據為非“7E”,說明在下一幀HDLC數據后仍需回填“7E”,圖6表示在管控幀丟棄后,下一個HDLC數據間隔中,“7E”個數大于1的情況,可以直接在這個幀間隔中回填L長度的“7E”。

圖6 能在管控幀下一幀HDLC間隔完成一次性“7E”回填

情況3:當管控幀丟棄后,數據為非“7E”,并且下一個HDLC數據間隔中,“7E”個數等于1時,則需在這個幀間隔中回填1個字節的“7E”,然后繼續尋找下一個HDLC數據間隔,繼續回填,直至回填完L長度的“7E”,恢復原始HDLC幀數據,如圖7所示。

圖7 不能在管控幀下一幀HDLC間隔完成一次性“7E”回填

在HDLC滿帶寬情況下,原始HDLC幀頭和幀尾至少組成2個標志位,結合零開銷管控幀插入中情況2的“7E”序列丟棄原理和高可靠管控幀提取中情況3的HDLC幀恢復原理,可以實現HDLC幀滿帶寬通信情況下的零開銷管控數據傳輸。

4 FPGA實現

FPGA實現和仿真都基于第3節中自定義的管控幀結構開展設計。

4.1 零開銷管控幀插入FPGA實現方案

實現方案如圖8所示,通過異步緩存、管控幀高頻插入、標志字“7E”的判決、丟棄等方式,實現零開銷管控幀插入。

圖8 零開銷管控幀插入FPGA實現方案

4.2 高可靠管控幀提取FPGA實現方案

如圖9所示,通過異步緩存、管控幀高頻插入、m序列捕獲、標志字“7E”的判決、回填等方式,實現高可靠管控幀提取。

圖9 高可靠管控幀提取FPGA實現方案

5 FPGA仿真

使用FPGA仿真軟件modelsim對第5節方案進行仿真。

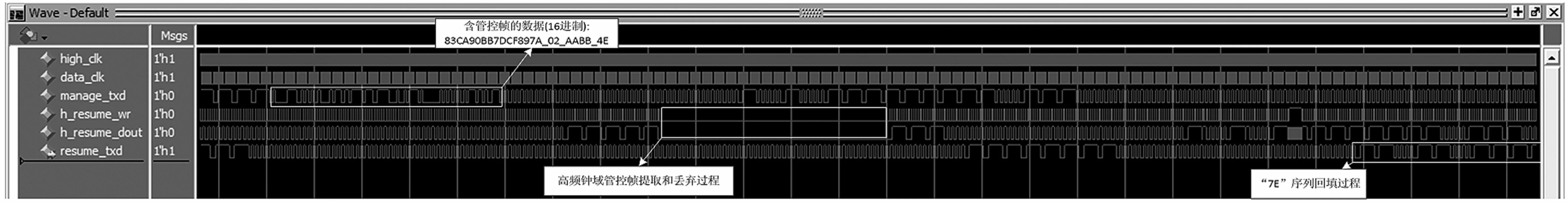

5.1 零開銷管控幀插入仿真

圖10為進入方向的仿真結果,信號data_clk和high_clk分別為隨路鐘和高頻鐘,信號manage_in_flag為管控幀插入指令,信號org_rxd為輸入的HDLC幀數據,信號h_manage_dout和h_manage_wr分別為進行管控幀插入和“7E”序列丟棄的高頻鐘域數據和有效信號,信號manage_txd為完成管控幀插入和“7E”序列丟棄后的隨路鐘域輸出數據。仿真結果顯示,在收到管控幀插入指令后,通過高頻鐘完成管控幀數據的插入和“7E”序列的丟棄,并將含有管控幀數據(83CA90BB7DCF897A_02_AABB_4E)的HDLC通信幀通過隨路鐘輸出。

5.2 高可靠管控幀提取仿真

圖11為外出方向仿真結果,信號manage_txd為含管控幀數據的隨路鐘域HDLC幀數據(圖10的輸出結果),信號h_resume_dout和h_resume_wr分別為進行管控幀提取、丟棄和“7E”序列回填的高頻鐘域數據和有效信號,信號resume_txd為完成管控幀丟棄和“7E”序列回填的隨路鐘域輸出數據。仿真結果顯示,通過m序列捕獲,定位到管控幀位置,并通過高頻鐘完成管控幀數據的提取、丟棄和“7E”序列的回填,并將最終恢復的HDLC幀原始數據通過隨路鐘輸出,實現了HDLC幀的零開銷帶內管控功能。

圖10 零開銷管控幀插入modelsim仿真結果

圖11 高可靠管控幀提取modelsim仿真結果

6 結語

本文提出了基于HDLC幀的零開銷帶內管控技術,有效解決了端到端HDLC通信零開銷帶內管控通信構建的難點問題,在保證不損壞原有HDLC幀的條件下,提高了帶內管控通道的性能,可以滿足在HDLC幀滿帶寬傳輸條件下的零開銷帶內管控需求。該技術可以有效應用于信號資源有限、傳輸帶寬緊張的環境中,如衛星無線通信等環境。本文給出的FPGA詳細設計方案,實現簡單、資源占用少,可靈活應用于各種規模的FPGA設計項目中。FPGA仿真驗證結果證明了本方案的可實現性。此外,本文所提方案已經在多個項目中得到應用。