一種通用SDR平臺的設計與實現

張仁良, 周昌義, 胡婉如,2, 安軍社

(1.中國科學院 國家空間科學中心,北京 100190; 2.中國科學院大學 計算機科學與技術學院,北京 101408)

軟件無線電(Software-Defined Radio,SDR)具有結構開放、軟件可編程、硬件可重構和支持多種頻段等特點,在現代通信系統中占據著重要的地位,無論在軍事[1]、微小型衛星[2],還是在商業通信[3]中都有很大的影響力。

SDR主要特點是通用化、標準化、模塊化和對頻段的廣泛覆蓋性。硬件系統本身支持的頻段或者通過擴頻再結合軟件配置,基本可以滿足多種通信場景中應用的需求。

隨著國外各種先進技術應用于SDR平臺,目前基本實現了3個目標:① 高度集成化;② 模塊化;③ 面積最小化。AD9371[4]是最具代表性的一款集成電路(Integrated Circuit,IC),內部提供可靠的鏈接,包含了20多個高性能分立式無線電元件,極大減小了芯片面積,純die(芯片)僅為7.8 mm×8.2 mm。NI公司的USRP(Universal Software Radio Peripheral,通用軟件無線電外設)[5]是模塊化的代表,其封裝為一個黑盒子,用戶連接外部設備再配合上位機即可使用。國內主流的SDR平臺實現方法有兩種:① 依賴于離散元件的組合[6];② 采用國外的模塊化方案,例如使用AD9361[7]、AD9364等一體化射頻芯片和Radio420s射頻板[8]等搭建平臺。

本文提出一種較為先進的SDR平臺,其目的是使用SDR方式,靈活地改變通信的參數,適用于多種應用場景,例如作為地檢測試應答機與無人機、直升機進行通信,通過軟件可以直接設置相關參數,極大地提高了配置的靈活性,擴大了應用范圍。

1 硬件設計方案

Kintex7嵌入了MicroBlaze軟核,可以對AD9371進行配置,收到的RX信號解調為基帶信號,經過ADC轉換和濾波后送入JESD204B接口,發出的信號通過JESD204B接口送出,再經過濾波及DAC轉換和混頻后輸出到TX接口。完成這些操作需要一個硬件平臺,所以筆者主要介紹整體硬件設計方案,并對選用AD9371和Kintex7來搭建平臺的原因做出闡述。

1.1 AD9371外圍芯片概述

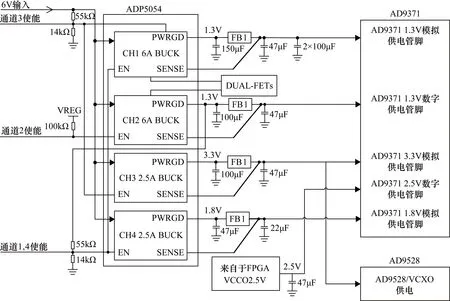

AD9371的電源供電使用四通道高性能降壓DC-DC調節器ADP5054。使用14路LVDS/HSTL輸出的JESD204B時鐘發生器AD9528產生AD9371和Kintex7之間的同步時鐘來同步高速數據總線JESD204B。

AD9371是一款高度集成的寬帶RF收發器,提供2個發射器(Tx)、2個接收器(Rx)、2個觀測接收器(ORx)、三通道嗅探接收器(SnRx),集成了頻率合成器和數字信號處理功能。

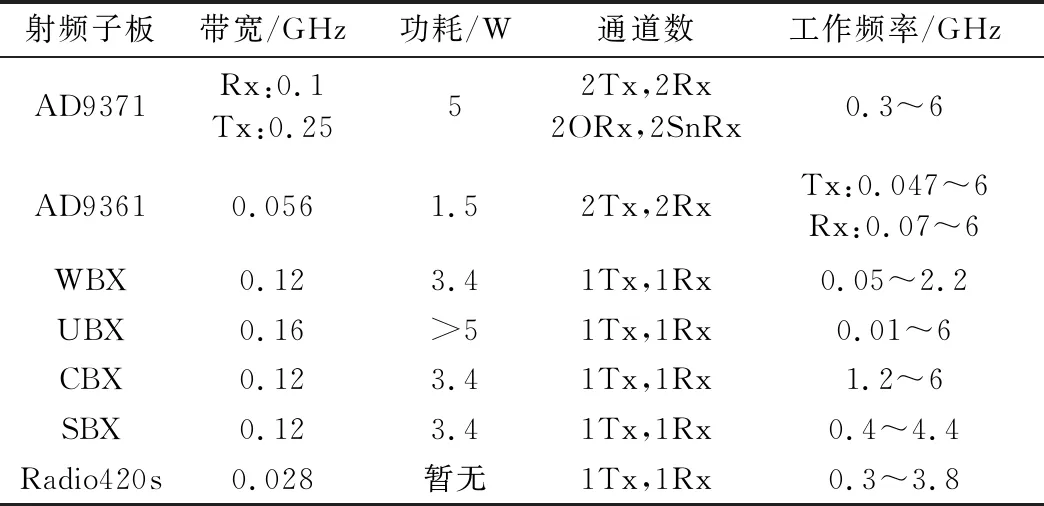

射頻子板參數對比如表1所示。由表1可知,AD9371無論是在工作頻率、帶寬還是在通道數量上都具有明顯優勢,采用JESD204B串行接口[9]作為數據傳輸通道,最高數據率可達6144 Mbit/s。其他平臺皆采用LVDS或其他并行接口進行數據傳輸,最高速率僅為1.0 Gbit/s。雖然其功耗在表1所列的其他平臺中處于劣勢,但在性能上處于第一位置。參考AD9371功能框圖可知[10],其中SnRx和ORx共享ADC和數字處理器。4個高速的串行接口用于發射鏈路,4個串行鏈路被Rx、ORx和SnRx通道所共享。

表1 射頻子板參數對比表

1.2 Kintex7外圍芯片概述

Kintex7的外圍芯片包括:4收4發的RS422接口、4收4發的LVDS高速接口、1片W5300網口芯片。其中,RS422和LVDS接口使用J14-26連接器,網口使用RJ45連接器;外接1片DDR2芯片作為存儲器的擴展;外接配置Flash用于存儲調制解調、JESD204B接口協議和MicroBlaze代碼;1片128 Gbit的NAND Flash用于存儲大量數據。

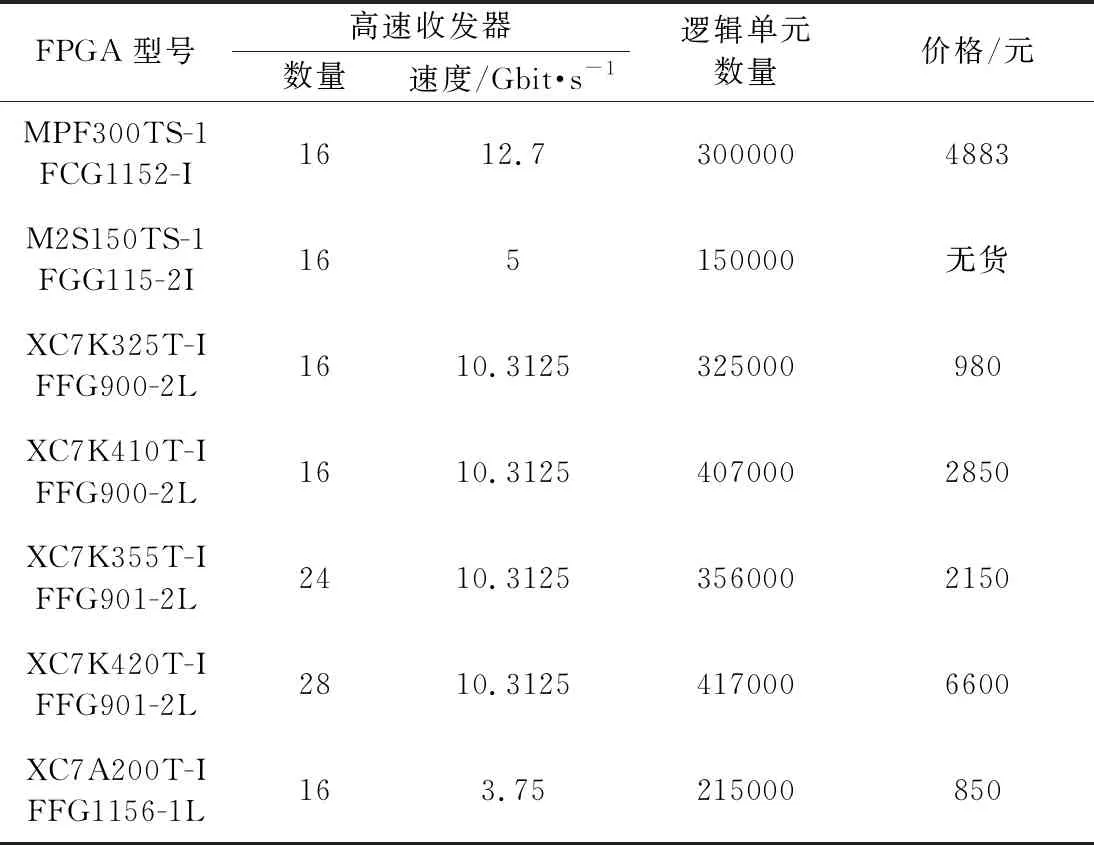

表2為對Microsemi和Xilinx公司幾款FPGA的邏輯單元、收發器數量(速率)價格等方面的比對,依據性價比最終選擇了XC7K410T,其在容量、速度、邏輯單元數量、價格方面都處于優勢地位,對于本平臺來說比較適合。

表2 FPGA產品特性對比

1.3 整體硬件原理框圖

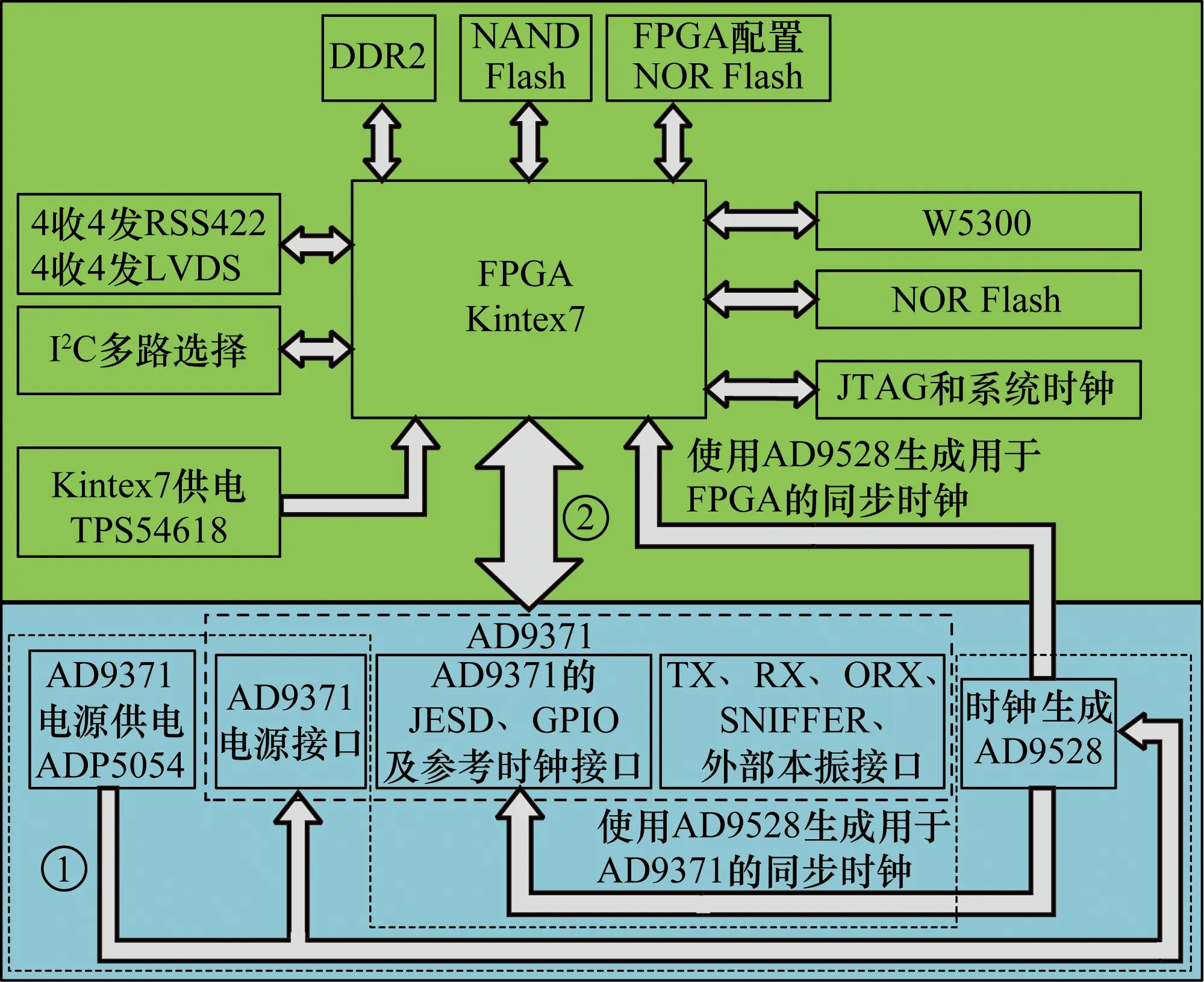

原理框圖如圖1所示。原理分為兩個部分,其中綠色底圖為Kintex7外圍連接;淺藍色底圖為AD9371外圍連接;中間使用箭頭②表示Kintex7和AD9371的信號連接。

圖1 原理框圖

箭頭①為AD9371的電源拓撲,采用ADI公司的ADP5054四通道BUCK作為供電芯片,AD9371電源拓撲如圖2所示,模擬供電使用通道1、3、4,數字供電使用通道2以及FPGA輸入的2.5 V電源。

圖2 AD9371電源拓撲

通過控制使能信號,使AD9371的上電順序為先數字1.3 V供電,再模擬1.3 V和1.8 V供電,模擬3.3 V可以任意時間上電。

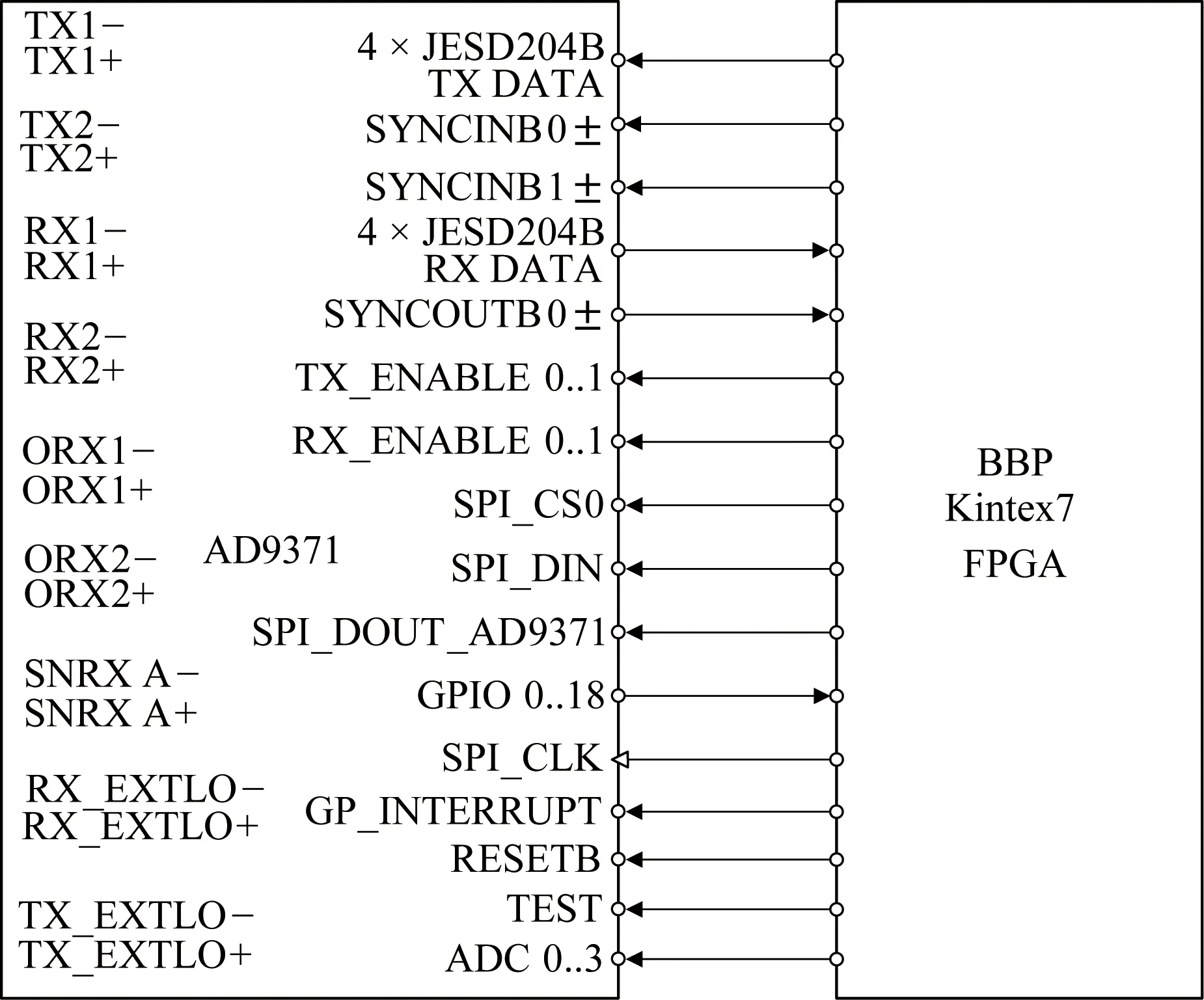

圖3為AD9371與Kintex7之間的信號流及射頻接口,SPI配置信號和高速串行數據總線JESD204B是AD9371與FPGA之間的主要連接信號。其他需要重點注意的信號主要有:同步輔助、復位、測試和GPIO信號。

圖3 AD9371與Kintex7信號流圖

2 PCB設計注意事項

遵守AD9371的PCB設計規則是該硬件系統成功的重要前提,下列四點對于提升硬件性能具有重要意義。

① 疊層和阻抗匹配。

② 布局時模擬部分和數字部分分開。

③ 需要根據優先級布線,先布高優先級的信號線,再布低優先級的信號線。

④ 各RF射頻信號中引入隔離結構,以達到通道之間的隔離度要求。

2.1 疊層和阻抗匹配

PCB板為14層盲埋孔混壓板,頂層和底層使用Rogers基材降低高頻損耗。Rogers基材下的層2和層13為GND層,作為RF傳輸線的參考平面,以保證信號的完整性。為了實現電源通道之間的良好隔離,層3和層12用于電源域的布線。高速串行接口JESD204B在層5和層10布線,以達到RF信號和高速數字信號良好隔離的目的。余下的低速數字控制信號布在層7和層8。

為了在不改變現有疊層的情況下增加線寬,對RF信號走線使用單獨的阻焊開窗模型。

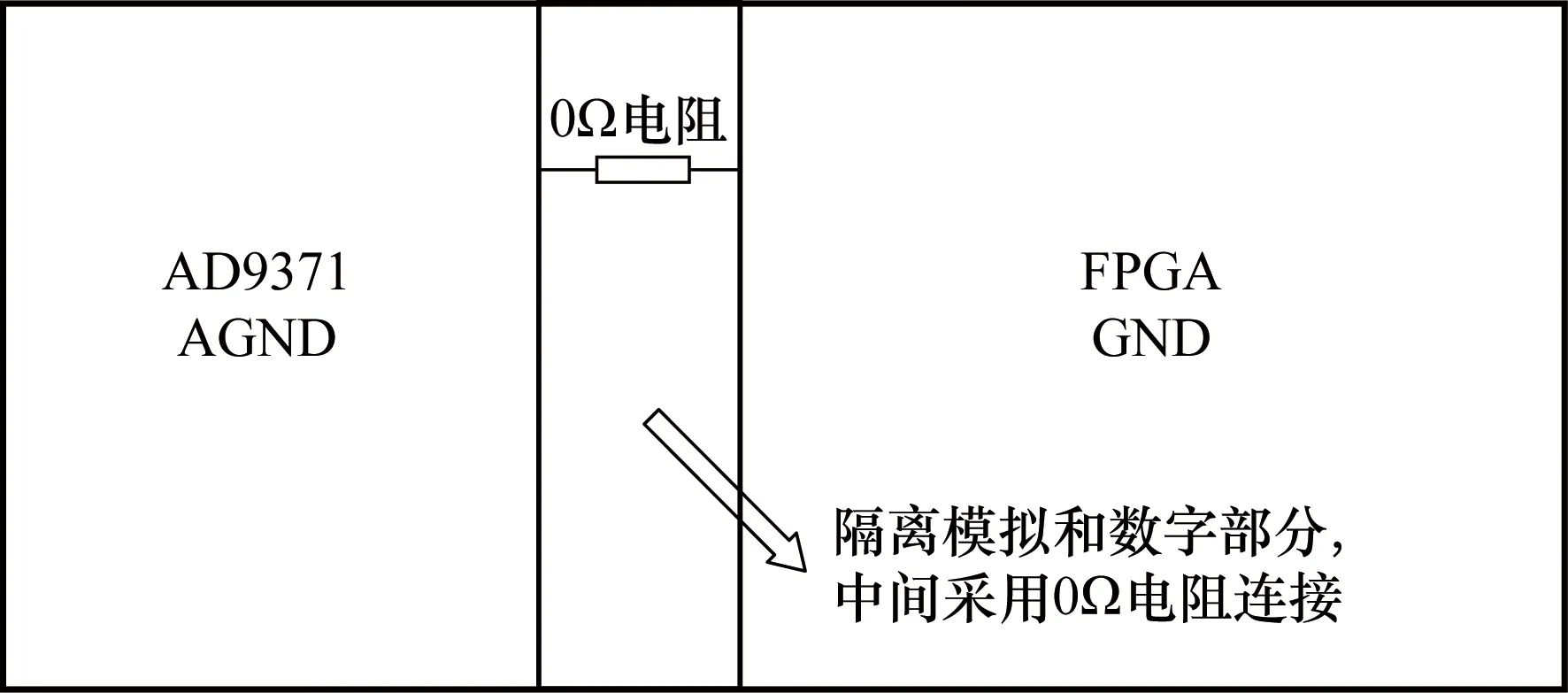

2.2 布局原則

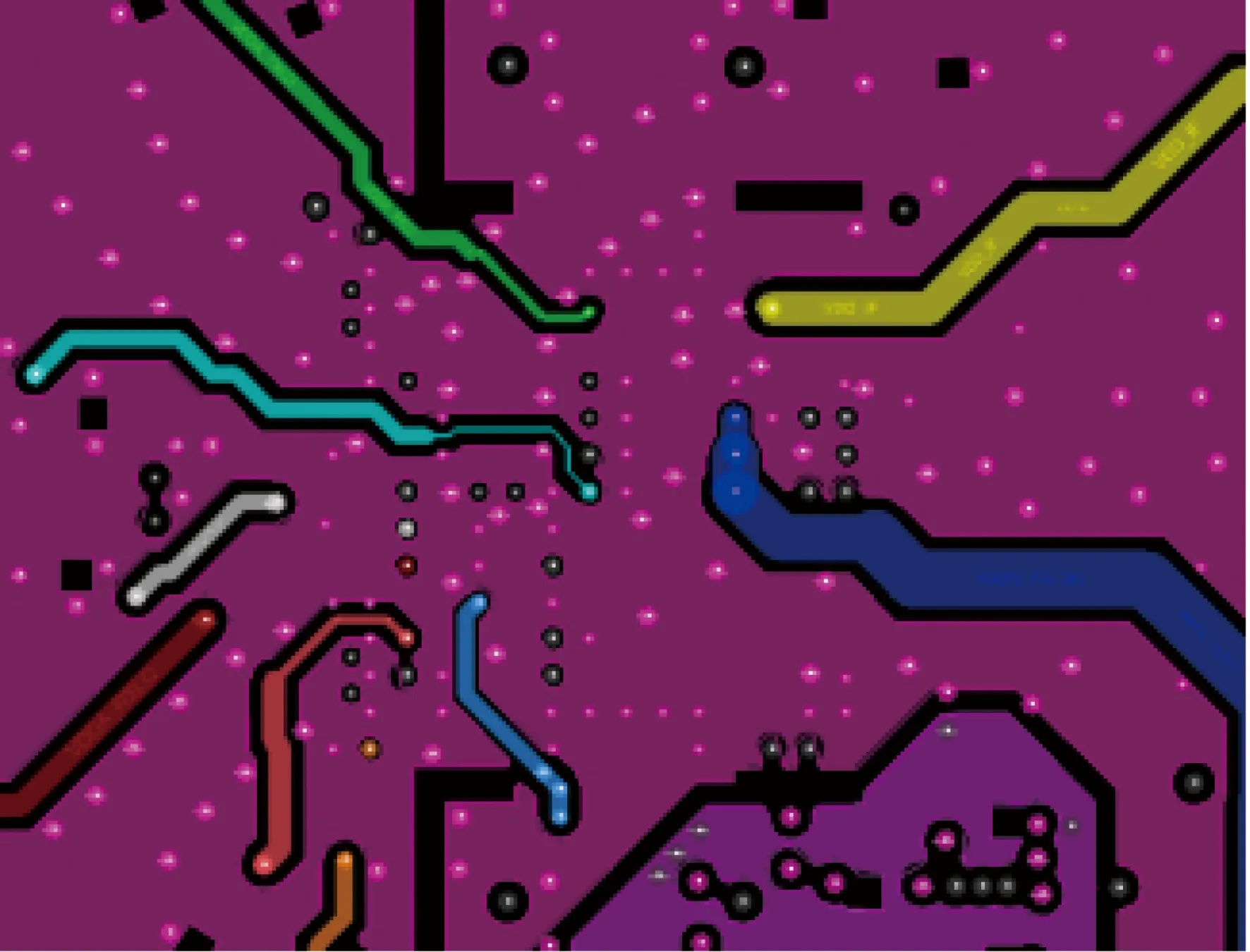

AD9371模塊(模擬電路)和Kintex7模塊(數字電路)是本硬件電路設計的兩個主要組成部分。AD9371和Kintex7模塊布局如圖4所示,為了減少兩個模塊之間的信號和回流干擾,將AD9371模塊擺放在左邊,Kintex7模塊擺放在右邊。另外,將AD9371模塊的地命名為AGND,Kintex7模塊的地命名為GND,鋪地階段AGND和GND單獨鋪地,中間使用0 Ω電阻或銅皮連接,極大地減少了二者之間的回流干擾。需要注意AD9371模塊表層與內層鋪地需要保持一致。

圖4 AD9371與Kintex7模塊布局示意圖

2.3 布線優先級

為了保證AD9371的關鍵信號可以在PCB設計階段就獲得足夠的設計優化空間,第一優先級是RF和JESD204B信號,二者需要最早布線。第二優先級是電源信號,最低優先級的是低速數字信號。需要嚴格按照布線優先級的順序布線,以達到不干擾關鍵元件的布局和布線的目的。

2.3.1 第一優先級RF線設計規則

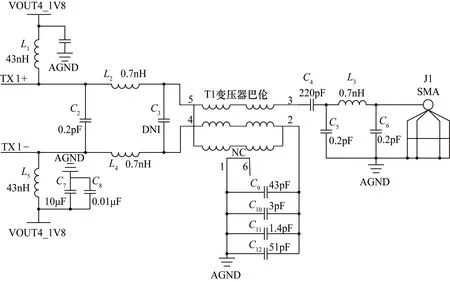

以RF發射通道1舉例介紹其設計規則,圖5為AD9371發射通道的電路原理圖。

由于本設計的巴倫沒有提供直流中心引線,所以將繞線式電感(Chokes)連接在VOUT4_1V8和Tx輸出之間,以滿足Tx輸出所需要的200 mA電流。圖5中的L1、L5為繞線式電感;C7為Tx電源的儲能電容器。當改變衰減值的時候,為了有效減少靜態電流,要通過1.8 V的電源域向巴倫直流供電。在進行PCB設計時候,必須將發射通道1和通道2的1.8 V供電路徑做好隔離,且不允許使用銅皮連接繞線式電感,只允許使用引線直連[11]。

圖5 AD9371發射通道電路原理圖

2.3.2 第一優先級JESD204B線設計規則

要求在開始PCB設計時候就布JESD204B信號。為了減少JESD204B信號走線插損,要求AD9371盡可能靠近Kintex7放置,使走線長度盡可能短,保證直接芯片間互聯。層5布JESD204B發射信號,層10布JESD204B接收信號,信號線上層、下層使用完整的GND平面作為參考。JESD204B走線嚴格控制為100×(1±10%)Ω的到地阻抗,要求差分對共面、松耦合和線寬最大。

為了保持阻抗的連續性,線寬必須盡可能接近Pin/Ball的寬度,1 oz(1 oz=35 μm)銅皮厚度,線寬至少為8 mil(1 mil=0.0254 mm),走線的參考地面不能跨分割或中斷。連接器和無源元件的焊盤尺寸與JESD204B的線寬盡可能接近,以避免由于阻抗不連續導致的信號反射串擾等問題。

2.3.3 第二優先級電源線設計規則

電源供應品質直接影響整個系統性能,但遵循下面的布線要求,就可以保證各個模擬電源域之間具有良好的隔離度。為了保證每條電源布線都被地面包圍,電源布線應遵循星狀布線法,數字和模擬電源Ball都通過磁珠電阻的隔離后單獨布線來完成供電。

圖6為電源布線示例,顯示了在層12上的電源布線結構,每條電源線之間通過包地和接地過孔來隔離。

圖6 電源布線示例

電源引腳要求放置0.1 μF或(0.1+10)μF旁路電容,對于數字供電和JESD204B供電還需要加入100 μF濾波電容以減少低頻干擾。通過鐵氧體磁珠FB(Ferrite Bead)供電時,需注意FB、旁路電容應盡可能靠近Ball放置,FB必須通過引線連到儲能電容器,每個Ball的FB應隔開放置以確保它們的電場互不影響。

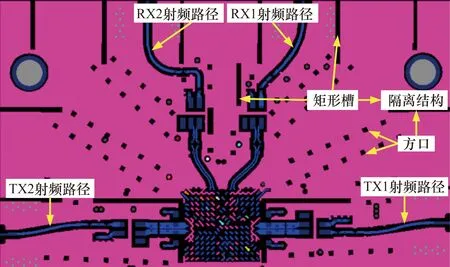

2.4 AD9371信號隔離規則

為了確保收發器滿足AD9371數據手冊中的通道隔離要求,本平臺需要滿足以下的隔離指標要求。分為RF隔離和JESD204B隔離,二者隔離距離計算方法一致,前者計算的是隔離方口的距離,而后者是包地過孔距離,這里僅介紹RF隔離設計規則。

2.4.1 隔離結構

AD9371Datasheet中隔離參數要求如下。

① 在6 GHz時,Tx to Tx不少于80 dB。

② 在6 GHz時,Tx to Rx不少于80 dB。

③ 在6 GHz時,Rx to Rx不少于60 dB。

④ 在6 GHz時,ORx to ORx不少于60 dB。

為了實現這些目標,引入了兩種隔離結構。

隔離結構由矩形槽和方口組合構成,圖7展示了在本設計中所用的隔離結構。采用矩形槽主要是為了快速加大隔離區域,且PCB設計效率較高,但如果都采用矩形槽設計,就會導致其他低速和電源信號沒有布線空間。方口雖然設計起來比較麻煩,但方口之間還可以進行信號布線,且不會使隔離度惡化。

圖7 通道隔離結構

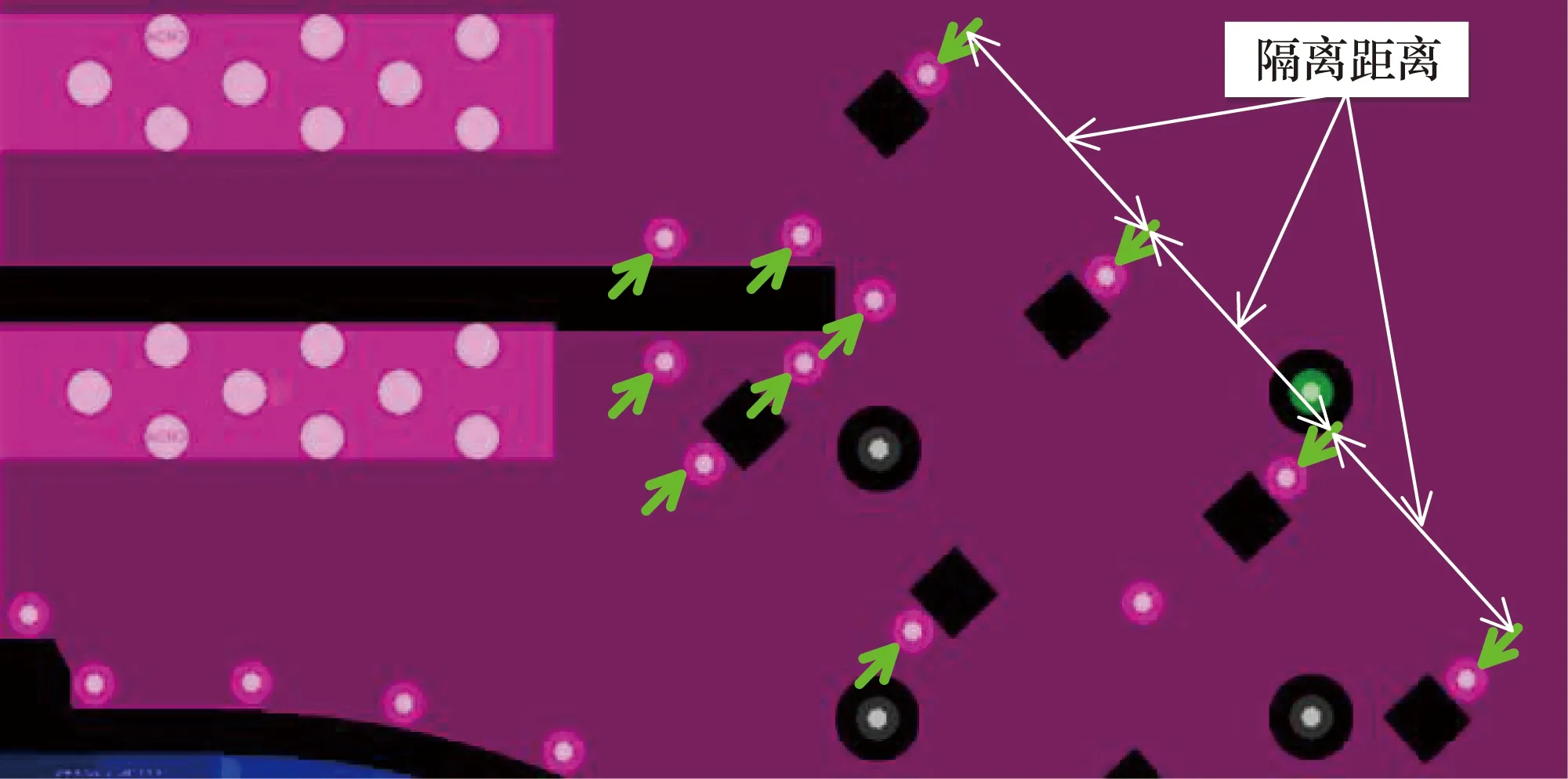

使用方口、矩形槽時,需要就近放置地過孔,可以參考圖8綠色箭頭所指的放置方法,方口至少需要一個,矩形槽需要在周圍放置多個。過孔應是通孔,過孔的作用是就近引導返回電流到靠近方口或矩形槽的地層。

圖8 放置回流過孔和隔離距離示例

2.4.2 隔離距離計算

設計PCB圖紙時,方口之間的間距應不超過最高頻率波長的1/10,如圖8中的白色箭頭所示的隔離距離。

波長可以使用式(1)來計算。

(1)

式中:εγ為隔離材料的介電常數;f為RF頻率,一般取最大值;λ為RF信號波長。

AD9371最大的RF信號的頻率是6 GHz。對于Rogers 4350B板材,εγ為3.5。由式(1)可計算出λ為26.73 mm,即最小的波長為26.73 mm。

為了滿足1/10波長的規則,方口的間距必須小于等于2.673 mm。

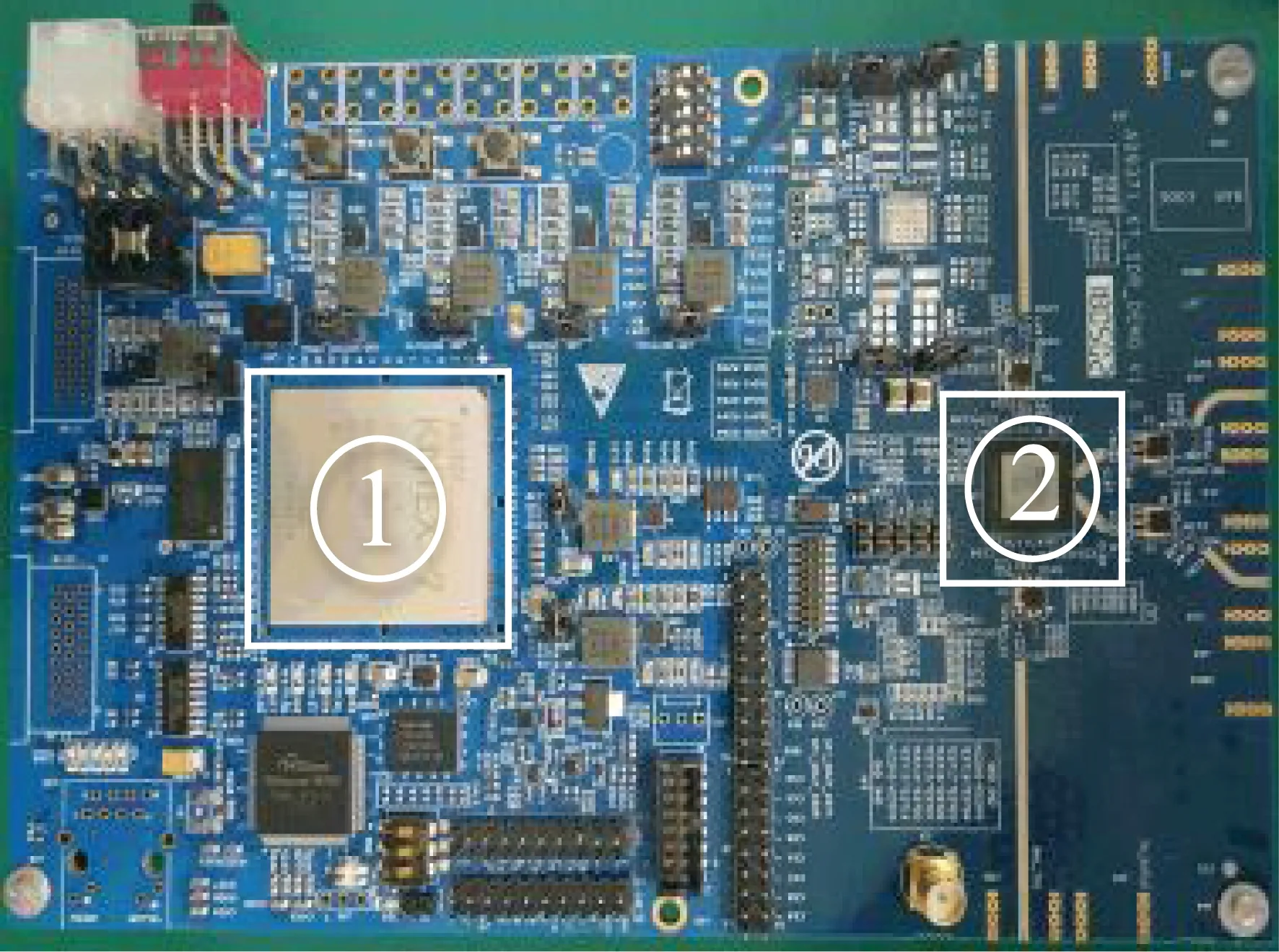

3 SDR平臺硬件測試

平臺硬件實物如圖9所示,標號①為FPGA IC,標號②為AD9371 IC,整板布局緊湊,測試也證明了此種布局分開的方法是正確的,板子性能良好,解決了模擬與數字相互干擾的問題。

圖9 硬件實物

目前AD9371數據發射有兩種方法,一種為DMA模式,另外一種為DDS模式。

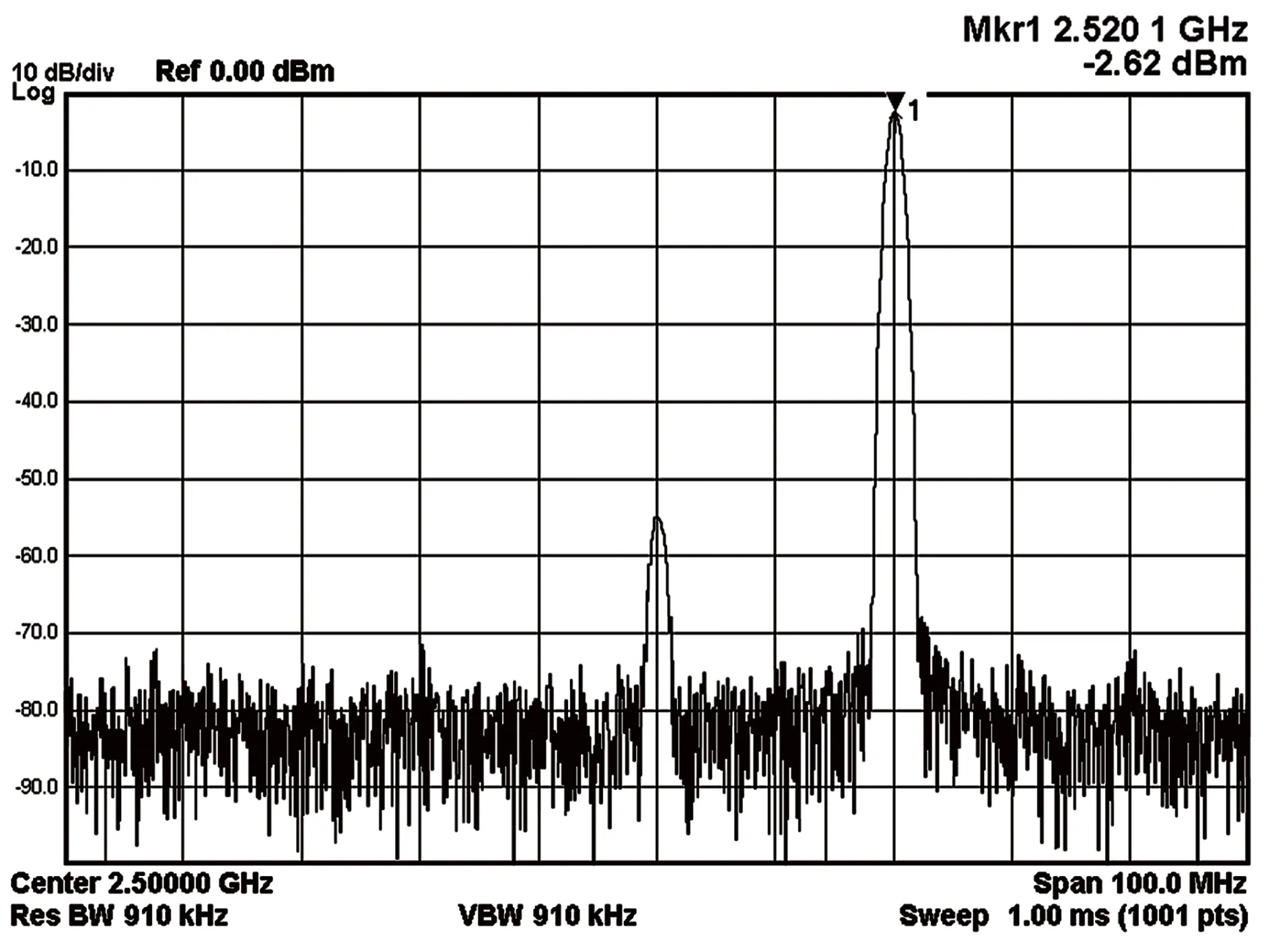

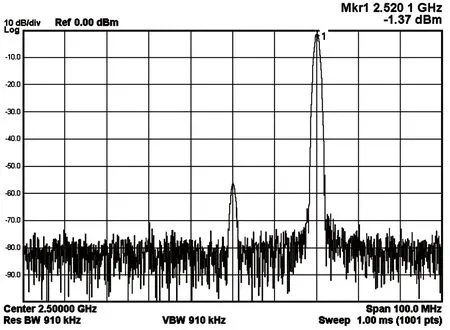

測試數據為2.5 GHz載波+20 MHz正弦波,采用DDS模式。圖10為官方DEMO板對應的增益,為-2.62 dBm;圖11為本平臺對應的增益,為-1.37 dBm。頻譜儀參考電平設為0 dBm,頻寬設置為100 MHz,測試代碼增益設置相同,衰減系數設為0,通過對比大量頻譜儀增益數據,可以看出其明顯比官方DEMO板提升了1~2 dB的增益。

圖10 官方DEMO板DDS模式測試頻譜

圖11 本平臺DDS模式測試頻譜

4 SDR平臺軟件設計

本平臺直接在MicroBlaze中跑C語言代碼,過程如下[12]:ADI提供TES(Transceiver Evaluation Software)軟件,此軟件最大的優勢在于集成了所有AD9371可以配置的寄存器,將設置好的采樣、載波頻率、模式、濾波器等參數直接轉換為C語言代碼,再配合ADI專用于配置AD9371的API接口代碼,將這些代碼整合到一起,使用Vivado最終生成MCS文件,將其載入到配置Flash中。當硬件上電時,邏輯代碼將按照其存儲的地址空間順序載入到FPGA的SRAM中,完成MicroBlaze軟核處理器的初始化,再讀取配置Flash中的C語言代碼,配置好AD9371。

4.1 Verilog代碼框架

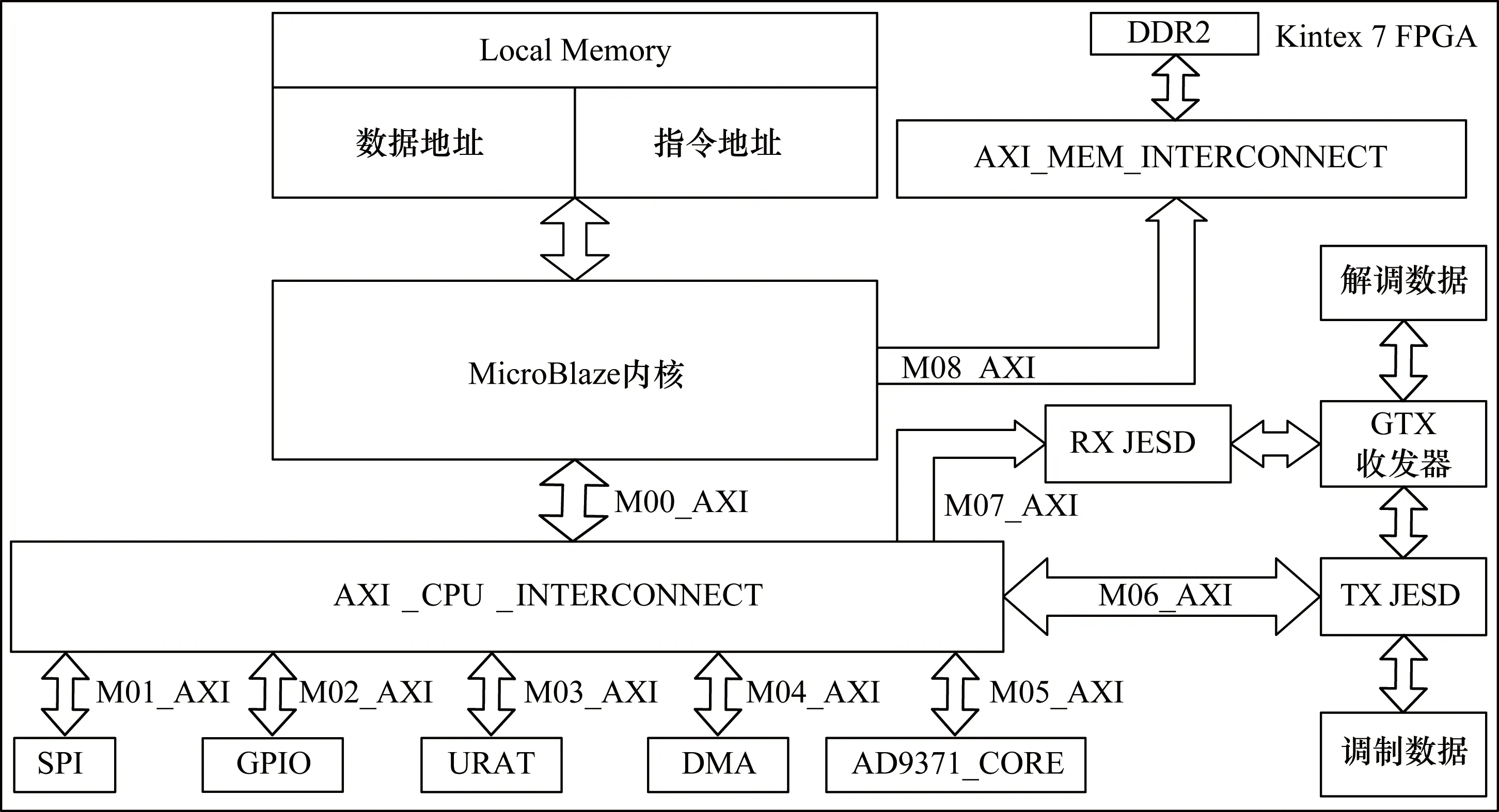

Verilog代碼框架如圖12所示,這里只給出部分重要的代碼模塊。MicroBlaze軟核通過AXI總線轉PLBv46總線連接低速IP模塊,SPI用于配置AD9371的相關寄存器,串口用于打印AD9371配置流程信息,JESD204B TX/RX用于連接AD9371數據通道。其余的I2C、INTC和GPIO為拓展接口。

圖12 基于MicroBlaze的代碼框架

數據發射的兩種模式如下。

① DMA模式下,在MicroBlaze初始化完畢后,將事先存儲在Flash中的正弦波矩陣送入DDR2暫存,隨后由DMA接口直接送入AD9371數字接口,再經過DAC采樣送入到混頻器中加入載波,最終送到發射通道。

② DDS模式下,MicroBlaze直接通過配置AD9371_CORE IP生成不同相位和不同頻率的通道波形。

4.2 MicroBlaze總線連接

圖13為MicroBlaze軟核的部分總線連接圖,其中AXI_CPU_INTERCONNECT模塊為AXI轉PLBv46模塊,用于連接外設模塊。M00_AXI~M08_AXI為主總線。其中,M06_AXI和M07_AXI直接連接JESD204B RX和TX IP,二者共同連接到JESD204B PHY IP即實際物理接口IP,這個IP直接與硬件引腳對應。調制數據和解調數據為拓展代碼。

圖13 基于MicroBlaze的總線圖

5 結論

經測試,本平臺系統性能良好,增益比官方DEMO板提高了1~2 dB,且總體功耗沒有增加,維持在5 W左右。

對比NI和ADI的平臺,目前ADI的AD9371一體化射頻芯片解決方案雖然犧牲了功耗,但在芯片面積、適配性和性能上占有絕對優勢。

本平臺的意義在于降低傳統離散化硬件設計的復雜度,實現面積最優化。嵌入MicroBlaze軟核處理器,通過修改C語言代碼即可修改AD9371的配置參數,無須修改FPGA邏輯代碼,有效簡化了配置流程,極大地提升了應用到多種工作場景的效率。所提出的SDR平臺具有商用價值,可以根據需求靈活、快速地適配不同場景,甚至可以更換處理器軟核(如選擇NiosII[13]、龍芯[14]等),通過提升處理器的速度,也間接提升了平臺的事務處理性能。

雖然一款通用的SDR平臺可以應用于多種場景,但還是有以下劣勢:

① 使用受到功率、穩定性、成本和半導體技術的限制。

② 對于特定波形的處理必然增加復雜度和成本。

③ 無法實現很高的頻率,對于更高的頻率(如12 GHz),目前只能離散化,集成化無法實現。

當然集成化的方案目前在航天領域還無法應用,離散化的方案穩定性更高一些。雖然本平臺具有航天應用潛質,但由于航天環境比較復雜,最終能否適應,還需要在可靠性和穩定性方面繼續做深入研究。