一種高速跳頻信號的數字信道化寬帶接收設計

王 杰

(中國西南電子技術研究所,四川 成都 610036)

0 引言

通信偵察的主要任務是利用電子情報偵察手段對敵方發射的輻射源信號進行搜索與截獲、分選與識別、調制參數測量和解調譯碼等。當前美國及北約國家的數據鏈均采用了高速跳頻和直接序列擴頻體制[1],其具有跳頻速度快、頻點多、帶寬寬、擴頻碼復雜等特點,信號的捕獲、跟蹤和檢測極為困難[2]。

針對信號的捕獲跟蹤,傳統的偵察方式為將接收的射頻信號通過模擬下變頻變換到中頻信號,經過AD 數字采樣后送數字信號處理模塊完成信號的頻譜計算和功率估算等,從而完成信號的檢測和分選識別。該方法針對帶寬小、跳速慢、頻點少的信號效果較好,但針對跳頻帶寬、頻點多的信號則處理能力不足,FPGA 的資源無法滿足多路信號同時下變頻、濾波和頻譜并行計算處理。此外,當前裝備發展的趨勢是低功耗、小型化方向發展,傳統模擬下變頻方式已經很難滿足這方面的需求。

美國亞德諾半導體公司(Analog)先后推出了AD9361、AD9371 及ADRV9009 等類型的射頻頻率捷變芯片,隨著芯片的換代升級,其芯片的功能越來越強大,其中ADRV9009芯片的處理帶寬可達200 MHz。本文提出基于ADRV-9009+Zynq 的處理架構實現寬帶高跳速信號的數字信道化寬帶接收設計,后端FPGA 處理采用多相濾波處理方式,通過抽取后再濾波,可大大節省FPGA 的硬件資源。該方法可針對特定頻點間隔的高速跳頻信號、擴頻信號等,經仿真調試和FPGA 板級調試均有較好的效果,大大節省了FPGA 的使用資源,具備推廣到其他非協作信號偵察的應用前景。

1 高速跳頻信號的工作原理

高速跳頻信號主要應用于通信電臺、敵我識別、數據鏈等平臺上,其主要采用了跳頻、直接序列擴頻和跳時等反偵察通信技術,具有較低的截獲慨率。

針對該類信號跳頻快和帶寬大的特點,采用寬帶數字信道化接收和高速數字信號處理相結合的技術,從而為后端的信號檢測和參數估計提供預處理的數據。

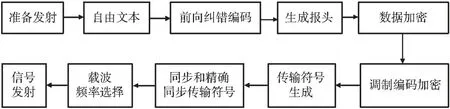

圖1 所示是一種常規的高速跳頻信號的信號發射流程,完成跳頻之前該跳頻信號還會進行擴頻調制、加密處理和載波選擇等,故對其偵收處理的難度較大。

圖1 高速跳頻信號波形的發射流程

2 針對高速跳頻信號的寬帶偵收總體設計

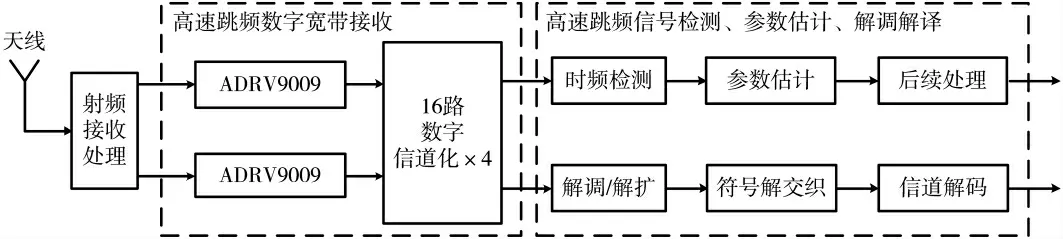

針對高速跳頻信號的偵收包含三個關鍵技術:寬帶接收處理設計、信號的參數估計和信號的解調解譯。其處理的流程如圖2 所示,本文主要針對前端高速跳頻信號的寬帶接收處理設計展開分析。前端天線接收的信號通過兩片ADRV9009 芯片完成L 頻段信號的下變頻和AD 采樣。采樣后的兩路數字基帶信號送入一片FPGA實現濾波、數字信道化處理,變成每路采樣率較低的基帶信號。

圖2 高速跳頻信號偵收處理流程

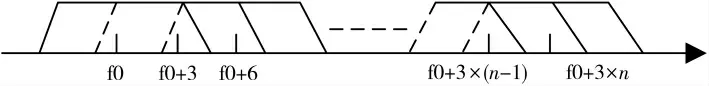

假定某高速跳頻信號的通道間中心頻率間隔為3 MHz,其跳頻帶寬為300 MHz 左右,有效帶寬為64 個,為了保證偵收對信號的全概率覆蓋,多相濾波數字信道化采用50%的混疊設計。多相濾波數字信道化各信道帶寬設計為6 MHz,接收通道1、2 輸出涵蓋頻段為前段150 MHz,劃分為32 個信道,接收通道3、4 輸出頻段涵蓋后段的150 MHz,劃分為32 個信道。多相濾波數字信道化處理由4 個完全相同的16 路數字信道化組成,通過控制ADRV9009 不同的射頻頻點可實現某高速跳頻信號頻段的全覆蓋。其信道劃分如圖3 所示。

圖3 高速跳頻信號寬帶數字信道化

3 ADRV9009 工作原理及特點

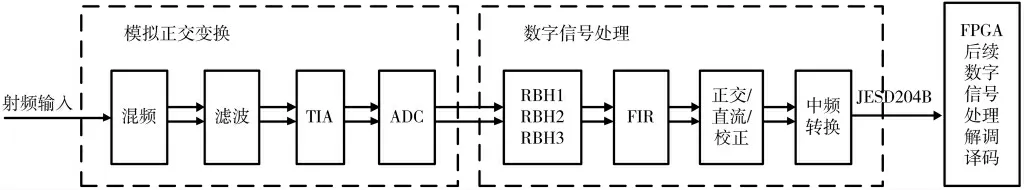

ADRV9009 是一款高度集成的射頻 (RF)捷變收發器,提供雙通道發射和接收器、集成式合成器和數字信號處理功能。其1 路接收通道的處理流程如圖4 所示。

圖4 ADRV9009 的接收處理流程

ADRV9009 接收鏈路按信號流程依次為:模擬正交混頻、TIA (跨導放大器)、ADC、第一級抽取、第二級抽取、可編程FIR 濾波器、正交校正、直流校正、直流增益和中頻變換后通過JESD204B高速接口后送后端FPGA 完成后續數字信號處理及解調/譯碼[3-4]。

ADRV9009 的接收通道最大可支持帶寬為200 MHz,而某高速跳頻信號的最大帶寬達300 MHz,因此兩片ADRV9009 的四個接收通道可實現高速跳頻信號的全帶寬覆蓋[5]。

4 針對高速跳頻信號多相濾波處理的原理

如前文所述,本文用兩片ADRV9009 實現高速跳頻信號的全帶寬覆蓋。ADRV9009 輸出的是經過抽取、濾波后的零中頻基帶信號。鑒于ADRV9009 送入的是基帶I、Q信號,因此,本設計采用復數的數字信道化多相濾波結構[6-7]。

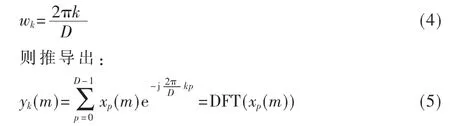

根據復信號的信道化原始結構,可得第k 路信道的輸出[8]為:

各信道可選擇奇劃分和偶劃分,為了推導及實現方便這里選擇奇劃分,令:

根據以上推導,可得基于多相濾波結構的信道化接收機結構模型如圖5 所示。

圖5 復信號的多相濾波結構

由于D 倍抽取器位于濾波器之前,每個信道的抽取濾波器不是原來的原形低通濾波器h(n),而是該濾波器的多相分量hp(m),其運算量降至原來的1/D,極大地提高了該信道化接收機的實時信號處理能力。多相濾波數字信道化具有數字信號處理的全帶寬、全概率覆蓋、各通道并行處理等特點,而且其運算量低,便于硬件實現[9-10]。

5 FPGA 的多路數字信道化處理設計

5.1 FPGA 處理流程

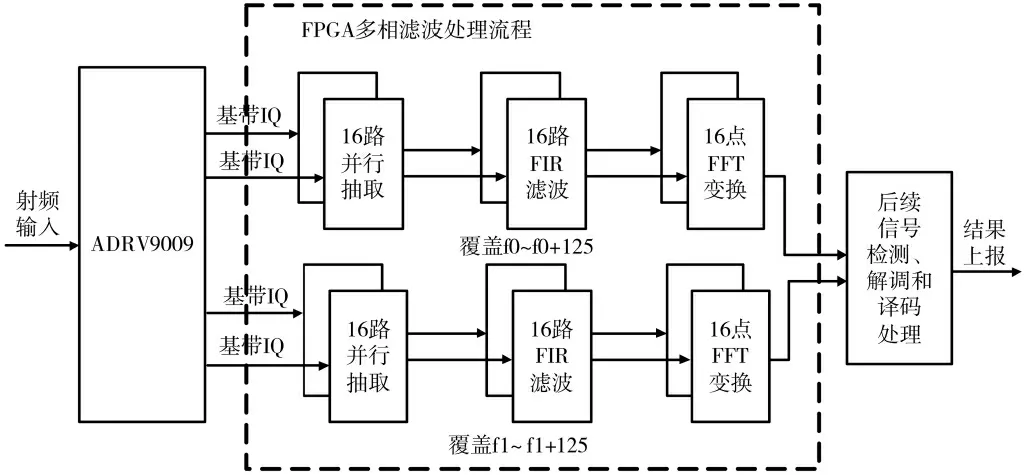

FPGA 采用Xilinx 的XC7Z045,FPGA 主要完成ADRV-9009 芯片的驅動配置和AD 信號接收。接收的零中頻基帶數字信號經16 倍抽取、濾波和16 點FFT 變換后輸出各路通道的處理結果。其處理流程如圖6 所示。

圖6 FPGA 的處理流程

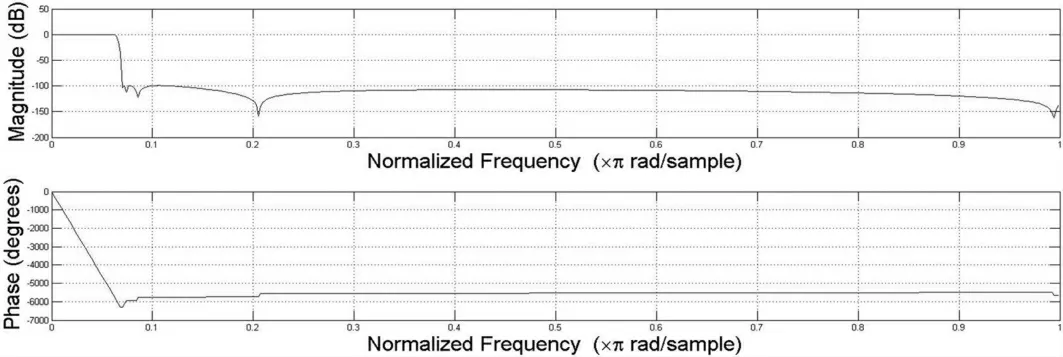

5.2 FIR 原型低通濾波器設計

多相濾波設計中的濾波器組的設計相當重要,這組低通濾波器是對原型低通濾波器進行移位抽取得到的。本方法采用無盲區的信道劃分方式,采樣率為96 MHz,信道數為16 個,每個信道帶寬是6 MHz。綜上所述,采用MATLAB 的Fdatool 設計完成[11]。FIR 濾波器的幅頻響應如圖7 所示。

圖7 FIR 濾波器的幅頻響應

5.3 FFT 設計

由于DFT本身需要做大量的蝶形運算,在FPGA 工程實現中采樣FFT 的IP 核來實現。每次送入16 個采樣點,處理完成后16 通道并行輸出,送后續的處理模塊完成高速跳頻信號的信號檢測和參數測量。

6 MATLAB 仿真及FPGA實現

6.1 MATLAB 仿真結果

利用MATLAB 針對高速跳頻信號的L 頻段的多相濾波設計方法完成仿真。設置當前ADRV9009 的AD1 通道接收頻率設置為f0,AD2 的通道接收頻率設置為f0+3,那么根據高速跳頻信號的頻點和帶寬的關系,兩個數字信道化處理模塊可將高速跳頻信號的L 頻段所有對應的跳頻點完全覆蓋。

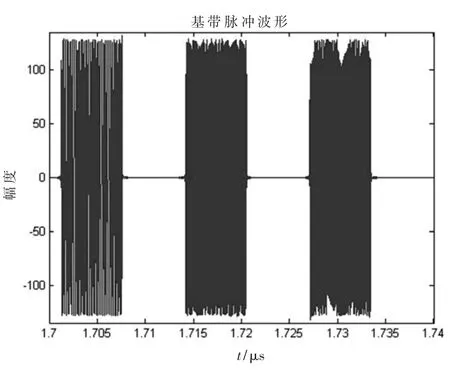

由于四個16 路的數字信道化結構完全相同,下邊以一個模塊的仿真來闡述。設置當前的高速跳頻信號的三個跳頻頻點分別為f0、f0+3、f0+6,則經過ADRV9009 后的輸出的基帶IQ 信號如圖8 所示。

圖8 三個不同跳頻頻點的脈沖波形

經過多相濾波處理后的波形如圖9 所示,由于經過多相濾波處理的信號為復信號,因此取復信號的模。

圖9 MATLAB 相應通道的輸出波形

由圖9 可見,一個通道只出現對應頻點的高脈沖信號,其他的通道信號幅度明顯降低,這和理論推導結果一致。

6.2 FPGA 仿真結果

6.2.1 FPGA 的仿真結果

圖10 是采用Modesim 對實現后的FPGA 算法完成仿真。由于MATLAB 信道的編號是從1 開始而FPGA 是從0開始,故其仿真結果和MATLAB 的仿真結果是一致的。

圖10 Modesim 的仿真結果

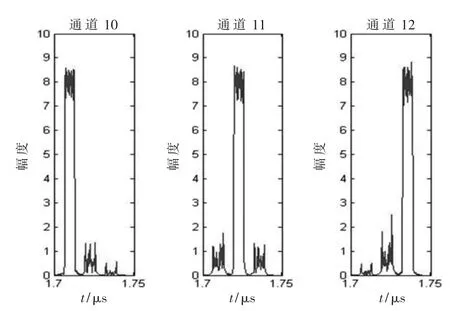

通過板級測試,其9、10、11 通道實測結果如圖11所示。由圖可見,9、10、11 通道信號的脈沖幅度顯著大于其他信道的脈沖幅度。工程實現后脈沖落入的信道和理論推導及MATLAB 仿真結果是完全一致的。

圖11 FPGA 在線實現結果

6.2.2 資源分析

FPGA 的乘法器(DSP)資源是最寶貴的硬件資源,實現乘法和其他的算術運算均需乘法器來完成。采用多相濾波體制每路的乘法器(DSP)是4 個,則總共需要512個DSP,加上FFT 變換的DSP 總共需要528 個乘法器就可完成該帶寬下高速跳頻信號的數字信道化處理。如果采用傳統的下變頻濾波的方式,每一路數字混頻濾波大概需要67 個DSP,則高速跳頻信號的51 個頻點總共需要3 417 個DSP,此時一片XC7Z045 的DSP 資源無法完成此工作。

7 結論

針對高速跳頻信號的偵察由于其信號帶寬寬、跳速快、編碼體制復雜,對接收機的設計及后端數字信號處理都是極大的考驗[7,12-13]。本文探討了針對高速跳頻信號接收的寬帶接收設計,結合當前高性能的射頻頻率捷變芯片,兩片ADRV9009 的四個接收通道可實現高速跳頻信號帶寬的全部覆蓋。該方法不僅簡化了前端射頻部分的功耗、體積,而且前端四路接收通道只需設置對應頻點即可。后端采用多相濾波的數字信道化技術,降低了數字信號處理的速度,節省了硬件資源,增強了系統的靈活性。該處理技術適應于不同帶寬的高速跳頻信號,而且針對其他非協作通信的寬帶信號依然有較大的優勢。