用于CMOS圖像傳感器的高速高精度斜坡ADC設計技術研究?

張 倩郭仲杰余寧梅吳龍勝

(1.西安音樂學院計算機教研室,陜西 西安710061;2.西安理工大學自動化與信息工程學院,陜西 西安710048;3.西安電子科技大學微電子學院,陜西 西安710065)

作為萬物互聯的傳感器網絡,圖像傳感器發揮著舉足輕重的作用。圖像傳感器分為CCD電荷耦合器件和CMOS圖像傳感器。早期由于工藝技術的原因,CCD器件占據絕對的市場比例。近二十年左右,CMOS工藝技術突飛猛進,加上CMOS圖像傳感器在集成度和低功耗等方面的絕對優勢,推進了CMOS圖像傳感器的快速發展。隨著大數據時代和5G時代的到來,電子成像系統對傳感器的速度、精度和集成度要求與日俱增,因此,近年來CMOS圖像傳感器的發展非常迅速[1-4]。

從目前大量的文獻研究成果來看[5-7],高速CMOS圖像傳感器基本上都采用全流水的工作方式,這樣影響傳感器速度的是每一級并行工作的電路。根據列級讀出電路的特點,并行工作的電路主要包括,像素單元的電荷轉移與采樣電路,列級ADC,并串轉換與數據輸出電路。對比這些電路,其中速度最難提升的是列級ADC。由于列級ADC在CMOS圖像傳感器中的特殊性,考慮到功耗和面積的雙重約束,一般采用的是單斜式結構,即斜坡ADC。斜坡ADC的組成單元包括采樣保持,比較器,計數器等關鍵模塊。對于n位分辨率的ADC,計數器的計數范圍為從0到2n-1個主時鐘,可見,斜坡ADC的速度隨著分辨率的提升急劇下降,這導致在高精度量化的應用中很難克服速度衰減問題。

因此,文獻[8-13]對單斜式結構進行了不斷的改進,其中共性的特點是都提出了兩步式的解決方案。很明顯,兩步式結構可以壓縮斜坡ADC的轉換時間,然而這里有個關鍵問題是,在兩步式的量化過程中,斜坡被分為多個分段區間的斜坡相疊加而成,這對斜坡間的無縫切換要求比較高,否則會存在各斜坡之間的非線性誤差。斜坡之間的切換很難做到無縫切換,總會存在一定的誤差,這使得該方法的精度受到一定的制約。文獻[11]對斜坡間的誤差進行了研究,提出了一種巧妙的解決方法,但是為了確保存儲電壓的精度需要增大斜坡電壓保持電容,這將會導致大陣列下斜坡驅動能力必須大大增加,造成芯片面積和功耗的巨大消耗。文獻[12]提出的兩步式相關多采樣方法雖然可以提高兩步式的轉換速度,但是對于低位的轉換仍存在子區間由于失調失配引起的銜接性問題。文獻[13]更是將兩步式單斜式改進為兩步式SAR與SS的合成,進一步壓縮了轉換時間,雖然第二步的子斜坡區間是實時產生的,但是斜坡間的失配問題依然存在。

針對上述分析的問題,本文基于兩步式架構的設計思想,以進一步提高兩步式的速度為目標,一方面將兩步式中的第一步前移到像素的采樣讀出階段,實現時間的共享,消除了兩步式中第一步消耗的時間。另一方面,通過第一步的處理,將第二步的斜坡下移到第一個斜坡區間,即實現單一區間的量化,避免了多斜坡之間的非線性問題。具體的設計方案與驗證結果如下所述。

1 基于時間共享與固定區間的高速高精度兩步式A/D轉換架構

傳統的單斜式ADC結構如圖1所示,其中AMP和電容C1,C2組成像素輸出的采樣與放大電路,放大倍數由C1和C2的比例決定,電容C3為保持電容。在單斜式ADC的量化階段,比較器CMP對保持的模擬電壓和斜坡電壓進行比較,同時在比較的過程沖同步計數,當比較器翻轉時的計數值即為量化的數字結果。正是由于這一過程的特點,其量化時間比較長。隨之改進的結構是圖2所示的兩步式結構,該結構可以將單斜式的時間消耗大幅壓縮。但是從圖3所示的兩步式多斜坡區間的關系可以看出,斜坡之間的無縫切換非常重要,它對線性誤差影響很大。

圖1 單斜式ADC結構

圖2 兩步式多斜坡ADC結構

圖3 兩步式斜坡間的關系

本文針對這一問題提出了一種有效的解決方案,如圖4所示。由AMP和電容C1,C2組成的像素輸出采樣放大電路與傳統結構一致,所不同的是,在本文提出的兩步式中,每一步的具體工作過程如下所述。其中VL到VH是列級ADC的模擬量化范圍,按照兩步式的工作過程,第一步量化M位,n=2M-1,第二部量化K位。

第一步,開關S1閉合,開關S2閉合至CMP1翻轉時刻,保持電容C3的下極板會根據像素輸出采樣放大的值動態切換,直至切換到預期的值。由于像素輸出與采樣放大的時間是一定的,所以將在這一段時間內,對正在建立的保持電壓VA進行從V1到Vn的比較,當VA超過V1時,保持電容C3的下極板接V1。當VA超過V2時,保持電容C3的下極板再切換到V2。當VA趨于穩定時,保持電容C3的下極板將固定到上一狀態保持不變。比較器的比較過程和電容C3下極板的變化過程是同時發生的,當比較器狀態發生變化后,此時電容下極板的開關將會斷開,此時電容下極板維持當前值。需要注意的是,電容上下極板變化的過程中互相不會有影響,這需要提高采樣放大的輸出驅動來保證。

第二步,這一步才是列級ADC真正消耗時間的部分。此時S1和S2均為斷開狀態,保持電容C3兩端的電壓差此時處于VL到V1之間,因此,將保持電容C3兩端的電壓差與VL到V1之間的固定斜坡進行類似于單斜式結構的比較,完成第二步的量化。

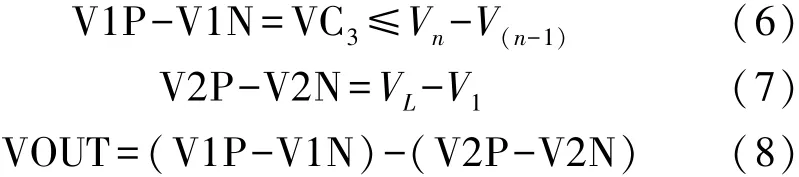

最后,將第一步的結果和第二步的結果相加,即得到最終的量化結果。以圖4中的VA為例,在采樣電路輸出過程中,同步查找VA所在的區間:

圖4 本文提出的兩步式結構與時序關系圖

在細量化區間,針對式(1)中的ΔV,通過四輸入比較器直接得到單一區間的斜坡比較,即ΔV在式(3)中進行比較量化,最終通過對m和k進行譯碼實現M+K位的高精度量化結果。

從上面推導可以得到,列級采樣保持結束后,電容C3兩端的壓差時鐘VC3,對應比較器的V1P和V1N輸入端,比較器的另外一組輸入端V2P和V2N對應固定的斜坡信號,保證了V1到VH的任意一點信號都可以被快速且單一區間量化。

根據上述分析可以看出,本文提出的方法具有以下優勢:①利用列級采樣過程的時間,并行完成了粗量化的工作,為兩步式A/D轉換節省了大量時間;②保持電容C3的下極板電壓不會發生類似傳統結構的電壓突變,從而降低電容對切換速度的制約;③細量化階段的電壓比較始終采用單斜坡實現,而且沒有引入余量增益與做差電路,從而提升了粗細量化的斜街,避免了傳統兩步式的切換誤差問題。利用本文提出的方法可以在提高兩步式A/D轉換速度的同時,也改進了粗細量化的轉換精度,為高動態范圍的CMOS圖像傳感器提供了有效的解決方案。

2 實驗結果與數據分析

為了驗證所提出方法在實際芯片中的可行性,論文在一款基于55 nm 1P4M工藝的2 048×2 048規模CMOS圖像傳感器設計中對上述提出的改進方法進行了具體電路的詳細設計與測試驗證。設計輸入為2 048列像素輸出列線的模擬信號,量化范圍為1.2 V到2.8 V。該設計的分辨率為12位,計數器時鐘頻率為500 MHz,其中第一步量化4位,時間長度為0.5μs,第二步量化8位,時間長度為0.5μs。具體在電路實現中的表現是,在像素輸出與列級采樣的過程中,對采樣保持建立過程中的信號最多進行24-1次比較,根據比較的結果確定開關S2<1∶24-1>的編碼方式,從而確定保持電容C3的下極板所接電位。同時輸出比較器最后一次翻轉對應的電位作為最后加法器的輸入。在第二步的量化中,斜坡范圍為1.2 V到1.3 V,計數器的范圍為0到255,比較器翻轉時對應的計數器值為底8位的量化結果。最后將兩步的量化結果拼接相加得到12位數字信號的完整輸出。

如圖5所示為電路內部詳細的設計原理。其中虛線框中的電路為列級電路,共有2 048列,V1到Vn的參考電壓信號和VL到V1的固定斜坡信號由芯片級共用電路提供。由于電容C3的下極板會根據VA上升的幅度呈臺階上升,最終當VA穩定時,C3的兩端電壓差處于V1-VL之間,這樣就可以將所有信號下移到V1-VL之間。對于V1到Vn的參考電壓信號,由于是直流信號,可以很好的保證列級之間的一致性。而對于VL到V1的固定斜坡信號,由于是受時間約束的瞬態信號,在版圖布局時,需要充分考慮列級金屬走線引入的布局差異,通過反補償的方式抵消列級之間的差異,同時,在時間允許的情況下,也可以考慮采用數字相關雙采樣技術予以消除。如圖6所示為考慮像素規格尺寸的列級版圖設計,實際設計列寬為7.5μm,為了提升電路在有限列寬下的抗干擾程度,關鍵的參考信號、斜坡信號、電源地信號走線均采用了提升驅動能力與隔離的措施。

圖5 兩步單斜ADC電路在列級的并行實現

圖6 本文提出的兩步單斜ADC電路與版圖實現

通過將量化后的數字信號與模擬輸入信號進行比對后發現,論文所提出的方法實現了高速與高精度的目標,圖7所示為光電轉換實際輸出曲線,圖8所示為DNL和INL的實際仿真驗證曲線,其中DNL的最大值為0.12LSB,INL的最大值為0.08LSB,這一優秀的線性誤差參數將為高端CMOS圖像傳感器提供良好的支持。表1列出了本文驗證結果與相關文獻的對比,可見,本文工作采用時間共享后,將行時間壓縮到500 ns,提高了CMOS圖像傳感器的幀頻。采用固定區間的細量化后,DNL和INL質保均表現良好,顯示了一定的線性優勢。除此之外,論文在功耗和噪聲方面,也沒有任何犧牲。

表1 本文研究成果與參考文獻的對比

圖7 光電轉換實際輸出曲線

圖8 DNL和INL的驗證對比曲線

3 結論

本文針對單斜式ADC的速度有限缺點和兩步式多斜式ADC的線性誤差缺點,提出了一種基于時間共享和單區間斜率的高速高精度兩步式ADC結構。采用第一步與像素輸出采樣并行的方式,進一步提高了兩步式ADC的速度。采用電容頂極板電壓切換技術,將兩步式的多斜式轉換為單個固定的斜坡,解決了多斜坡之間的線性誤差問題。該方法在一款基于55 nm 1P4M工藝的2 048×2 048規模CMOS圖像傳感器中進行了實際驗證,結果表明,行時間可以加快到500 ns的同時,非線性誤差控制在0.12LSB以內,為高端CMOS圖像傳感器的設計提供了有效的解決方案。