一種集成無源電容式高硅鋁合金基微波功率芯片載體技術

劉米豐,任衛朋,趙 越,陳 韜,王盈瑩

(上海航天電子通訊設備研究所,上海 201109)

以微波收發組件為核心的有源相控陣雷達具有快速掃描、數字波束形成以及空間功率合成等優點,可同時完成預警、跟蹤制導和火力控制等多種功能,具有非常強的多目標處理能力,是現代作戰體系依賴的先進設備[1-4]。

作為微波收發組件的核心器件之一,微波功放芯片的作用是將低功率的射頻信號放大成高功率的射頻信號,直接決定了雷達的最大探測距離和抗干擾等關鍵性能。由于微波功放芯片在工作過程中會產生大量的熱量,需要及時、高效地將熱量導出,否則會出現芯片失效、燒毀等現象。同時,微波功放芯片與微波組件殼體材料的熱膨脹系數(CTE)不一致,需要在兩者之間設置過渡結構,從而降低熱應力對微波功放芯片的沖擊,提高微波組件的可靠性[5-7]。

高硅鋁合金材料因具有高導熱、低CTE、低成本以及可加工性高等優點,可滿足微波功放芯片對芯片載體的要求[8-11]。因此,本文提出了一種基于高硅鋁合金基底的一體化集成功率芯片載體,其主要特點是在高硅鋁合金基板上集成了含薄膜電容和導線的內匹配電路,可減少后續芯片電容貼裝工序,提高微波組件的生產效率與可靠性。

1 高硅鋁合金基薄膜電容制備

1.1 高硅鋁合金基板表面前處理

一體化集成芯片載體的薄膜電容結構要求高硅鋁合金襯底表面平整、光滑且不能有裂紋等缺陷,否則就無法在襯底表面形成致密、無缺陷的薄膜電容介質層,并導致電容短路、擊穿電壓降低以及漏電流增加等問題。此外,一體化芯片載體的焊接膜層粗糙度也與高硅鋁合金襯底表面粗糙度相關,而低粗糙度的焊接膜層是實現高質量、低空洞率共晶焊接的關鍵因素之一。因此,首先需要采用高硅鋁合金表面處理技術,以獲得具有無裂紋、平坦化的高硅鋁合金基板表面。

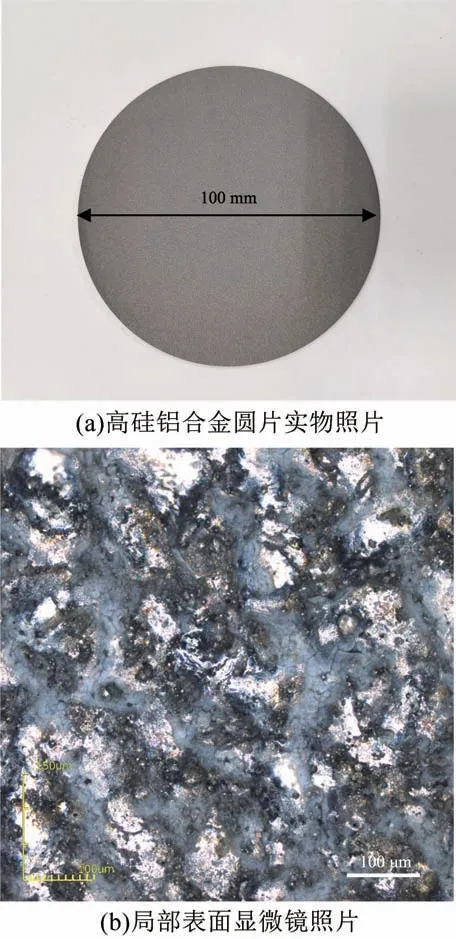

采用機械加工方式將高硅鋁合金塊材加工成直徑100 mm、厚度1.2 mm 的高硅鋁合金(70Si30Al,CTE=7)圓片,利用光學數碼顯微鏡(Olympus OLS4100)對高硅鋁合金圓片表面進行三維建模,得到檢測結果如圖1 所示,其表面存在大量的瘤狀物,粗糙度也高達2.917 μm。

圖1 高硅鋁合金圓片初始表面形貌Fig.1 Initial morphology of high Si-Al alloy wafer

由于高硅鋁合金圓片表面的瘤狀物尺寸在幾十微米以上,因此先采用機械研磨方法將基板表面的瘤狀物研磨去除,再采用化學機械拋光(Chemical Mechanical Polishing,CMP)技術將表面粗糙度降至納米級。此外,由于高硅鋁合金圓片存在鋁與硅晶胞混合的復雜表面,要求CMP 拋光液能同時對鋁和硅起化學反應。因此,選擇Logitech 公司的SF6 型堿性溶液作為高硅鋁合金圓片的拋光液,該拋光液主體成分是納米級的硅溶膠、無機堿、絡合劑以及螯合劑,并通過用去離子水對原液進行稀釋,將拋光液pH 值調節至8 左右。

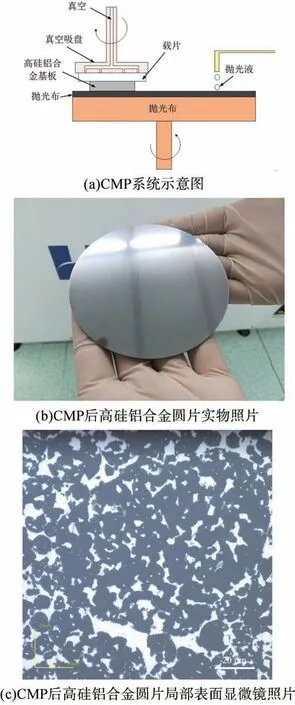

圖2(a)所示為Logitech 公司的PM5 型CMP 系統,該系統由真空吸盤、拋光盤和拋光液三個主要部分構成。將研磨后高硅鋁合金圓片用石蠟粘貼到直徑100 mm 的玻璃圓片正面,然后利用真空將玻璃圓片背面吸附到減薄拋光機的真空吸盤上,并將上轉盤倒置到拋光盤上,就可實現高硅鋁合金圓片的研磨加工。設置拋光盤轉速為70 r/min,真空吸盤上施加6 kg 的壓塊,設置拋光時間為1 h。完成CMP 后,通過光學數碼顯微對拋光后的高硅鋁合金圓片進行三維建模,可得高硅鋁合金圓片的表面粗糙度降低至23 nm,滿足后續薄膜加工需求,如圖2(b)和(c)所示。

圖2 高硅鋁合金圓片表面平坦化Fig.2 Surface planarization of high Si-Al alloy wafer

1.2 Ta2O5-Al2O3混合介質層薄膜電容制備

薄膜電容的比容量與電極相對面積、介質材料介電常數以及介質層厚度相關。而增大薄膜電容面積則會導致一體化芯片載體面積增大,進而對微波組件的高密度集成和低成本形成不利影響。因此,為了獲得更大比容量的薄膜電容,只能增加薄膜電容的介質層厚度或者選擇更大介電常數的介質材料。相比于常規的SiO2材質介質層,薄膜形態Ta2O5的相對介電常數可達到18~28,是SiO2薄膜的6~8 倍[12-17]。此外,由于Ta2O5具有良好的熱、化學穩定性,因此選擇其作為功率芯片一體化集成載體的薄膜電容的介質層。

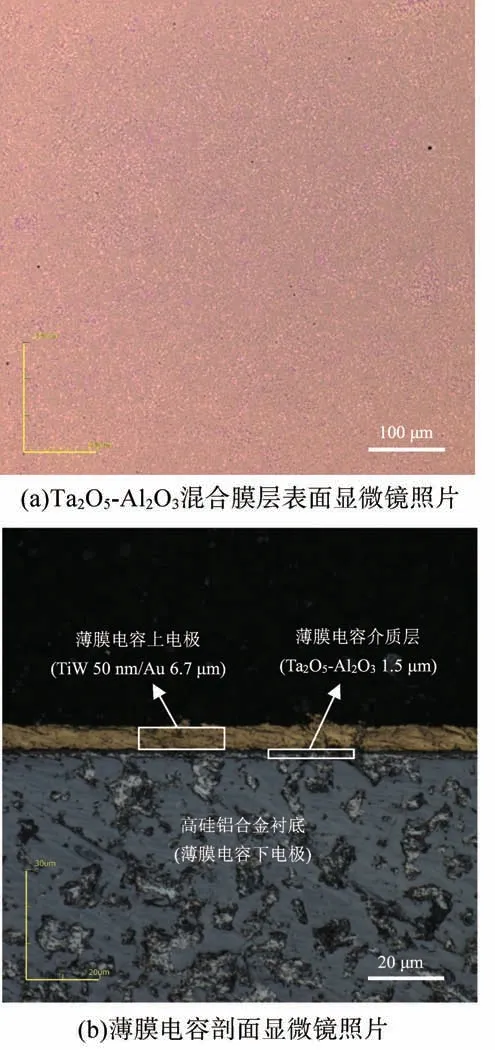

在高硅鋁合金基板表面制備Ta2O5膜層時需要考慮與Ta2O5與鋁硅界面的結合力。為此,采用美國丹頓DISCOVERY 635 磁控濺射儀器在高硅鋁合金基板表面濺射一層Ta-Al 混合薄膜層,具體制備工藝參數為:Ta 靶功率為400 W、時間4000 s,Al 靶功率為400 W、時間1000 s。通過臺階儀(KLA Tencor ASIQ3) 對Ta-Al 混合膜層厚度進行測量,測試結果為1.5 μm。然后,將高硅鋁合金基板放入質量分數0.1%的檸檬酸溶液中進行陽極氧化,氧化電壓為200 V,溶液溫度低于10 ℃,氧化時間為20 min,陽極氧化完成后用去離子水沖洗10 min 并氮氣吹干。圖3(a)為Ta-Al 混合膜層陽極氧化后的顯微鏡照片,采用萬用表對該膜層進行電測試,測試結果表明接觸膜層的表筆與接觸基板背面的表筆之間為絕緣,由此得到該混合膜層已經被陽極氧化成Ta2O5-Al2O3混合膜層。在Ta2O5-Al2O3混合膜層表面通過磁控濺射TiW(50 nm)/Au(100 nm)種子層并采用電鍍將Au 膜層加厚至6 μm以上,形成薄膜電容上電極,從而實現高硅鋁合金基薄膜電容的制備,如圖3(b)所示。通過半導體參數分析儀(Keysight B1500A),采用4 端對(4TP)測量方法對薄膜電容的比容量進行測試,測試結果約為7 μF/mm2。

圖3 高硅鋁合金基薄膜電容Fig.3 Film capacitance based on high Si-Al alloy substrate

2 一體化集成功率芯片載體制備

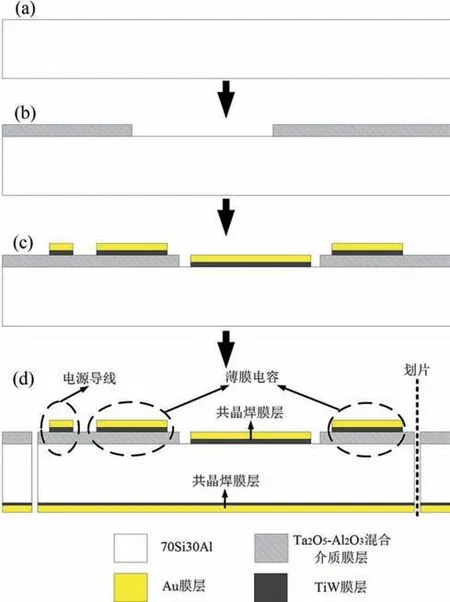

在高硅鋁合金基薄膜電容制備技術基礎上,開發了一體化集成功率芯片載體制備的工藝流程,具體如下:

(1)對線切割后的高硅鋁合金基板表面進行研磨和CMP 處理,完成后用丙酮超聲清洗將基板表面的石蠟去除干凈,然后用去離子水沖洗并用氮氣吹干,如圖4(a)所示;

(2)在表面處理后的高硅鋁合金上表面通過磁控濺射沉積一層厚度為1.5 μm 的Ta 和Al 混合膜層,然后在質量分數0.1%、10 ℃的檸檬酸溶液內進行200 V的陽極氧化20 min,將Ta-Al 混合膜層氧化成Ta2O5-Al2O3混合膜層,通過光刻技術在基板的薄膜電容區域覆蓋上光刻膠,然后浸入HF 溶液(HF 與H2O 質量比為1 ∶50)中4~6 min,去除薄膜電容區域外的混合介質層,如圖4(b)所示;

(3)在完成薄膜電容介質層制備的基板上,表面采用磁控濺射一層TiW/Au(50 nm/200 nm)種子層,然后采用圖形電鍍技術將薄膜電容電極、焊接膜層和導線的金層加厚至6.7 μm,最后將光刻膠掩膜和TiW/Au 種子層去除,便可同時形成薄膜電容電極、焊接膜層和導線結構,如圖4(c)所示;

(4)最后在基板背面通過磁控濺射和電鍍形成一層TiW/Au(50 nm/2 μm)膜層作為下表面的焊接膜層,并通過劃片完成功率芯片一體化集成載體的制備,如圖4(d)所示。

圖4 一體化集成芯片載體制備工藝流程Fig.4 Process of the integrated chip carrier

按照上述工藝流程,完成微波組件的一體化集成功率芯片載體制備,實物照片如圖5 所示,單個載體內部含有8 個集成薄膜電容和一個導線。

圖5 一體化集成功率芯片載體樣品實物Fig.5 The integrated power chip carrier samples

根據功率芯片對匹配電容的要求,要求每個薄膜電容的電容值在50~100 pF 范圍內,且其中3 個薄膜電容需進行并聯。采用萬用表測得3 個并聯電容的容值約為187 pF,獨立電容的容值約為70 pF,滿足功率芯片的外圍電路匹配要求。

3 應用與討論

3.1 微波組件應用

先利用自動共晶焊接技術將GaAs 功率芯片焊接到一體化集成功率載體的焊接區域上。然后通過金絲引線鍵合技術實現功率芯片與內匹配電路的電互連,完成T/R-MMICs 模塊制備。最后將整個TR-MMICs模塊通過焊料焊接方式裝配到組件殼體中,并利用金絲鍵合將其與微波組件基板、環隔器等進行互連,完成某型號雙通道微波發射組件制備,如圖6 所示。

圖6 基于一體化功率芯片載體的雙通道微波組件實物Fig.6 Double-channel microwave module based on integrated power chip carrier

3.2 性能測試

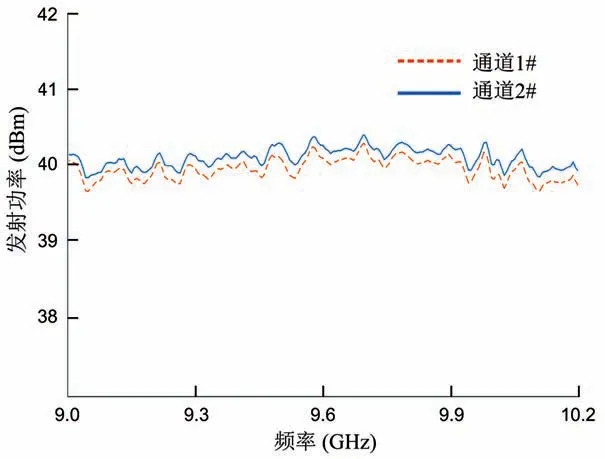

采用射頻功率計(BOONTON 4500B)對微波組件發射功率進行測試,測試結果如圖7 所示,在9~10.2 GHz 頻率范圍內,通道1#的發射功率大于39.473 dBm(約9.8 W),通道2#的發射功率大于39.801 dBm(約9.6 W),滿足組件設計要求。

圖7 微波組件發射功率測試結果Fig.7 Transmission power test result of microwave module

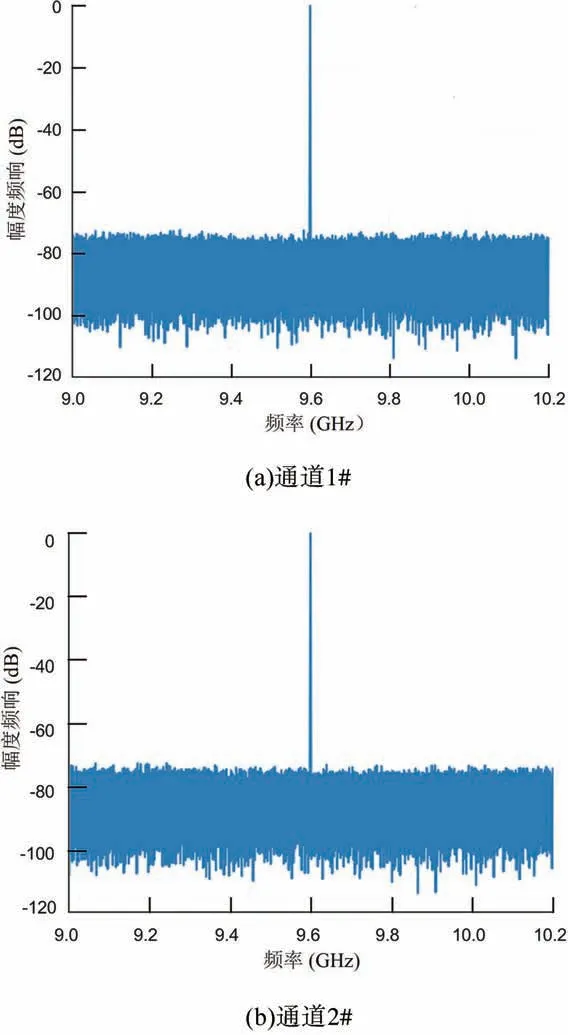

采用射頻功率計(Agilent E4440A)對微波組件雜散抑制進行測試,測試結果如圖8 所示。由圖8 可知,在9~10.2 GHz 頻率范圍內,通道1#雜散抑制約為-76.24 dB,通道2#雜散抑制約為-75.09 dB,滿足組件設計要求。

圖8 微波組件雜散抑制測試結果Fig.8 Spurious suppression test result of microwave module

4 結論

通過CMP 技術實現了表面粗糙度為23 nm 的高硅鋁合金圓片制備;利用磁控濺射和陽極氧化技術在高硅鋁合金表面實現了厚度1.5 μm 的Ta2O5-Al2O3混合膜層的制備;基于Ta2O5-Al2O3混合介質層的薄膜電容的比容量約為7 μF/mm2。

制備了基于高硅鋁合金基板的一體化集成功率芯片載體,集成了薄膜電容和導線的內匹配電路,單個薄膜電容的電容值約為70 pF。將一體化集成功率芯片載體應用到了某型號的雙通道微波發射組件中,發射功率的測試結果為9.8 W(通道1#)/9.6 W(通道2#),雜散抑制的測試結果為-76.24 dB(通道1#)/ -75.09 dB(通道2#),測試結果滿足設計指標要求。

由于高硅鋁合金基一體化集成功率芯片載體不僅可以減少微波組件組裝步驟,而且能提高集成密度,同時自身還具備批量化制造優勢,因此該技術在高功率微波組件中的應用前景十分廣闊。