DMSA 在時序簽核中的應用*

孫 恒,王仁平,蔡沅坤

(福州大學 物理與信息工程學院,福建 福州 350000)

0 引言

隨著集成電路產業不斷發展,芯片制造早已進入深亞微米時代,一直以來,時序簽核一直是檢驗芯片設計是否合格的重要標準之一,在綜合工具(Design Compiler,DC)、布局布線工具(Integrated Circuit Compiler,ICC)、時序分析工具(Prime Time,PT)中都嵌入了不同的時序分析引擎。當工藝節點達到90 nm 及以下時,為了使芯片在不同的極端環境下可以正常工作,就需要采用多工藝角多模式的物理設計方案來確保芯片在不同環境下穩定工作[1-3]。在對多場景物理設計進行時序分析時,傳統PT 需要打開多個窗口反復切換場景以達到遍歷每一個場景的目的,隨后逐個場景進行時序分析,這樣會使設計過程變得過于繁瑣,而且,對于同一路徑,不同場景下的時序違規可能會重復出現,對時序分析帶來不必要的麻煩[4],工藝角或模式的合并,也會帶來各種各樣的問題,DMSA 的使用可以很好地解決這些問題。

1 靜態時序分析原理

DMSA 是STA 的一種特殊模式,其原理和STA 原理如出一轍。STA 是通過“窮舉法”抽取整個電路的時序路徑,計算時序路徑的傳播延時,檢查信號是否滿足時序約束要求,其目的是保證所有路徑滿足內部時序對建立時間(Setup time)和保持時間(Hold time)的要求,從而實現時序簽核[5]。

STA 的實現主要分為三個步驟:(1)時序路徑的劃分,如圖1 所示,STA 在時序分析時一般將電路分為四種時序路徑[6]。(2)路徑延時的計算,靜態時序分析的路徑延時(Path delay)分為單元延時(Cell delay)和線延時(Net delay)。單元延遲多采用非線性延時模型(Nonlinear delay model),即用二維查找表進行單元延時計算,兩輸入變量分別為輸入轉換時間(Input transition time)和輸出負載(Output load),同樣,線延時的計算通過ICC 中實際繞線情況,由Start-RC 抽取寄生參數值,根據特定的線延時模型進行估算[7]。(3)路徑時序的檢測,就時序路徑而言,需要通過延時計算得到路徑的數據要求時間(Data required time)和數據到達時間(Data arrival time),然后通過比較數據要求時間和數據到達時間來判斷路徑是否存在時序違規問題[8-10]。

圖1 物理設計中時序路徑劃分

2 DMSA 的應用

DMSA 是靜態時序分析的一種特殊模式,通過啟動主進程(Master)來充當所有場景的管理者角色,主進程是運行在DMSA 模式里的特殊進程,可以向從進程(Slave)遠程分配服務器資源和任務,實現通過單個端口對所有的場景進行時序分析的目的[11-12]。

2.1 DMSA 使用過程

在DMSA 的使用過程中,需要對三個關鍵變量進行設置,確保時序分析準確、高效的進行。

(1)許可證數目。在DMSA 模式下進行時序分析時,主服務器(Master)需要分配一定數量的許可證(license)給從服務器(Slave)使用,沒有許可證的從進程不能進行工作,使用“set_multi_scenario_license_limit”命令可以對許可證的數量進行設置,默認情況下,主服務器會最大程度地分配許可證給從進程,如果設置的從進程的數量多于許可證的數量時,沒有許可證的從進程需要等其他從進程任務完成后,分配到許可證才可以進行工作。

9月的加州依然很熱,洛杉磯周邊的山路其實也不乏駕駛樂趣,但必須承認,林肯在中大型全能豪華SUV市場的最新成果很擅長營造輕松的駕乘體驗。V6發動機的動力表現從容不迫,8速自動變速箱升擋時也懂得回應平順,轉向輕巧而柔和。據說CCD連續可調阻尼懸架在行駛中能以每秒約23000次的頻率掃描路面,盡可能根據路面情況過濾掉多余的顛簸,面對粗糙鋪裝路面時給我的路感反饋甚至比全新林肯領航員Navigator還要得體一些。前后車窗配置的聲學夾層玻璃,車輛底部與油箱加厚的吸音材質,配合ANC主動降噪系統,車內靜音表現值得肯定。

(2)從進程的數量。根據場景的數量,在主服務器通過“set_host_option -max_core -num_processes”命令對core數目、啟動進程數目進行設置,一般情況下,場景的數目要小于等于從進程的數目,確保每一個場景都有一個專用的從進程,保證DMSA 順利進行。

(3)場景的定義。DMSA 中場景的定義分為兩種:(1)每一個場景都由一個腳本定義,通過命令“create_scenario-name ${mode}_${corner} -specific_variables {mode corner} -specific_data {pt_setup.tcl}”主服務器將變量工作模式、工藝角組合分配到從服務器并執行帶有變量工作模式、工藝角的腳本pt_setup.tcl。(2)時序分析使用“save_session”命令后,可通過“create_scenario -name -image”指定之前保存過的場景。許可證、從進程、場景三個變量的設置是DMSA 設計方法能否并行運行的關鍵,需根據待分析芯片的物理設計進行正確的配置[13]。

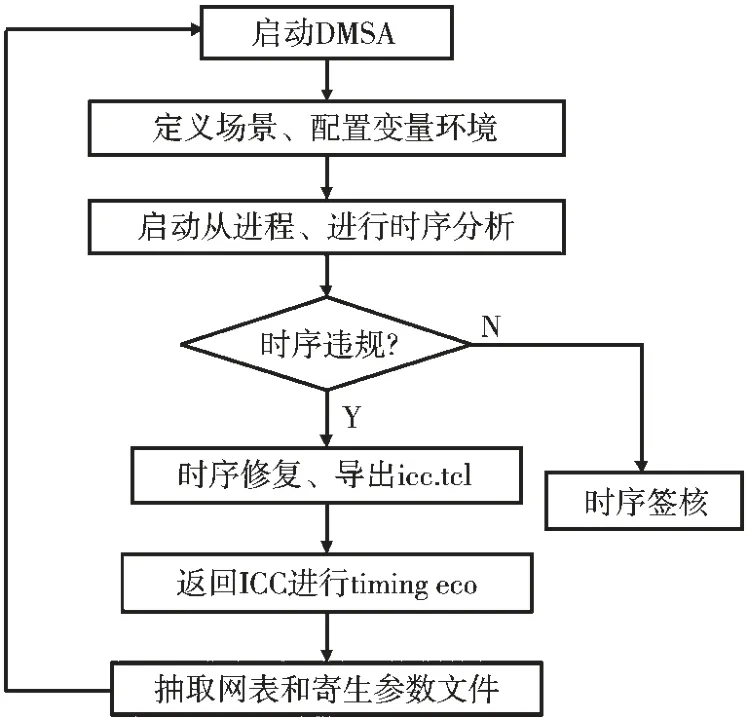

2.2 DMSA 時序修復流程

芯片在流片(Tapeout)之前,要滿足時序約束和物理規則等要求,為了進行更精確的時序分析,需要將ICC生成的網表以及提取的寄生參數文件導入PT 進行時序分析[14],對于多場景的物理設計,采用DMSA 設計方法,通過在terminal 中輸入“pt_shell -multi_scenario”便可進入DMSA 模式。然后配置好相關路徑和服務器資源,通過“create_scenario”命令進行場景創建,并將數據傳遞到每一個從進程中,使用“start_hosts”命令來啟動所有從進程,完成環境配置之后“report_constraints-all_violators”命令可以查看合并后各場景下的時序違規,然后使用“fix_eco_timing”命令進行時序修復,待時序修復完成,用命令“write_changes-format icctcl-output icc.tcl”生成時序修復后的工具命令語言(Tool Command Language,TCL)腳本,返回到ICC 中進行時序修復,再提取優化后網表和寄生參數文件重新到DMSA 中進行時序分析,循環往復,直到實現時序簽核[15]。DMSA 時序修復流程如圖2所示。

圖2 DMSA 時序修復流程

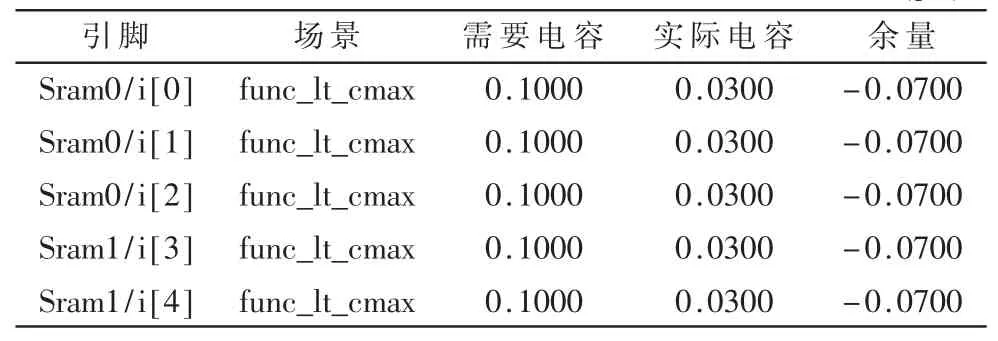

3 DMSA 在Cxdp13 芯片上的實現

本次實驗基于Smic 90 nm 工藝庫,待測試芯片Cxdp13設有2 種模式,8 個工藝角,共有16 個場景。在硬件配置方面共設置16 個進程,對應16 個場景。時序分析時,主進程將所有從進程中的時序信息整合篩選寫入到一個文檔報告中,自動過濾掉過多的重復路徑,而不需要針對每一個場景進行時序分析,這樣PT 在做時序修復時會顧及所有工藝角、模式的影響,可以有效減少各場景間的相互影響[16]。通過使用“fix_eco_timing -type hold-method{size_cell insert_buffer}-buffer_list $buf_list”命令和”fix_eco_timing -type setup -method{size_cell}”命令進行時序違規的自動修復,經過第三次迭代后,所有場景中時序違規全部修復完成。表1 是時序修復后通過“report_constraints”得到的所有時序和設計規則檢查(Design Rule Check)違規,因為macro 端口后面沒有連接負載,所以出現最小電容(Min_Capacitance)違規,此違規可以忽略。

表1 時序與設計規則檢查違規 (pF)

4 結論

本文介紹了DMSA 技術在MCMM 物理設計中時序簽核的應用,并利用Cxdp13 芯片設計實例闡述DMSA 技術的實現過程。實踐結果表明,DMSA 模式下時序分析與修復可以并行進行,時序修復過程中也會考慮其他場景的需要并且不需要進行多窗口切換,提高了時序分析的效率,也大大縮減了時序修復的時間。另外,隨著科技的發展,普通計算機的硬件條件也足以支撐DMSA 技術的實現。因此,在如今的MCMM 物理設計中,DMSA 技術在時序簽核中得到了廣泛的應用。