龍芯3A4000 主板VGA 接口電路設計及研究*

籍明慧,裴煥斗,宮健,張川川,莊杰

(1.中北大學 儀器與電子學院,山西 太原 030051;2.山西百信信息技術有限公司,山西 太原 030006)

0 引言

隨著電子產業的快速發展,視頻接口技術也從早期的BNC、S-端子、VGA 等接口發展到如今的DVI、HDMI以及DP 等數字視頻接口[1],有了長足的進步。但是在視頻數字化的潮流中,VGA 仍以成熟的技術優勢、良好的兼容性和通用性以及相比之下較低的成本被廣泛應用,是主板、嵌入式設備及高端顯示器等設備上最主要的接口。同時VGA 接口對于那些需要模擬信號進行顯示的機器是不可替代的,在技術產品革新替代中有著重要的作用。在針對國產化CPU 龍芯3A4000 進行主板開發時,面向國產機器替代,逐步實現國產化的要求,VGA接口的設計成為其中重要的一環。陳鍇然[2]對不同視頻傳輸標準的傳輸方式與優劣進行了分析對比,簡要介紹了各種視頻傳輸標準的應用場景;陳桂、朱麗婷、付宗寶及鄭佃好[3-6]等人基于幾種ARM 芯片控制ADV7120、ADV7125和THS8134B 等高性能視頻D/A 轉換芯片將LCD 掃描式接口轉換為了VGA 接口,具體介紹了其電路設計。筆者在開發基于龍芯3A4000(MIPS 架構)的通用主板的過程中,提出一種利用高性能視頻D/A 轉換芯片ADV7125將DVO 總線數字信號轉換為模擬信號通過VGA 接口實現視頻輸出的電路設計方法,該設計電路簡單可靠,且有較好的防護性和信號質量。本文將詳細介紹設計中的結構思路、電路設計及測試結果。

1 VGA 接口

1.1 簡介及原理

VGA 是IBM 于1987 年提出的一個使用模擬信號的電腦顯示標準[7],標準定義了VGA 信號外部接口互連的電氣特性標稱值、機械配接要求以及其信號傳輸原理(時序規范)。顧名思義,VGA 接口就是用來專門針對于VGA 標準輸出數據的接口,具有多分辯率模式、模擬信號輸出、數據傳輸速度快等優點,以其良好的兼容性、成熟性、可靠性被廣泛應用于視頻顯示領域。

在進行視頻顯示時,第一步系統內部首先將視頻信息解碼為數字型圖像信息緩沖至顯存芯片中,然后高性能視頻D/A 芯片調用數字視頻信號經過模擬調制成為R、G、B 三原色模擬數據信號和行(HSYNC)、場(VSYNC)同步控制信號,最后信號遵循VGA 時序通過VGA 接口傳輸到顯示設備中,其中行、場同步信號的作用是處理輸入模擬信號以及聯合起來控制VGA 的顯示時序。由VGA 顯示工業標準可知,VGA 的顯示時序在不同顯示模式和刷新頻率下,各個模式行、場時序圖輪廓基本一致,都由同步脈沖、顯示后沿、顯示時序段和顯示前沿組成,只是每一段時序的狀態持續時間不同。

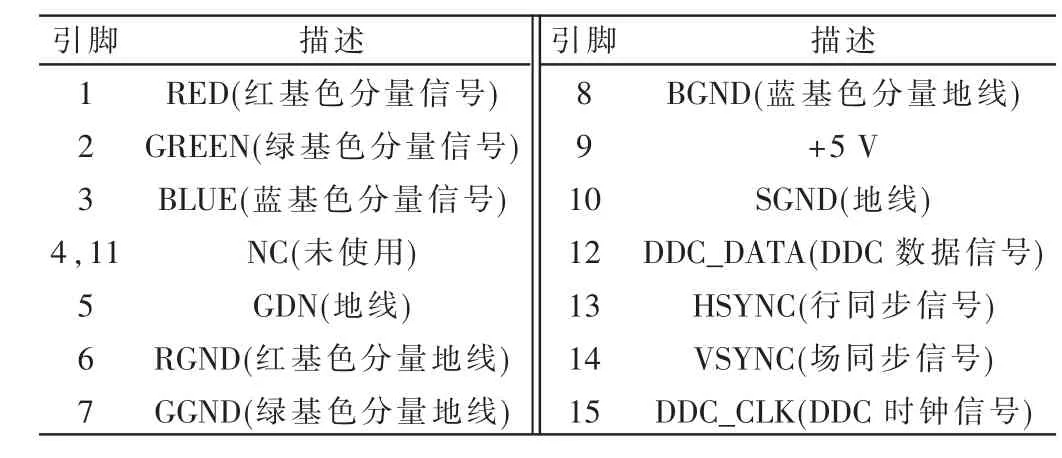

1.2 VGA 接口引腳定義

VGA 接口的物理外形是一個15 針孔的插座,分為三排,每排五個針孔。其傳輸信號主要有以下幾種類型:

(1)模擬數據信號:紅、綠、藍3 基色RGB 信號;

(2)同步控制信號:行/場同步信號(H/VSYNC);

(3)電源、地:1 個通用地,3 個對應彩色分量信號地,一個對應控制信號地,一個+5 V 電源。

其中行場同步信號(HSYNC、VSYNC)用來處理3 根RGB 彩色分量信號,同時配合起來控制VGA 的顯示時序,當工作在不同模式時,行同步信號和場同步信號的波形也各不相同。VGA 接口引腳定義見表1。

表1 VGA 接口引腳定義

1.3 VGA 接口時序要求

前文提到,VGA 的顯示時序是由行、場同步信號配合控制的。針對不同顯示模式和刷新頻率,VGA 接口的時序也有不同表現方式,但是其行場時序結構都是一致的,均由同步脈沖、顯示后沿、顯示時序段和顯示前沿組成,只是其不同狀態占用時間不同。圖1 為VGA 的信號時序圖。

如圖1 所示,行、場同步信號在每行/幀開始的時候均產生一個的低脈沖信號,且對應的同步脈沖均為負脈沖,在難以分辨不同模式下同步脈沖的周期時,會將其反相處理到達區分效果[8]。

圖1 VGA 信號時序

VGA 時序包括行、場掃描時序兩個部分,其時序參數有四個部分:行(場)同步脈沖(tWH,tWV)、顯示后沿(tHC,tHV)、有效顯示區寬度(tHSYNC,tVSYNC)、顯示前沿(tVH,tCH)。開始掃描時,第一步進行的是行同步操作,同步操作完成后開始真正的數據掃描工作[9]。TVSYNC 是完成一幀掃描所需要的時間,稱為場掃描周期,其倒數被稱為場頻,又稱刷新頻率;行掃描時序與場掃描時序的結構是一致的,此處不再細說。其中各個狀態所占用時間可通過刷新頻率即場頻得出,場掃描周期即為場頻的倒數,行掃描周期則通過場掃描周期和所掃描行數計算得知。

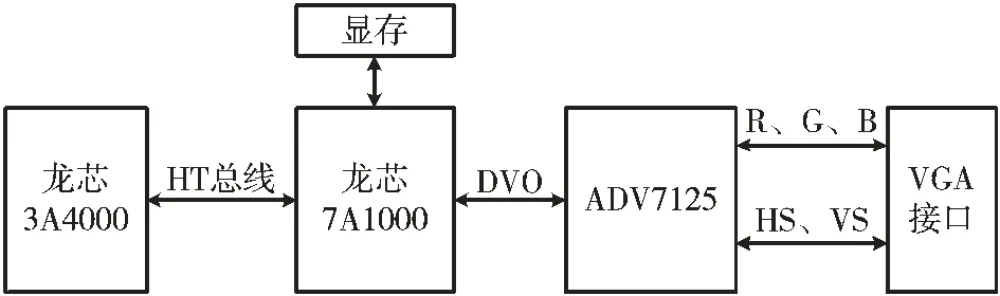

2 接口功能實現整體結構

本文基于龍芯3A4000 CPU 的開發背景下進行VGA接口設計,整體采用龍芯3A4000+7A1000 的架構,通過龍芯7A1000 橋片(后文簡稱橋片)擴展顯存以及VGA接口,利用高性能視頻D/A 轉換芯片ADV7125 將DVO 數字信號轉換為模擬信號進行視頻顯示。整體結構如圖2所示。

圖2 整體結構框圖

龍芯3A4000 是龍芯3 號系列處理器中首款基于GS464v 微架構的四核處理器,采用28 nm FD-SOI 工藝,主頻穩定工作在1.5 GHz~2.0 GHz,其性能與龍芯3A3000相比提升達一倍左右[10]。橋片與龍芯3A4000 之間通過HT 高速總線相連,內部集成2D/3D GPU(100~500 MHz)、顯示控制器以及顯存接口,同時集成PCIE 以及USB、I2C、SPI 等多個高低速接口。

本次設計主要依托于橋片內部集成的顯示控制器接口,橋片顯示控制器支持雙路DVO 顯示,每路最大支持1 920×1 080@60Hz,支持RGB444、RGB555、RGB565、RGB888四種色深。橋片顯示控制器提供了數據傳輸引腳和時序控制引腳,包括行場同步信號DVO_HSYNC/VSYNC 以及24 位數字數據信號DVO_D[23:0],其主要負責圖像數據處理、VGA 接口時序實現以及配置芯片ADV7125 的工作模式,并把處理后的幀數據以點為單位送SDRAM 顯示存儲器。進行視頻顯示時,調用顯存中圖像數據經橋片處理后傳輸至D/A 芯片ADV7125 進行模數轉換,最后模擬圖像信號遵循VGA 時序通過VGA 接口傳輸到顯示設備中。此次設計采用單片2 Gb×16 bit 的SUMSUNG公司的DDR3 SDRAM 芯片K4B2G1646Q-BCK0 作為顯示存儲器,可以滿足高速數據收發存儲的功能需求。

根據橋片設計手冊規定,VGA 接口的同步信號需要由橋片顯示控制器提供,故利用ADV7125 可以方便地將橋片的DVO 接口轉換成VGA 接口。DVO 接口的數據位DVO_D[23:0]分別對應RGB888,即:DVO_D[23:16]對應RGB 信號的R[7:0],DVO_D[15:8]對應RGB 信號的G[7:0],DVO_D[7:0]對應RGB 信號的B[7:0]。在本系統中ADV7125 工作在RGB888 模式,故在設計中分別將DVO接口數據信號DVO_D[7:0]、DVO_D[15:8]、DVO_D[23:16]分別與ADV7125 芯片的VGA_B[7:0]信號、VGA_G[7:0]信號和VGA_R[7:0]信號相連接。ADV7125 芯片的時鐘信號由橋片差分時鐘提供,DVO 接口中的同步掃描信號HSYNC 和VSYNC 以及I2C 總線控制信號直接接到VGA接口。同時為了支持顯示器熱插拔功能,使用SPI_CSn2(復用為GPIO 功能)作為DVO 通道的顯示器熱插拔檢測引腳。信號走向如圖3 所示。

圖3 整體信號流向圖

3 電路設計

由于同步控制信號由橋片直接提供且VGA 時序已經確定,故利用ADV7125 將DVO 數據信號轉換成VGA接口電路并不復雜,在設計時嚴格考慮到芯片的基本特性和信號輸入要求即可。整體電路可分為橋片到ADV7125 芯片數據傳輸轉換以及轉換后信號處理并輸出兩個部分,下面就ADV7125 芯片特性、橋片到芯片ADV7125 電路連接、VGA 接口設計以及關鍵信號的處理做詳細介紹。

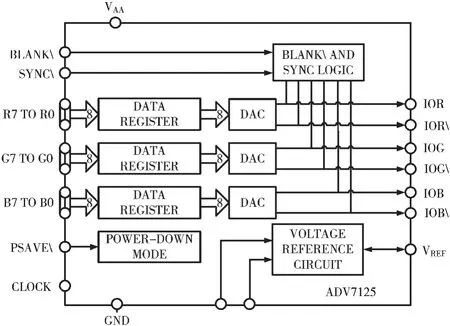

3.1 ADV7125

ADV7125 是一個單芯片高速數模轉換器,吞吐量達330 MS/s,內置著三個獨立的8 位高速分段式架構互補輸出高速DAC,分別對應三個具有8 位寄存器的輸入通道,用來接收數字信號并對視頻數據做對應處理,24 位像素數據(顏色信息)在每個時鐘周期的上升沿鎖存至器件內,之后被提供給三個8 位DAC,然后轉換為三個模擬(RGB)輸出波形[11]。ADV7125 還有兩個附加的控制信號BLANK 和SYNC,以與像素數據相似的方式鎖存至模擬視頻輸出,分別在CLOCK 的上升沿鎖存,以便與像素數據流保持同步,共同作為ADV7125 的輸出信號。

ADV7125 采用單芯片設計,使用相同的電流源保證了單調性和低毛刺,片內運算放大器保證了滿量程輸出電流在面對溫度和電源變動時的穩定性[12]。采用可以進行調節的+5 V/+3.3 V 電源供電,可配置省電模式,多應用于數字視頻系統、高分辨率彩色圖形、圖像處理等方面。其功能框圖如圖4 所示。

圖4 ADV7125 功能框圖

3.2 橋片與ADV7125 連接電路設計

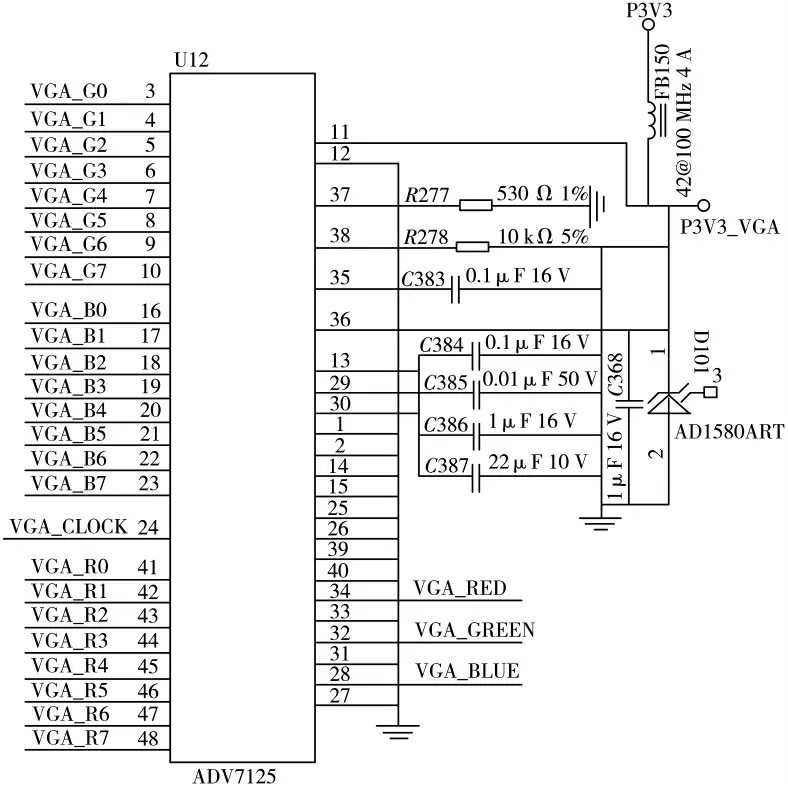

由于VGA 接口的同步信號由顯示控制器提供,故只要將DVO 接口數據的DVO_D[7:0],DVO_D[15:8]和DVO_D[23:16] 分別與ADV7125 芯片的VGA_B[7:0]、VGA_G[7:0]和VGA_R[7:0]直接連接進行數字信號傳輸,ADV7125 芯片的時鐘信號由顯示控制器內部時鐘源產生的差分時鐘提供。詳細電路設計圖如圖5 所示。

圖5 中VGA_B[7:0]、VGA_G[7:0]、VGA_R[7:0]、VGA_CLK 為橋片的輸出端。COMP 端達到補償內部參考運放的功能,通過在COMP 引腳與P3V3_VGA 之間連接一個0.1 μF 的電容來實現。ADV7125 是高精度DAC 芯片,對于參考電平的要求很高,如果以電阻分壓的方式得到參考電壓的話效果并不好,根據ADV7125 設計手冊在電路設計時采用1.235 V 電壓基準芯片AD1580 來產生參考電壓,可以得到穩定的參考電平。ADV7125 的REST 引腳專門用來控制視頻信號幅度,考慮到阻值要求,固定的530Ω用2個200Ω和1個130Ω的電阻來代替,便于后期調節。同時ADV7125 的SYNC 引腳用來控制單一復合同步輸入,由于橋片的圖形處理器可以生成水平同步(HSYNC)、垂直同步(VSYNC)和復合SYNC 信號,不需要ADV7125 產生同步信號,故將SYNC 拉到地,使其永久低電平。省電控制引腳PASVE 為低有效,此處同樣將其接地,實現功耗降低。另外在布局設計時使用了盡可能短的電容引線,盡可能將電容靠近器件放置,將每個VAA 引腳單獨去耦至地,最大程度地降低了引線電感。

圖5 ADV7125 與橋片連接電路

3.3 VGA 接口設計以及關鍵信號的處理

考慮橋片VGA 接口設計要求、信號保護、信號緩沖等方面因素,設計VGA 接口電路如下,分以下三方面進行介紹,并在最后給出VGA 接口原理圖。

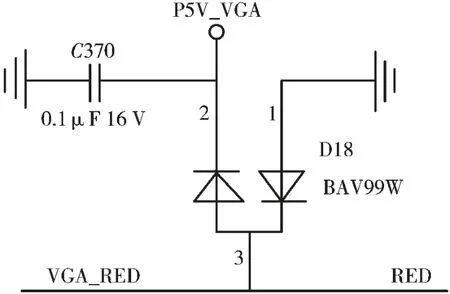

輸出模擬視頻信號的處理:(1)在三個模擬輸出的引腳上分別搭配一個75 Ω 的端接電阻到地,以達到最佳性能,并且在PCB 布局時盡可能地靠近了轉換芯片去削弱信號反射。(2)在信號抵達接口之前,通過LC 濾波電路對模擬信號進行一級濾波優化處理;(3)使用快速開關二極管BAV99W 進行電路保護,BAV99W 相當于兩個二極管,其開關速度快于一般二極管,其接法如圖6 所示。

圖6 BAV99W 連接方式

VGA_RED/GREEN/BLUE、LS7A_DVO_HSYNC/NSYNC 均經過此電路處理。公共端接所需要保護的信號,另兩端一個接電源,一個接地,可以實現泄放超額電壓從而穩定電壓的作用。

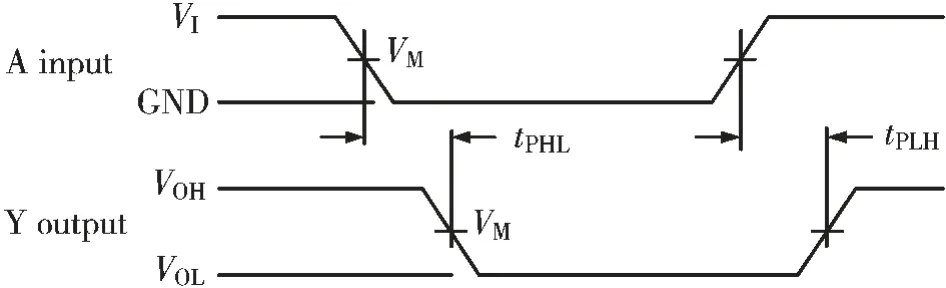

同步信號緩沖處理:視頻同步信號由橋片顯示控制器產生,由設計要求直接輸出至VGA 接口,故需要對信號LS7A_DVO_HSYNC/N 做緩沖處理。本次設計使用74AHCT1G125GV 非逆變緩沖器實現信號緩沖,電路連接以及輸入(A)到輸出(Y)傳播延遲如圖7、圖8 所示。

圖7 74AHCT1G125GV 連接方式

圖8 輸入(A)到輸出(Y)傳播延遲

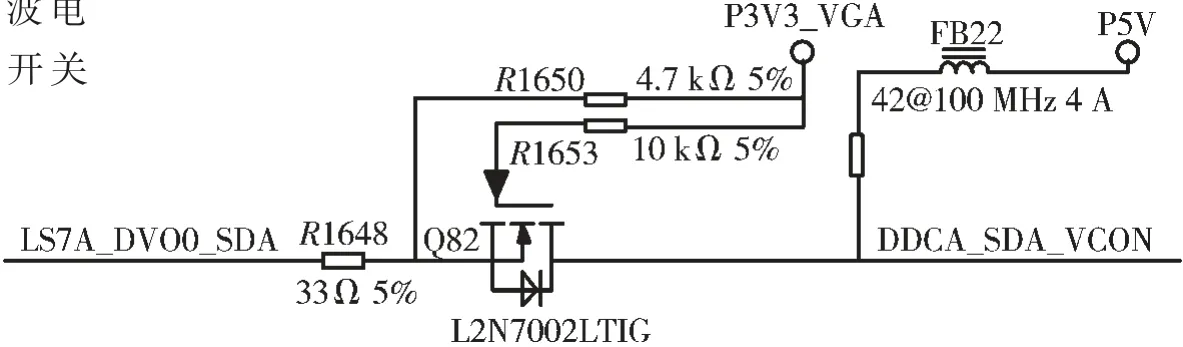

I2C 控制信號的電平轉換:橋片的每個DVO 接口都自帶了一組I2C 信號(使用GPIO 模擬),連接DVO 接口的轉換PHY 芯片和顯示器,專門用于顯示器檢測。根據橋片設計要求,必須使用該組I2C 信號連接顯示器接口,而不使用PHY 芯片輸出的I2C 引腳。橋片輸出I2C 信號電平為TTL 電平,而VGA 接口需要電平為5 V,故需要對SDA/SCL 信號進行電平轉換,此處設計使用常規的MOS 管實現電平轉換,電平轉換電路如圖9所示。

圖9 電平轉換電路

視頻信號、同步信號以及I2C 信號經過處理后連接至VGA 接口即可實現視頻輸出功能。除此之外,還使用了保險絲對VGA 接口進行了保護。VGA 接口及信號如圖10 所示。

圖10 VGA 接口及信號

4 測試結果

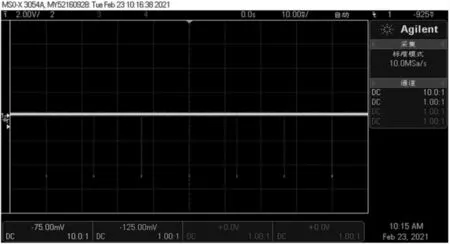

硬件調試后,針對VGA 接口標準進行測試,分辨率設定為1024*768@60Hz,利用MSO-X 3054A 示波器對行場同步信號HSYNC、VSYNC 進行測試,結果如圖11、圖12所示。

圖11 HSYNC 波形圖

圖12 VSYNC 波形圖

由圖中分析可知:HSYNC 的周期為20.68 μs,VSYNC的周期為16.67 ms,與1 024×768@60Hz 模式下的VGA 接口時序要求一致,效果達到設計要求。同時,由模擬信號波形圖可得知其輸出電壓在0~0.7 V 之間,均符合VESA標準及增強型數據顯示通道標準。利用VGA 適配器將主板VGA 接口與顯示器接口連接,顯示器畫面可正常顯示,且無明顯抖動,顯示性能良好。

5 結論

本文在龍芯3A4000 的開發背景下進行了VGA 接口的設計,通過高性能D/A 視頻轉換芯片ADV7125 將橋片輸出DVO 數字信號轉換為模擬信號,并將模擬信號傳輸至VGA 接口,實現視頻顯示的功能。根據VGA 時序要求以及橋片設計要求進行電路設計,并考慮了信號質量以及接口防護方面的要求。經過測試,通過VGA 接口實現視頻輸出功能正常,性能良好,目前已成功應用于龍芯3A4000 主板,滿足功能性、可靠性要求,同時達到了產品級別的要求。