新型PD 協議芯片BMC 解碼電路的設計與驗證*

張萬榮,王飛虎

(北京工業大學 信息學部,北京 100000)

0 引言

近年來,隨著移動設備快速充電功率的不斷提高,USB 標準化組織(Universal Serial Bus Implementers Forum,USB-IF)制定了基于BMC 編碼的USB 功率傳輸(Universal Serial Bus Power Deliver,USB PD)3.0 協議,該協議相比于Qualcomm 公司的快速充電(Quick Charge,QC)協議、Samsung 公司的自適應快速充電(Adaptive Fast Charge,AFC)協議等快充協議具有只占用一根通信線,協議內容可拓展性強等優點,已成為應用最廣的快充協議[1-3]。BMC 解碼模塊是USB PD 3.0 協議芯片的核心模塊[4-6]。隨著手機快充功率突破120 W,峰值電流可達到6.25 A,電流大范圍變化帶來的地電位漂移現象愈發嚴重,地電位漂移導致BMC 信號在傳輸過程中周期多次連續變化使得BMC 信號周期累計變化范圍可達3.3 μs 的±30%[7];隨著USB 線中數據傳輸速率提高到20 Gb/s 使,USB 線包內的電磁環境更加惡劣,從而使得BMC 信號在傳輸過程中受到大量高頻噪聲干擾而導致周期單次大幅度突變[8]。為解決上述問題,近年來人們提出了一些對BMC 解碼模塊優化的方案,文獻[9]提出了一種解碼電路能夠成功解碼周期在3.3 μs±25%范圍內變化的BMC信號,但是當BMC 信號周期累計變化到±30%時不能成功解碼,而是通過錯誤反饋機制強制USB PD 3.0 協議芯片回到初始狀態。

針對上述文獻的不足,本文在傳統解碼模塊的基礎上,首先,通過調整傳統解碼系統的結構并加入狀態機實現了對信號周期單次變化在±25%以內的BMC 信號成功解碼;另外,通過新增的FIR 濾波器產生隨BMC 信號周期浮動的解碼閾值實現了對周期多次連續變化的BMC 信號成功解碼。

1 新型BMC 解碼電路的設計

BMC 解碼規則如圖1 所示,被解碼信號在每一比特開始前先進行一次翻轉,如果某一比特的1/2 位置發生了一次翻轉,則該比特被解碼成二進制數1,如圖1 中第1 比特和第3 比特所示;如果被解碼信號某一比特內不發生翻轉,則該比特被解碼成0,如圖1 中第2 比特和第4 比特所示[10-11]。

圖1 BMC 解碼規則

傳統的BMC 解碼系統電路結構如圖2 所示,包括濾波模塊、邊沿檢測模塊、解碼模塊[12]。首先,數字BMC信號是由模擬信號經過施密特觸發器得到的,容易帶有毛刺,濾波模塊可以濾除寬度為200 ns 以下的毛刺;然后,邊沿檢測模塊輸出的BMC 信號的上升沿和下降沿作為解碼模塊中計數器開始和結束的條件;最后,解碼模塊通過對BMC 信號64 比特前導碼的過采樣求周期的平均值得到解碼閾值,通過對比解碼閾值和計數器計數值的大小解碼數據包的有效數據部分,當計數器的值小于3/4 解碼閾值時解碼結果為1,否則為0。從而實現了BMC 信號的解碼。

圖2 傳統BMC 解碼系統電路結構

為了實現對信號周期單次變化在±25%以內的BMC信號成功解碼,本文將計數器從解碼模塊中分離出來并在解碼模塊內新增狀態機。新型BMC 解碼電路架構如圖3 所示,其中優化后的解碼模塊電路原理圖如圖4所示,Threshold 值進入解碼模塊后先進行移位操作得到1/2Threshold 和1/4Threshold,然后將1/2Threshold 和1/4Threshold、Threshold 和1/4Threshold、1/2Threshold 和Threshold 分別進行加法運算得到3/4Threshold、5/4Threshold、3/2Threshold 的值,通過比較器后得到它們與Cnt 值的大小關系,將比較結果與Edge 信號做與運算后作為狀態寄存器的跳轉條件,D register1 和D register2 構成狀態機的2 比特位寬的狀態寄存器,D register3 為輸出寄存器,當狀態寄存器值為01 且與門And1 產生的結果為1時輸出1,當狀態寄存器值10 與門And1 產生的結果為1 時輸出0。優化后的解碼模塊與其他模塊間的協作方式如圖5 所示。首先,BMC_Signal 信號經過消抖模塊打拍后得到BMC_Signal_Filtered 信號,當解碼模塊檢測到BMC_Signal_Filtered 信號后認為數據開始傳輸,狀態機從Idle 狀態跳到Counter_First 狀態,同時邊沿檢測模塊會檢測到BMC_Signal_Filtered 信號的出現,從而激發計數器開始工作。然后,當BMC_Signal 信號發生跳變時會再次被邊沿檢測模塊捕捉到并使得邊沿檢測模塊產生脈沖信號Edge,當解碼模塊在Counter_First 狀態檢測到Edge信號時會比較計數器產生的Cnt 和閾值Threshold 的大小,如果Cnt 的值處于3/4Threshold 和5/4Threshold 之間,則將當前比特的BMC 信號解碼為0;如果Cnt 的值處于1/4Threshold 和3/4Threshold 之間,則將當前比特的BMC 信號解碼為1。因此,新型BMC 解碼電路可對信號周期發生1/4 形變的信號解碼。

圖3 新型BMC 解碼系統電路結構

圖4 解碼模塊電路原理圖

圖5 新型BMC 解碼系統協作方式

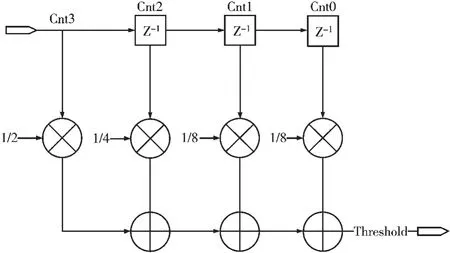

為了實現對周期多次連續變化的BMC 信號成功解碼,本文在新型解碼電路中增加FIR 濾波模塊。新型BMC 解碼電路架構如圖3 所示,其中FIR 濾波器電路原理圖如圖6 所示,其為四階FIR 濾波器,本文設計的FIR濾波器的高通區間為250~350 kHz,通過MATLAB 調用FIR 濾波函數計算得到抽頭系數分別為61、30、16、15。為了減小芯片面積且便于電路實現,本文將抽頭系數h近似為1/2、1/4、1/8、1/8[13-15],由式(1)可知輸出結果Threshold 值不再是固定值,而隨相鄰Cnt 值同向變化。由圖3 和圖5 可知,FIR 濾波器的輸入Cnt 值由計數器和解碼模塊共同決定,當解碼模塊在Counter_First 狀態或者在Counter_Second 狀態檢測到Edge 信號時比較對計數器產生的Cnt 和閾值Threshold 的大小,如果Cnt 的值處于3/4Threshold 和5/4Threshold 之間,則將計數器的值打入FIR 濾波器。FIR 濾波器每接收到一次計數器的傳遞來的結果就會通過FIR 算法更新一次傳送給解碼模塊的Threshold 值,從而完成更新Threshold 的值的正反饋,達到了連續多比特位寬均變化時仍可以成功解碼的目標。

圖6 FIR 濾波器電路原理圖

2 新型BMC 解碼電路的仿真與驗證

傳統解碼算法能夠允許的BMC 信號周期變化范圍為25%,由于供電功率增大或減小導致BMC 信號周期變化超過25%時會導致解碼失敗[16]。圖7 為傳統解碼模塊對周期連續變化的BMC 信號進行解碼的仿真結果。BMC_Signal 為待解碼的BMC 輸入信號;Number 表示當前輸入的BMC_Signal 信號的序號;BMC_Signal_Filtered為BMC_Signal 經過濾波后得到的信號;Edge 信號為邊沿檢測模塊的檢測結果;Counter 為計數器的值,計數器以19.2 MHz 的頻率對 BMC_Signal 信號進行過采樣;Counter_Result 為計數器對前一位BMC_Signal 信號的采樣結果,例如,Number 為2 時Counter_Result 為64 表示計數器以19.2 MHz 的頻率需計數64 次完成對Number為1 時BMC_Signal 的采樣;BMC_Decode_Result 為解碼結果。由圖7 可知,本文仿真了輸入信號BMC_Signal 的前10位的周期以6.25%的速度增加,第10 位到13 位周期保持不變,第13 位到第21 位周期以6.25%的速度升高。周期變化幅度小于25%時,BMC_Signal 的前5 位能夠成功解碼,第6 位到第17 位變化幅度超過25% BMC_Decode_Result 一直為0,解碼失敗,第18 位后BMC_Signal 信號周期重新升到3.33 μs±25%的范圍內后,傳統解碼模塊再次正確解碼。由仿真可知,傳統BMC 解碼模塊只可以對周期在3.33 μs±25%范圍內的信號進行解碼。

圖7 傳統解碼模塊仿真結果

由圖8 可知,本文仿真了輸入信號BMC_Signal 第4位中的254 ns 寬的毛刺成功被消抖模塊濾除,濾波后的信號BMC_Signal_Filtered 沒有毛刺;輸入信號BMC_Signal 前10 位的周期以6.25%的速度增加,第14 位到第18 位的周期以6.25%的速度減小,由于加入了FIR 濾波器使得Threshold 值隨Counter_Result 增大或減小,從而新型BMC解碼電路均能成功解碼。

圖8 新型解碼模塊仿真結果

本文與文獻[9]的性能比較見表1 所列,本文設計的新型BMC 解碼電路可對任意頻率的BMC 信號進行解碼,文獻[9]僅可以對周期在300 kHz±25%范圍內的信號進行解碼,且在華虹半導體0.18 μm 工藝下面積相比于文獻[9]減少了57.29%,功耗相比于文獻[9]減少了89.10%。

表1 性能比較

3 結論

為了實現對單比特周期突變25%的BMC 信號解碼,而且能夠對周期多次連續變化的BMC 信號成功解碼,本文將計數器從解碼模塊中分離出來并在解碼模塊內新增狀態機,另外在傳統解碼電路中增加了FIR 濾波模塊。狀態機的跳轉條件為Cnt 值相對于Threshold 值可變化1/4,實現了對單比特周期突變25%的BMC 信號的解碼;新增的FIR 濾波器使得Threshold 值隨Cnt 值線性變化,實現了對周期多次連續變化的BMC 信號成功解碼。對新型BMC 解碼電路的仿真結果表明,可以對周期相差25%的相鄰兩位BMC 信號解碼,可以對周期以6.25%增加的連續十位進行解碼。