基于嵌入式的通用電子測量儀器硬件平臺設計研究

裴曉燕

(晉中職業技術學院,山西晉中,030600)

0 引言

通過應用嵌入式系統與模塊功能設置,可以優化通用電子測量儀器結構、擴展應用功能、增強應用效用。例如,在現階段使用的通用電子測量儀器之中,主要包括:(1)數字存儲示波器;(2)數據記錄儀;(3)數字頻率計;(4)頻譜分析儀;(5)任意波形發生器;(6)多功能函數發生器;(7)噪聲發生器。由于此類儀器在重量、體積、通用性能、功耗等方面,均具備一定的比較優勢。因而,在與嵌入式系統進行技術融合應用的過程中,通常會根據通用電子測量儀器的實際使用需求,對其硬件平臺進行具體設計。

1 嵌入式通用電子測量儀器體系結構

通用電子測量儀器的功能主要包括了信號產生-獲取、數據采集-控制、數據分析-處理、數據輸出-顯示四大部分。通常設計的典型性嵌入式通用電子測量儀器系統中,上層由嵌入式計算機平臺與嵌入式軟件平臺構成,下層以儀器硬件電路作為支撐。其中,嵌入式計算機系統中包括了CPU、DSP、FPGA、內存,同時,設置有人機交互接口、通信及I/O接口,以及A/D轉換模塊。用戶在具體應用中可以根據在電源系統、DUT、參考信號支持下,通過數字信號調理、RF信號調理、模擬信號調理、RF信號下變頻等直接連接到嵌入式計算機系統。具體的儀器系統結構見下圖1。

圖1 嵌入式通用電子測量儀器系統結構

2 嵌入式通用電子測量儀器硬件平臺硬件設計分析

2.1 儀器硬件平臺設計

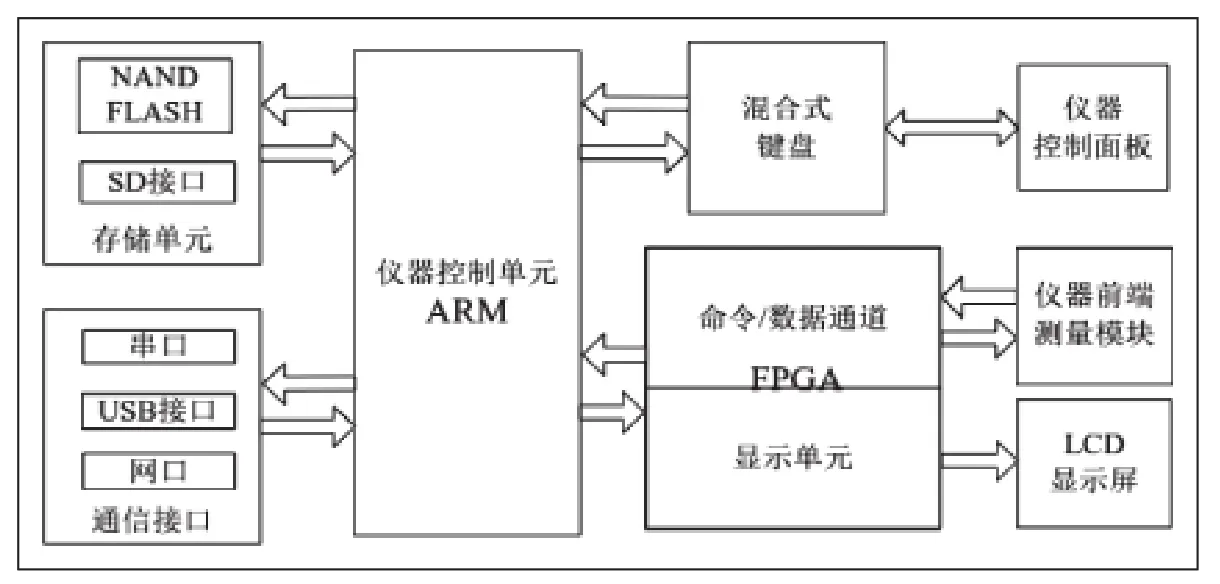

首先,在硬件組成結構方面,主要按照模塊化的單元制式,進行平臺基本結構設置,見下圖2。

圖2 通用電子測量儀器硬件平臺基本結構

其次,根據各相單元制式的模塊功能需求,選擇匹配的硬件配置。具體如下:

(1)在儀器控制單元,選擇普通儀器中的片上系統ARM處理器,其處理速度在200MHz到1GHz之間。其優勢主要體現在內部資源豐富、成本投入適中,以及在消費電子領域的普遍適用性等方面。

(2)嵌入式系統的存儲器以NAND FLASH為準,其特點是速度快、容易小、價格一般、適用性較強。配套的接口選擇SD接口。

(3)在顯示功能方面,按照用戶使用習慣,本次研究中選用彩色型LCD液晶顯示屏。

(4)鍵入功能中按照鍵盤方式功能需求,選擇混合式鍵盤。

(5)命令/數據通道選用FPGA進行邏輯設計。

第三,由于DSP平臺不能較好的支持嵌入式Linux、Windows CE系統的數據處理功能。因而,在本次研究中,根據儀器硬件平臺基本結構確定各項硬件配置后,以平臺架構設計需要為準,選擇了ARM+FPGA結構的設計方案。設計架構見下圖3。

圖3 ARM+FPGA結構的通用電子測量儀器硬件平臺設計架構

在該架構下,可以明確各單元模塊中的功能。例如,儀器控制單元作為核心系統,通過設置輔助電路與內存電路,能夠較好的支持整個操作系統的運行。而存儲單元選擇的存儲卡接口與NAND FLASH能夠幫助儀器平臺,對應用系統生成的定標文件、配置文件,以及應用中的各種測量數據進行全面的存儲,并構建內容完整的文件系統。尤其是在基于FPGA雙顯示緩存LCD液晶顯示屏支持下,能夠以800*480的分辨率,實現乒乓式數據顯示。利用FPGA進行異步FIFO命令/數據通道設計,也能夠使儀器前端測量模塊與顯示單元、儀器控制單元之間建立起一個交互性的數據傳輸路徑,完成測量數據采集與命令傳輸等。加上混合式鍵盤單元中設置的旋轉編碼器、掃描、主機通信電路,能夠較好的實現數據多元輸入與快速轉換及傳輸。另外,以串口、USB接口、網口為通信接口,較好的實現了儀器控制單元ARM核心系統的集成。而且,在以太網接口在專用芯片應用條件下也獲得了有效擴展,有利于擴大應用范圍。

2.2 儀器軟件系統設計

在軟件系統設計方面,本次研究以嵌入式Linux軟件系統為準,能夠在文件系統、Linux、啟動引導代碼支持下,通過連接應用程序、通用電子測量儀器硬件平臺、設備管理器,以及安裝設備驅動程度,完成嵌入式軟件系統應用。軟件系統結構見下圖4。

圖4 軟件系統結構

其中,在開發設備系統驅動程序環節,目標定位在file_operation結構中的文件操作函數方面,所以,僅需要按照了解設備電路原理——對設備地址進行映射與定義設備號——實現初始化函數——設計實現文件操作與定義file_operation結構后,通過設置文件操作函數(如write、read),并于該驅動程序中進行內核編譯,或者采用insmod命令進行模塊加載即可實現對該設備驅動程序的開發。

2.3 儀器硬件電路設計

完成嵌入式通用電子測量儀器硬件平臺搭建、軟件系統設置等上層系統后,需要對應下層系統功能設置,配套的進行儀器硬件電路設計。本次研究中主要按照通用電子測量儀器硬件平臺架構中的單元模塊進行電路設計。分述如下:

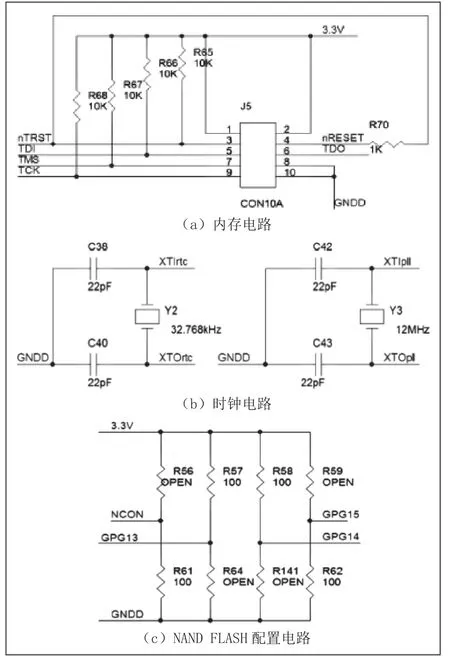

(1)儀器控制單元中包括了控制單元處理器電路、內存電路、輔助電路,以及PCB布線。由于本方案中選用了S3C2400嵌入式微處理中,配置了ARM920T內核。因而,在設備接口相對較多的情況下,根據AHB系統總線、APB系統總線進行了內部資源功能分區,然后,根據平臺地址空間映射關系,設置了具有自刷新功能與掉電模式的SDRAM控制器。因而,在內存電路方面,主要按照芯片、處理器對應引腳線連接的方式與4字節尋址單位設置,較好的實現了內存電路基礎上的通信關聯。在JTAG、時鐘、芯片配置方面的輔助電路細化程度較高,具體見下圖5。

圖5 輔助電路 (部分)

PCB布線以SDRAM高速器件為準,根據電路范疇選用了“短布線、且等長”的基本原則進行了仿真布線設置。簡單講,所有電路的布線均按照現實布線方式,選擇對應的仿真模型。例如,在SDRAM時鐘線的PSCLK仿真模型中,本次研究中選擇了IBIS模型,利用V/I曲線建模方法,完成了對I/O BUFFER的精準建模。另外,考慮到關鍵信號的傳輸精準性問題,本次研究中選擇了阻抗匹配方案,能夠預防信號反射時產生的振鈴、過沖、下沖等問題。繼續以時鐘線仿真結果為例,在匹配源端阻抗后,明顯在信號傳輸方面優化未匹配阻抗的方案。匹配阻抗前后的仿真結果見下圖6。

圖6 SDRAM 時鐘線 PSCLK 在阻抗匹配前、后的仿真結果

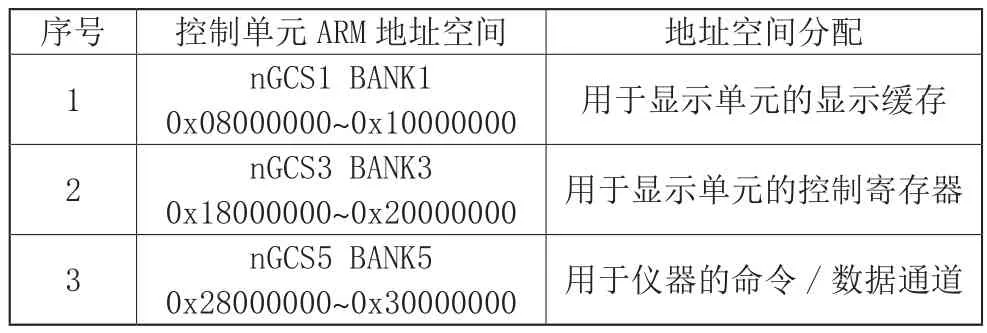

(2)其它單元的電路設計如下:首先,在存儲單元主要按照NAND FLASH電路與SD卡接口電路進行具體設計,SDCRAD中選用的SPI模式,能夠滿足多種微控制器中的通信協議需求。其次,在顯示單元則按照S3C2440內部集成的LCD控制器結構(ARM系統總線、控制模塊、LCD FIFO、LCD屏幕接口),配套FPGA顯示緩存1與顯示緩存2,設置顯示緩存電路與LCD顯示接口電路。除此之外,在地址分配方面,儀器顯示單元與命令/數據通道的地址空間分配如下表1所示。

表1 儀器顯示單元與命令/數據通道的地址空間分配

第三,在混合式鍵盤電路設計中按照鍵盤接口(串口)、鍵盤控制器、8條行掃描線、6條列掃描線、8*6矩陣鍵盤構成,通過旋轉編碼器鑒相電路將旋轉編碼器與前面構成部分進行關聯,當鍵盤控制器電路與主機通信電路等關聯起來后,可以實現正旋、反旋運用。至于儀器接口方面的RS232接口電路、USB主從接口電路、以太網接口電路設計,分別采用了UART邏輯電平轉換方案、引腳連接方案、專用芯片方案。最后,借助儀器平臺顯示單元的邏輯設計(時鐘、控制、LCD時序模塊)、命令/數據通道邏輯設計(FPGA XC3S400A 內嵌45KB 的 RAM),應用嵌入式Linux分區結構實施系統調試與試運行。

3 結束語

隨著數字電子技術的快速發展與應用,通用電子測量儀器便進入到了智能化發展階段,通過對微處理器的應用,解決了硬件邏輯、軟件靈活度問題,全面提高了數據處理功能。通過以上初步分析可以看出,在應用嵌入式系統后,可以建立關于通用電子測量儀器的硬件平臺。以基于ARM+FPGA的硬件平臺架構設計情況為例,其適用性、功能性可以獲得科學設置,可以充分發揮FPGA中的邏輯設計優勢,從而在嵌入式Linux操作系統下,較好的完成平臺開發。另外,通過對該平臺的使用,能夠進一步對PCB設計中的布局布線、LCD顯示功能、用戶界面等實施優化處理,從而達到對通用電子測量儀器諸項功能的有效使用。