基于SiP 封裝的DDR3 時序仿真分析與優化

王夢雅,曾燕萍,張景輝,周倩蓉

(中國電子科技集團公司第五十八研究所,江蘇 無錫 214035)

0 引言

系統級封裝(System in Package,SiP)是利用先進封裝技術將不同功能的芯片集成在一個微系統內,具備小型化、低功耗和高性能等優勢,已成為半導體行業關注的重要焦點之一[1-4]。SiP 中經常集成高頻率高帶寬的DDR3系統來實現存儲功能,但是與傳統PCB 不同,基于SiP封裝的高密度互聯DDR3 的復雜性設計帶來的信號完整性問題日益嚴重[5-8]。除了單純從信號的眼圖和波形來判斷信號質量外,DDR3 的設計還面臨著嚴格的時序要求,即使信號波形達到JEDEC 協議中規定的判決標準,數據與選通信號、地址與時鐘信號等之間的時延也不一定符合協議規范,DDR3 的接口時序分析成為DDR3 設計的重中之重[9-10]。

基于SiP 封裝的DDR3 設計一旦出現問題,再重新投產會造成時間和成本的浪費,為了解決這一問題,引入了仿真的概念。根據產品不同設計階段分為前仿真和后仿真,分別針對產品布線前和布線后[11-12]。本文主要針對后仿階段,從一例實際SiP 項目中的DDR3 封裝和基板設計著手,進行數據與選通、地址與時鐘之間的時序仿真,通過仿真結果分析其信號薄弱點,結合該項目各方面情況提出優化方案,經過仿真迭代,使信號符合JEDEC 協議規范,為SiP 的DDR3 時序仿真和優化提供很好的借鑒和指導作用。

1 DDR3 時序規范與計算理論

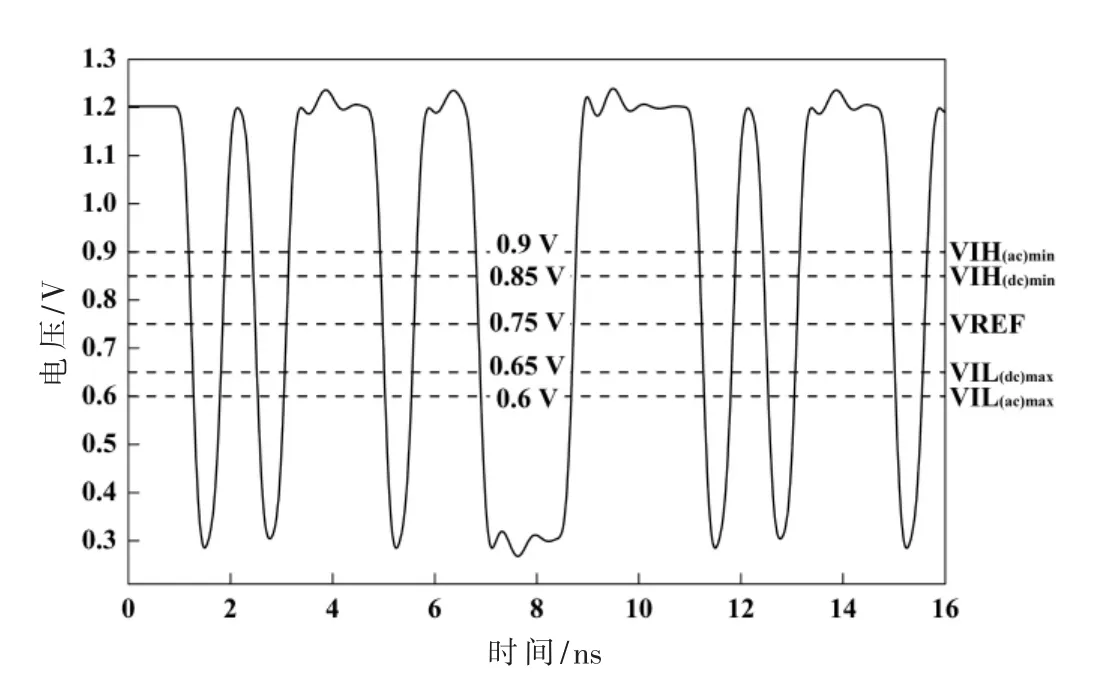

JEDEC 協議定義了AC 和DC 兩種輸入電平閾值,輸入信號必須達到AC 電平以滿足時序要求,而信號的邏輯狀態由DC 電平來決定。圖1 所示為DDR3(AC150/DC100)單端信號判決標準,上升沿時,信號穿過VIH(ac)min電平至下降到VIH(dc)min電平為高電平有效時間。下降沿時,信號穿過VIL(ac)max電平至上升到VIL(dc)max電平為低電平有效時間[13-14]。差分信號與單端信號類似,其VIHdiff(ac)min為0.3 V,VIHdiff(dc)min為0.2 V,VILdiff(dc)max為-0.2 V,VILdiff(ac)max為-0.3 V。

圖1 單端信號判決標準示意圖

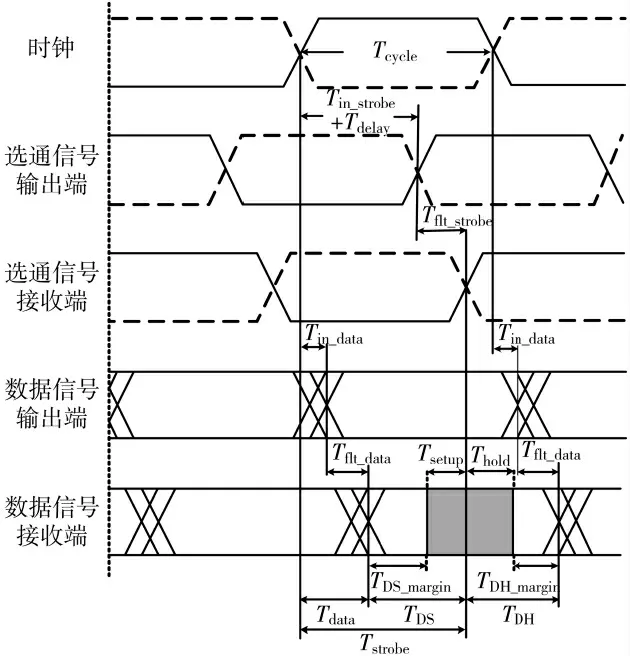

JEDEC 協議中規范了數據信號正確鎖存所需要的最小建立時間Tsetup和最小保持時間Thold。所以數據信號的建立時間TDS和保持時間TDH應大于規范要求,存在一定裕量,才能滿足時序要求。以數據與選通時序為例,其時序裕量計算過程如下[15-16]。

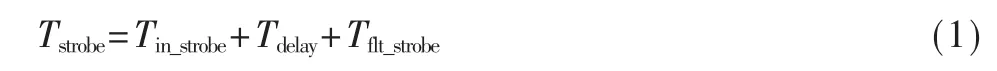

圖2 為DDR3 的數據信號和選通信號的時序分析示意圖。時鐘輸入到選通信號到達接收端的時間Tstrobe為:

圖2 DDR3 數據與選通信號時序分析示意圖

式中,Tin_strobe為系統時鐘輸入到選通輸出時間;Tdelay為選通信號相對數據信號的延時時間(1/4 時鐘周期);Tflt_strobe為選通信號互連通道傳輸時間。

時鐘輸入到數據信號到達接收端的時間Tdata為:

式中,Tin_data為系統時鐘輸入到數據輸出時間;Tflt_data為數據信號互連通道傳輸時間。

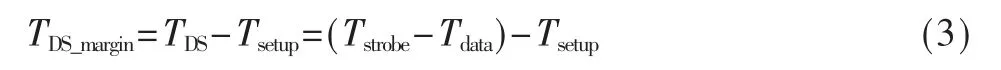

建立時間裕量TDS_margin為:

第一個時鐘邊沿觸發的數據到達接收端后會一直保持到下一時鐘邊沿觸發的數據到達接收端,保持時間裕量TDH_margin為:

式中,Tcycle為時鐘邊沿觸發間隔時間。

Tsetup與Thold通常基于一特定轉換速率,單端信號以1 V/ns 為基準,差分信號以2 V/ns 為基準。在實際DDR3系統中,由于芯片驅動能力、布線、負載等的不同,信號翻轉速率通常不同于基準速率,因此需要根據信號實際情況動態調整建立和保持時間裕量。另外,同一信號或同組信號的Tin_data與Tin_strobe由于受芯片制造工藝、工作電壓、溫度等因素的影響會有所不同。同一數據信號的Tflt_data受碼間干擾等因素影響在不同時鐘周期下也會不同。要根據各信號各周期的實際情況來計算各周期的時序裕量,通常借助仿真工具進行時序計算。

2 基于SiP 的DDR3設計

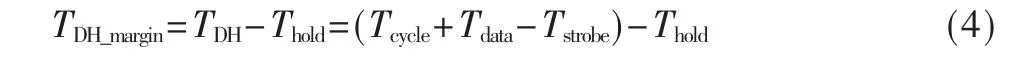

本項目SiP 基板共有70 層金屬層(MP1-MP70),金屬層之間填充介質層。其中DDR3 系統由FPGA 控制器和兩顆DDR3 芯片組成,DDR3 芯片經過RDL 后平鋪在SiP基板上。單顆DDR3 芯片的容量是2 Gb,速率為1.6 Gb/s,16 位數據。此DDR3 系統數據線(DQ0-DQ31)采用點對點的互聯拓撲,地址線(A0-A15)采用Fly-by 型拓撲并通過40.2 Ω 電阻上拉到0.75 V 的電源,如圖3 所示。基于DDR3 時序要求,數據線DQ0-DQ7 與DQSN0/P0 同層等長布線,數據線DQ8-DQ15 與DQSN1/P1 同層等長布線,以此類推。地址線與時鐘線等長布線。

圖3 基于SiP 的DDR3 設計示意圖

3 時序仿真分析與優化

本項目通過ANSYS SIwave 軟件按照數據信號DQ和選通信號DQS、地址信號與時鐘信號分兩組提取控制器端到Memory 端信號S 參數,包括基板與RDL 布線,完成頻域仿真。隨后利用Cadence SystemSI 軟件搭建基板與RDL 級聯的拓撲,分別進行以上兩組的時序分析,通過問題定位與版圖優化,經過仿真優化迭代使所設計的DDR3 信號滿足JEDEC 協議規范。

3.1 數據信號時序仿真分析與優化

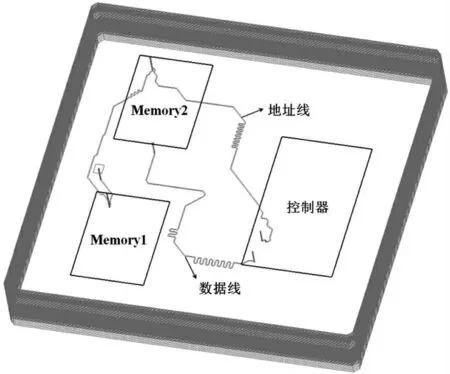

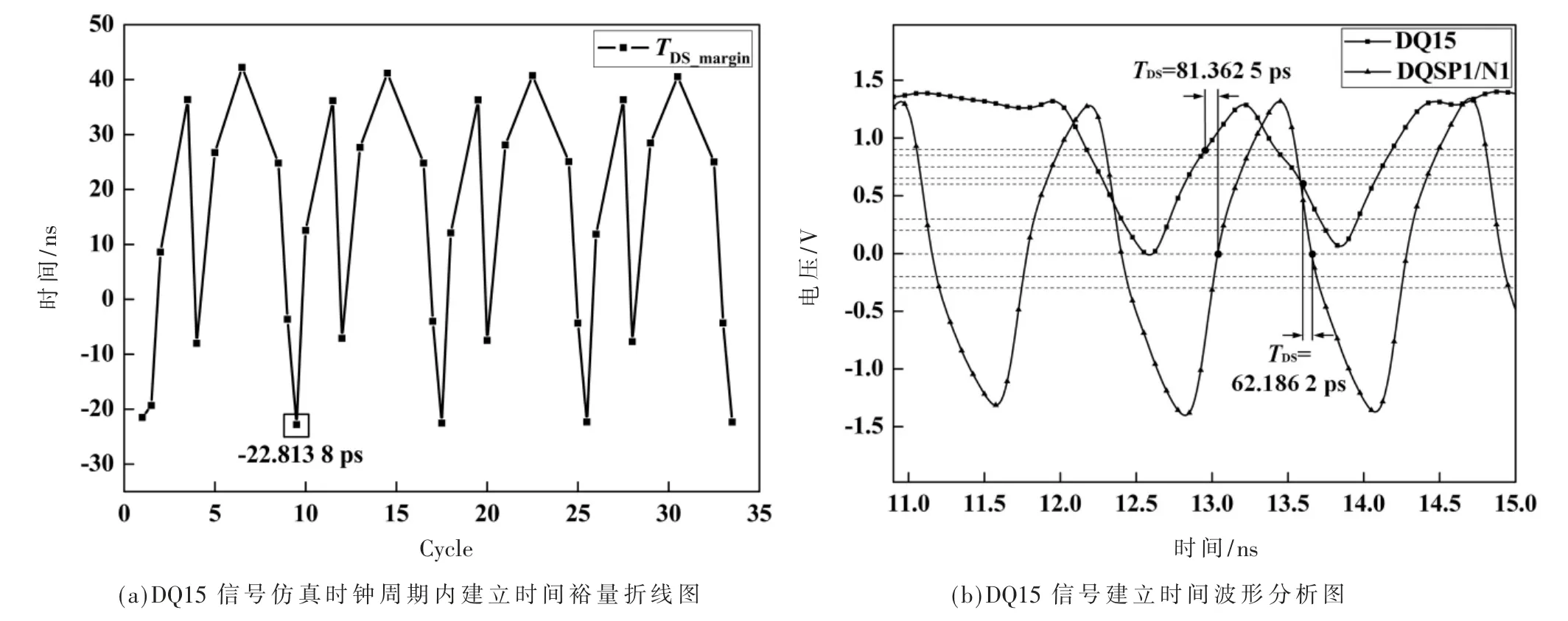

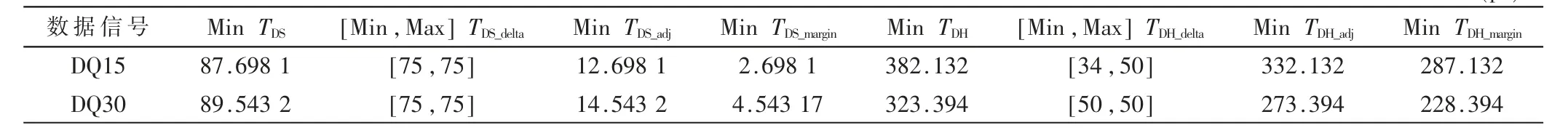

在數據寫時,按照時序要求,DQS 信號相對于DQ 信號延遲0.25 個時鐘周期發出。通過DQ 的時域仿真可以發現其單純從波形來看DQ 信號滿足判決標準,但是DQ8-DQ15 與DQ24-DQ31 信號相對于各自的DQS 信號的建立時間裕量不足,下面以上述兩組中分別最差的DQ15 與DQ30 為例,進行分析與優化。DQ15 與DQ30 的時序仿真結果如表1 所示,DQ15 與DQ30 的建立時間未滿足DDR3 規范在1.6 Gb/s 速率下所要求的最小建立時間,以至裕量為負值。圖4(a)為DQ15 信號在整個仿真時鐘周期(Cycle)內建立時間裕量折線圖,根據碼型的不同,信號在不同Cycle 下的建立時間也隨之變化,約一半周期下的建立時間裕量為負值,在第9.5 個Cycle 下建立時間最短,為-22.813 8 ps。結合DQ15 信號的波形進行分析,如圖4(b)所示,建立時間裕量不足是由于DQ15 信號上升下降沿過緩引起的。本項目SiP 體積小,DDR3 布線密,尤其是過孔之間的間距嚴重不足,過孔間的串擾可能是導致上升下降沿過緩的原因。

表1 DQ15 與DQ30 信號的時序仿真結果 (ps)

圖4 DQ15 信號的時序仿真結果

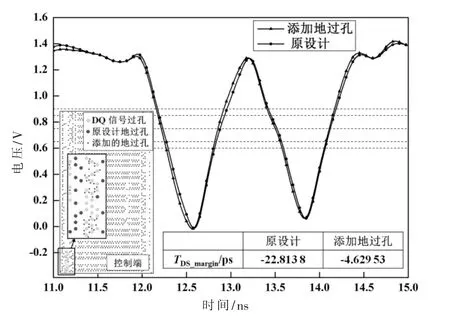

通過對DQ8-DQ15、DQ24-DQ31 兩組數據信號過孔較密的控制端信號過孔之間增加相應長度的地過孔,仿真結果如圖5 所示。增加地過孔,減少信號間的串擾,上升下降沿更加陡峭,可以使建立時間延長,改善時序問題,進一步驗證了長過孔串擾的影響。

圖5 添加地過孔后DQ15 信號的時序仿真結果

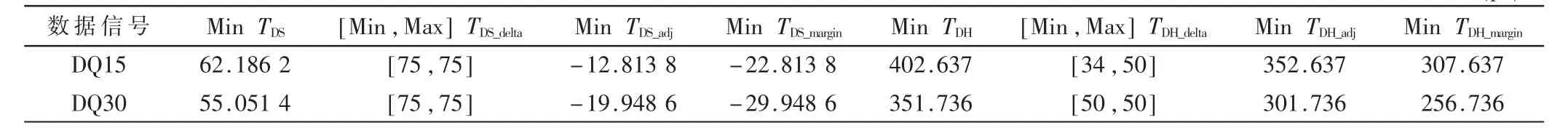

但基于本項目SiP 加工與各方面實際因素的考慮,上述過孔的優化不能用于本項目的實際情況。對于DQ8-DQ15、DQ24-DQ31 兩組數據信號建立時間裕量不足的問題,考慮適當延長DQS 的線長來滿足時序要求,通過裕量計算,將DQSN1/P1 延長2 mm,DQSN3/P3 延長3.5 mm。DQ15 與DQ30 的時序仿真結果如表2 所示,其余數據信號也均滿足時序要求。在優化完成后,對數據讀信號進行仿真驗證,也均滿足時序要求。

表2 優化后DQ15 與DQ30 的時序仿真結果 (ps)

DQS 與時鐘之間的時序,只要滿足布線規則,可以在DDR3 實際工作中通過“Write leveling”功能進行自動調節,故在本文不進行仿真。

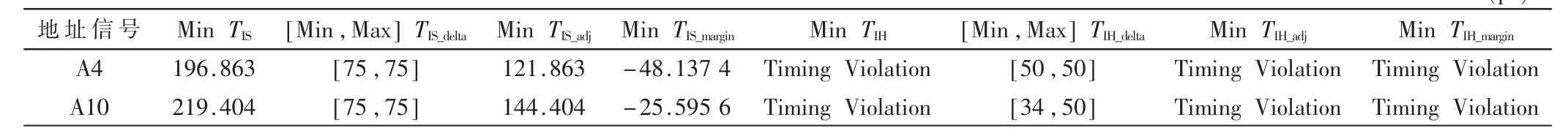

3.2 地址信號時序仿真分析與優化

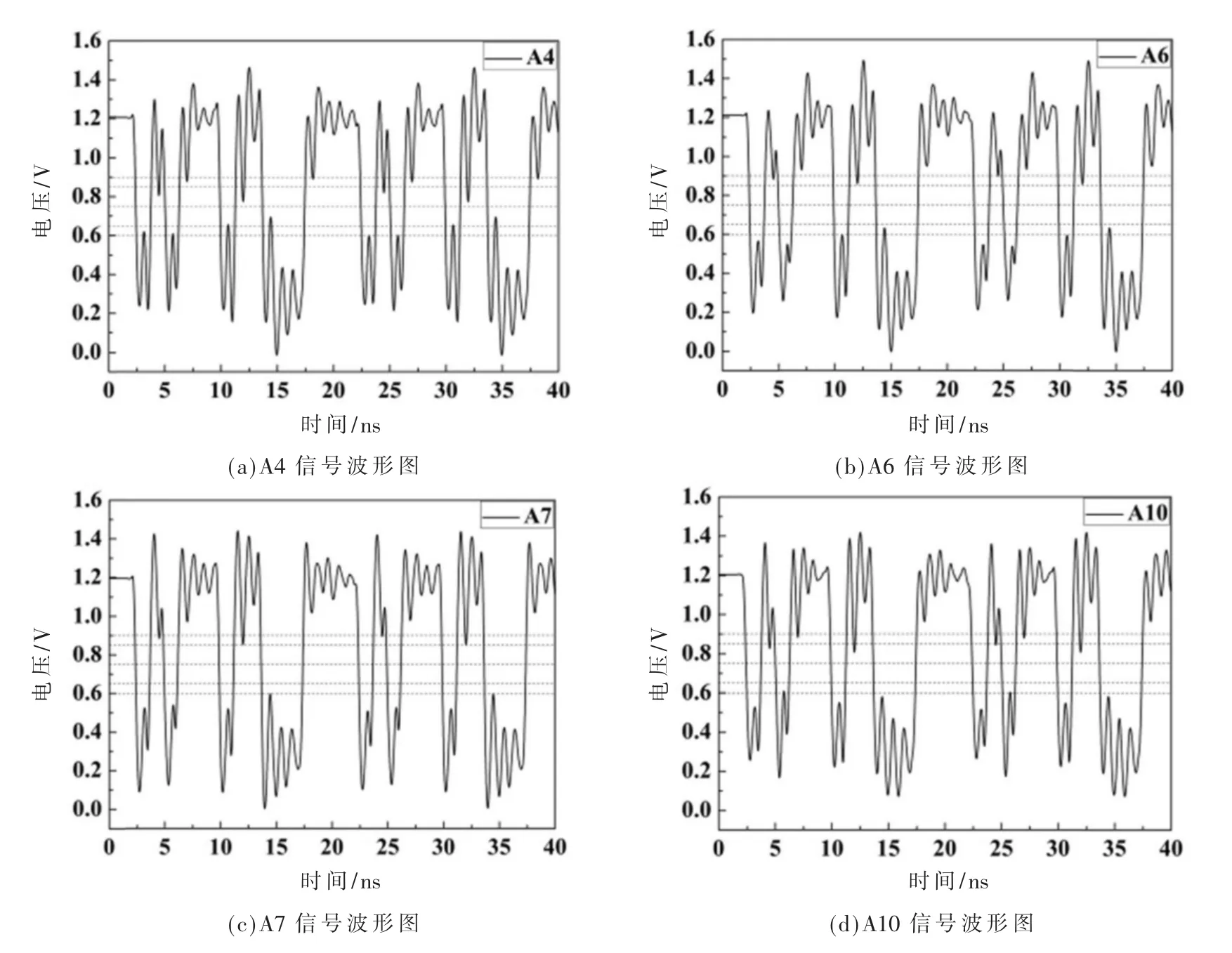

按照時序要求,時鐘信號相對于地址信號延遲0.5個時鐘周期發出,經過時序仿真發現,A4、A10 地址信號不滿足時序要求,建立時間裕量不足,并且保持時間及其裕量無法判斷(Timing Violation),如表3 所示。由此可猜想,A4、A10 地址信號定存在較大震蕩超過判決標準造成時序混亂。結合仿真波形來看,Memory2 地址信號波形存在震蕩,尤其是A4、A6、A7、A10 信號震蕩較為嚴重,如圖6 所示。A6、A7 震蕩幅度只超過AC 電平尚滿足邏輯狀態,但是A4、A10 信號震蕩幅度超過DC 電平使時序錯誤,和上述地址信號時序仿真結果相呼應。

表3 A4、A10 的時序仿真結果 (ps)

圖6 A4、A6、A7、A10 地址信號仿真波形圖

該項目地址信號由于采用Fly-by 結構,線路中存在分叉點即阻抗不連續點,極易形成反射影響信號質量產生震蕩,并且由于該SiP 布線過密,信號之間的串擾又加重了震蕩的幅度。Memory1 相對于Memory2 距離FPGA較遠,Memory1 的地址線信號幅值低于Memory2 的地址線信號,但Memory1 靠近終端上拉電阻能夠消除一部分反射,反而信號質量較好,Memory2 的地址線信號則存在較大震蕩,造成時序不滿足要求。

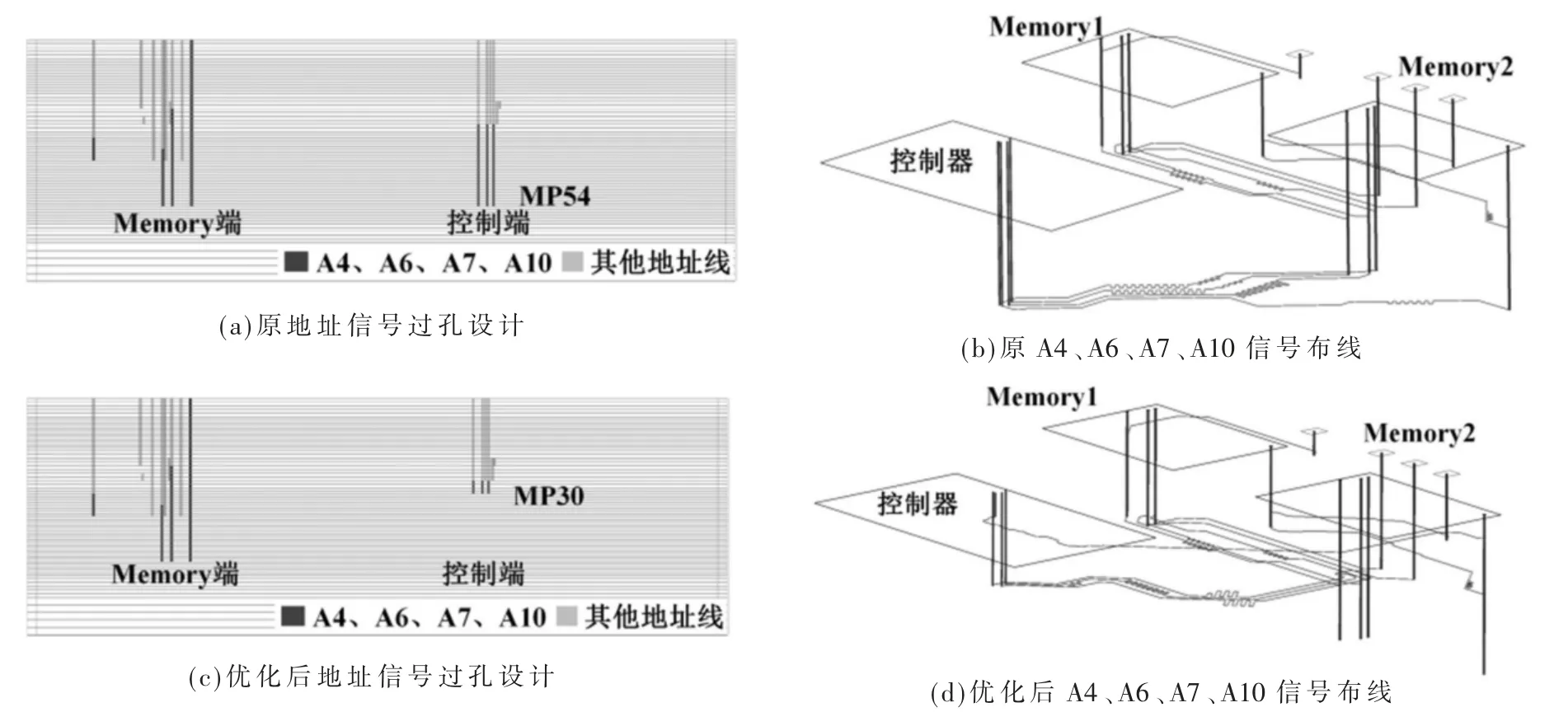

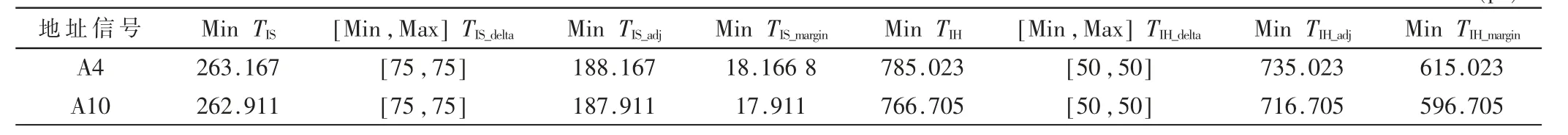

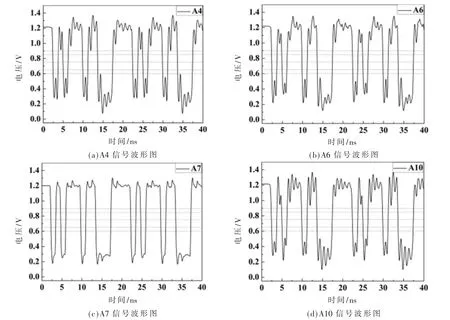

在后仿時,應綜合考慮各方面因素,找到最快速最精簡的方法改進設計,避免過設計。通過版圖分析,A4、A6、A7、A10 信號相對于其他地址信號布線較深,最長過孔位于MP54 層,并且控制端過孔布線過密。將控制端A4、A6、A7、A10 過孔縮短并調整間距,布線層上移,減少過孔間的串擾,如圖7 所示。通過對優化后的版圖進行時序仿真,A4、A10 信號的建立時間與保持時間裕量均達到要求,如表4 所示。結合仿真波形,如圖8 所示,A4、A6、A7、A10 信號的震蕩幅度 也獲得較大改善,滿足DDR3 規范要求。

圖7 地址信號過孔布線優化方案

表4 優化后A4、A10 的時序仿真結果 (ps)

圖8 優化后A4、A6、A7、A10 地址信號仿真波形圖

4 結論

本文介紹了DDR3 的時序計算與仿真,結合一例實際SiP 項目中的高密度互連DDR3 系統封裝和基板設計方案,進行DQ 與DQS、地址與時鐘之間的時序仿真與優化。通過仿真發現,在信號波形滿足DDR3 的AC 和DC 判決標準后,其建立時間與保持時間仍可能不滿足DDR3 的時序要求,驗證了DDR3 時序仿真的重要性。本文在項目后仿階段,針對DQ 與DQS、地址與時鐘之間的不合格時序信號,進行具體分析,討論時序與波形之間的關系,結合版圖分析,提出優化方案并通過仿真迭代進行驗證。鑒于后仿真階段對設計修改的局限性,最終得到切合實際的優化方案,使所有信號均滿足JEDEC協議規范。通過仿真來指導設計,為SiP 的DDR3 系統的設計與優化給出方向和建議。