Buck 芯片緩沖電路設計的仿真分析與應用*

葉豐華,劉 昊,康 磊,蔡文波

(浪潮電子信息產業股份有限公司 浪潮高效能服務器和存儲技術國家重點實驗室,北京 100086)

0 引言

Buck 芯片工作的基本原理是將高輸入電壓斬波成具有一定占空比的周期脈沖,之后再通過LC 濾波器將周期脈沖整合成穩定的低壓直流電[1-3]。

傳導高壓脈沖信號的位置稱為Phase 點,常用Buck電源的典型參數為開關頻率500 kHz,輸入電壓12 V。Phase 點在500 kHz,0 V~12 V 脈沖的作用下,成為了一個不可忽略的噪聲源。

為了降低開關損耗,當前開關電源的MOSFET 開關速度非常快,即Phase 點波形的上升沿和下降沿的斜率很高。芯片內的寄生電感(ESL)在這樣的激勵下能夠在Phase 點產生很大的過沖 (Overshoot)[4-5],Phase 點過高的Overshoot 會超過下管MOSFET 的耐壓值,造成MOSFET過壓損壞[6-8],使用緩沖電路可以削弱過沖對電路器件的負面影響。

本文通過對緩沖電路的緩沖效果進行比較分析,結合Buck 芯片中不同的緩沖方法下測得的電源效率,在仿真結果的輔助下評價兩種緩沖方式的性能,探究緩沖電路的設計技巧,作為指導Buck 芯片緩沖電路設計的方法。

1 Buck 開關電源中緩沖電路的設計

為Phase 點到GND 設置緩沖吸收電路可以吸收Phase波形中的高頻噪聲,降低電壓過沖和電磁輻射[9]。使用緩沖電路延緩開關速度,同樣能夠起到抑制Phase 點電壓過沖的作用[10]。

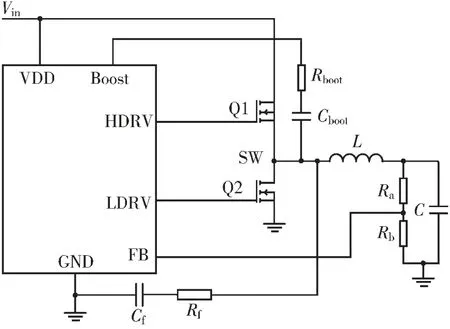

1.1 Buck 開關電源原理

Buck 開關電源的基本原理如圖1 所示。控制IC 分別控制Q1、Q2 兩個MOSFET 的開關,當Q1 導通Q2 斷開時,Vin通過導通的Q1 將能量傳輸到輸出電感L,輸出電容C 和負載。當Q1 斷開Q2 導通時,因為電感和電容當中儲存了能量,且因為電感的慣性不能允許電流的突變,會維持向負載端供電的狀態,將電感中儲存的能量傳遞到負載,Q2 此時起到續流通路的作用[11]。

圖1 Buck 型變換器原理示意圖

圖1 中共有兩處應用了緩沖電路,SW 點(即Phase 點)到BOOST 的RC,和SW 點到GND 的RC。

1.2 SW-GND 緩沖電路設計

Buck 開關電源的Phase 波形出現過沖和震蕩的直接原因是寄生參數,如ESL(寄生電感)、等效電阻、電容等,這些參數無法避免。

圖2 中Llp(Hi)是上管MOSFET Q1 的引線電感,Rds(on)是上管Q1 導通時的電阻值。Llp(lo)是下管MOSFET Q2 引線電感,Coss是下管Q2 的DS 兩級之間的等效電容,當Coss被充電,其上的電壓為

圖2 等效寄生參數電路

當上管導通時,等效于Vin通過圖2 的通路對下管Q2的寄生電容Coss充電從而產生VDS的波形,VDS就是Phase點的波形。

由于圖2 的通路中存在電感電容和電阻,因此當上管導通時,即便Coss已經上升至Vin,電感因為慣性還會繼續給Coss充電,形成過沖。

研究上管導通下管斷開的瞬間,此時由于Q1 突然的導通,導致回路上寄生電感儲存了能量,根據能量守恒定理,電感中儲存的能量轉移到電容中,得到:

式(1)中iqrr是通過下管MOSFET 的最大電流,vp是下管MOSFET 上的最大波動電壓,求vp的表達式疊加基準輸入電壓得到:

其中VPK是過沖電壓的最大值,Vin是輸入電壓的大小,輸入電壓疊加最大波動電壓得到最大過沖電壓。iqrr是MOSFET 體二極管的反向恢復電流,這個電流是下管MOSFET 寄生二極管反轉過程中的最大值電流,由此確定了SW 點波形的最大過沖。

式(2)中的寄生電感Llp(Hi)和電流iqrr通常在芯片內進行補償。芯片外,可以在SW 點和GND 之間加入一個電容Cf,該電容Cf和Coss形成并聯的關系,能夠等效地增加Coss的大小,從而也能夠抑制最大過沖的峰值。由此確定,SW 到GND 加入電容Cf的做法能夠優化過沖電壓。

被吸收的能量不會損耗在抗性元件上,而是耗散在電阻上,為了將電容吸收的過沖能量耗散,并且易于控制緩沖器的整體阻抗,則在Cf通路上再串聯一個Rf,最終的做法是在SW 和GND 之間加入一個RC 串聯電路。

站在頻域的角度分析Cf電容的選型,電容濾波的本質基于電容的頻域阻抗曲線,常在某一頻率達到低至10 mΩ~100 mΩ 的阻抗,這樣的低阻抗能夠用于吸收特定頻段的噪聲[13]。

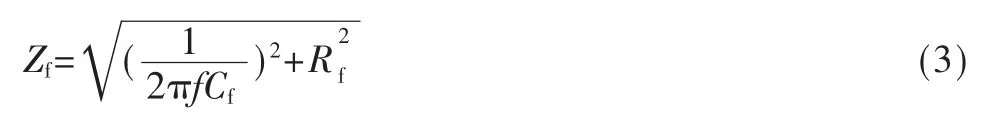

根據電容頻域阻抗公式結合Rf得到緩沖電路阻抗:

其中Zf是整個緩沖電路的頻域阻抗,f 是頻率。

去除所有的緩沖設計,測試phase 波形中的噪聲振蕩頻率f,為濾除該噪聲令該頻段下電容阻抗小于100 mΩ,可供選擇的電容容值即可計算得到:

聯系式(4)知,足夠大的Cf能夠有效濾除噪聲,但是不能太過偏離上式所計算出的電容值,否則濾波的頻段會產生偏差。

雖然使用緩沖電路能夠濾除噪聲降低過沖,但本質上是在消耗功率,SW-GND 緩沖電路必然會在一定程度上影響開關電源的效率,這在對于開關電源效率要求甚高的應用場合提出了挑戰,研發人員需要既達到緩沖性能的要求,又不對效率造成明顯的損失。

Vin通過輸入點到SW 點的電感Llp(Hi)對下管MOSFET的DS 電容Coss充電,后級電路是與之并聯的緩沖電路Rf和Cf。面對上管MOSFET 的突然打開,上述電路會產生階躍響應,Cf上的電壓UCf將會產生變化,通過Rf的部分將會產生功耗損失:

其中Q 是緩沖電路產生的功耗,t 是計時時間,該緩沖電路產生的功率損失與Cf、Rf的大小正相關。

1.3 BOOST 緩沖電路設計

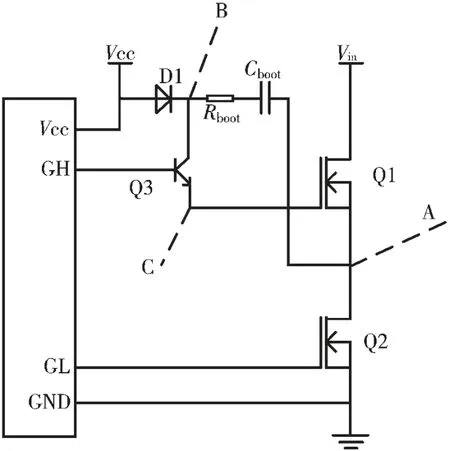

Buck 芯片驅動原理如圖3 所示。

圖3 Buck 芯片驅動電路簡圖

GH 和GL 發出的驅動信號分別驅動Q1 和Q2,輸出信號GH 經過射極跟隨器后驅動Q1。射極跟隨器的工作電源由自舉電路RC 提供,當下部開關Q2 導通時,通過D1 給Cboot充上電壓Vcc。當上部開關Q1 導通時,B 點和A 點的電壓都上升,但是壓差VBA保持不變,被抬升的B 點電壓將成為射極跟隨器的工作電壓[14-15]。

射極跟隨器導通后,相當于Cboot對Q1 的GS 之間的寄生電容Cgsh充電,其上的電壓為vgsh,用Vboot表示Cboot上的電壓,則Q1 導通的過程相當于Cboot中的初始電壓Vboot經過Rboot向Cgsh充電的過程,使得vgsh達到UGS(th)之后MOSFET 即可導通。

當Cboot遠大于Cgsh時,Cgsh的充電方程滿足:

MOSFET 的漏極電流iD和GS 之間電壓vgsh的關系式如下:

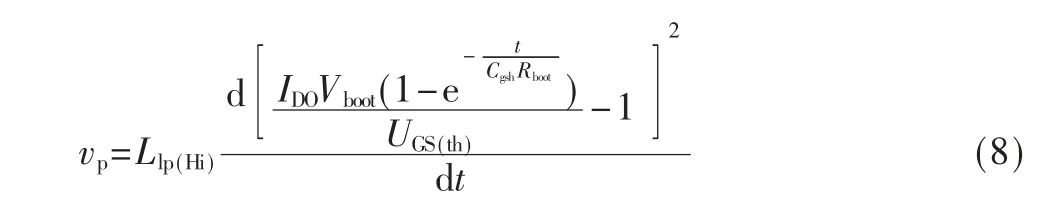

其中IDO是vgsh=2UGS(th)時的iD,該方程可以體現一個MOSFET 開啟快慢,Phase 波形的最大波動vp和iD的關系是:

所以更改Rboot可以通過改變MOSFET 的開啟速度達到限制過沖的效果。

當不滿足Cboot遠大于Cgsh時,vgsh最終穩定電壓是:

只有當Cboot遠大于Cgsh時,式(9)才成立,此時Vboot近似于不變,Cboot可近似為理想電壓源。增大Cboot放電的時間常數,可以保證上管導通時間內Vboot只有較小的波動,但在實際應用中,Vboot總會產生一定的跌落,為了確保電壓跌落不影響MOSFET 正常導通,工程上認為Vboot波動不可超過5%。根據式(10):

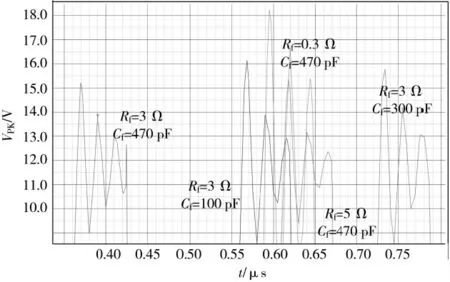

式中iBST是Cboot的放電電流,芯片數據手冊中可以查找到其最大值;Vboot(D)是在上管導通時間內Vboot的變化;ton是指上管導通的時間。若已知Buck 電源的占空比D,初始驅動電壓Vcc,開關頻率f,則可以計算出Cboot的最小值:

為了保證當上管斷開,下管導通時,Vcc能夠快速完成對Cboot的充電,RbootCboot的時間常數τ 不宜過大,工程上認為至少要使Cboot在下管導通的10%時間內完成充電,利用式(12)可以求出Cboot的最大值:

MOSFET 在開關過程中會產生開關損耗,其根本在于每次MOSFET 的開關變換都不可避免地存在V-I 交疊。MOSFET 的每個極間電容在每個開關過程中需要充放電,以完成整個開關過程,所以V-I 交疊會持續一定的時間。當電容越大,充電時間就會增大,MOSFET 開啟速度更慢,V-I 交疊時間越長,結果導致開關損耗變大,可以計算MOSFET 開啟至V-I 交疊完成之前的時間[16]表示如下:

其中,Cgdh是MOSFET 的GD 兩極之間的電容,I0是負載電流,g 是MOSFET 的跨導。在其他條件保持一致的情況下,當增大Rboot以減緩MOSFET 導通速度時,則必然增加V-I 交疊的時間,從而導致功率損耗的增加。

2 Buck 芯片緩沖電路的仿真

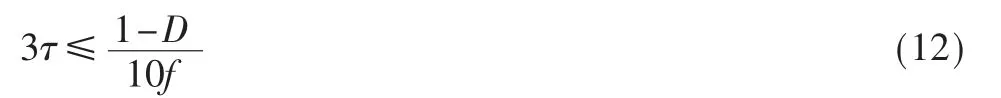

以常用系統電供電為例,Buck 變換器由控制器MPQ8633A 和外圍元件組成,輸入電壓Vin為12 V,輸出電壓UO=0.6 V。Buck 型變換器仿真原理如圖4 所示,原理圖中的Rf和Cf即所述SW-GND 緩沖電路,RBST和CBST即所述BOOST 緩沖電路中的Rboot和Cboot。

圖4 Buck 型變換器仿真原理圖

2.1 Buck 芯片SW-GND 緩沖電路仿真

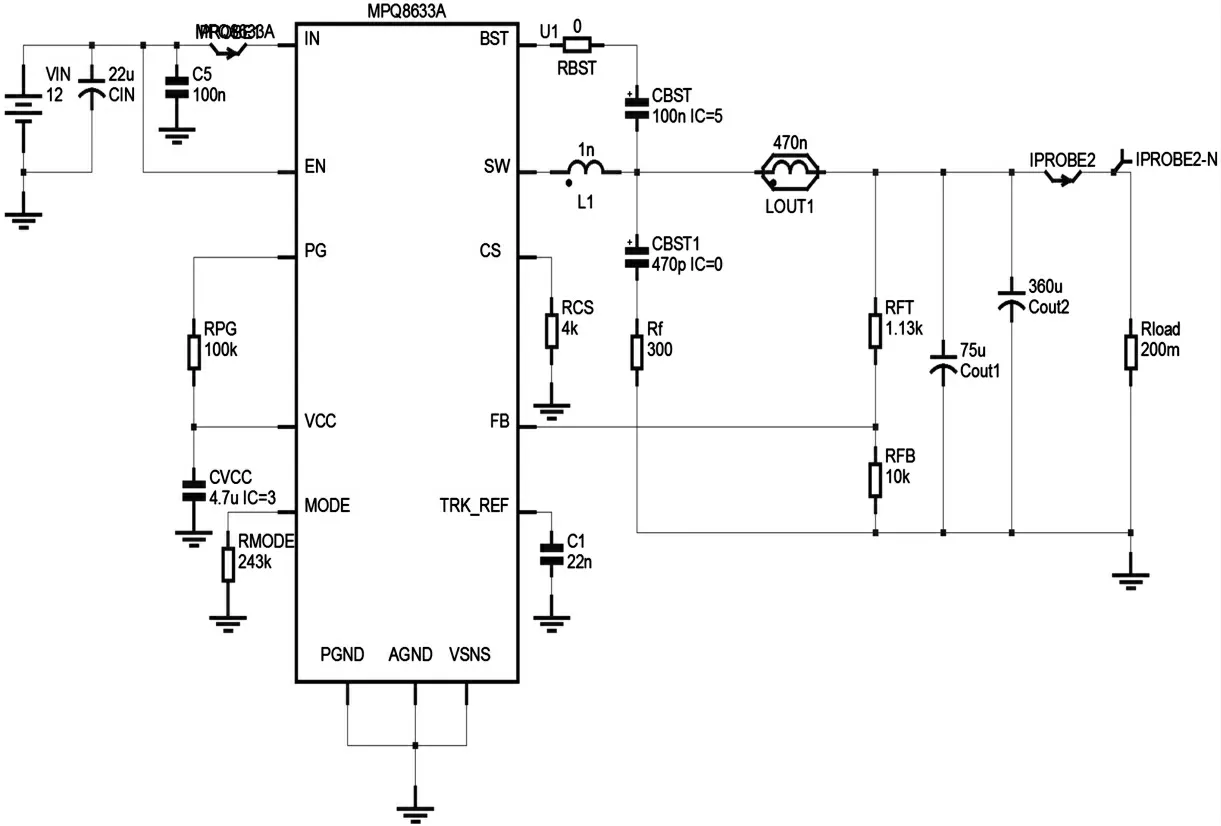

不調整CBST和RBST,仿真觀察不同Rf和Cf對于Phase波形的影響結果如圖5 所示。

圖5 SW-GND 緩沖電路仿真波

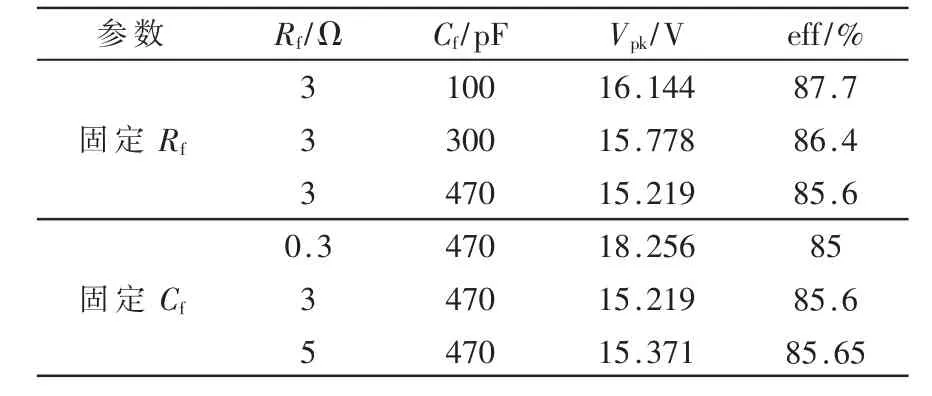

將仿真波形的最大過沖電壓值進行統計,列表比較不同Rf和Cf對于Phase 波形的影響,如表1 所示。其中,VPK是指過沖最高電壓值,eff 是指電源芯片的轉換效率。

表1 SW-GND 緩沖電路仿真

2.2 Buck 芯片BOOST 緩沖電路仿真

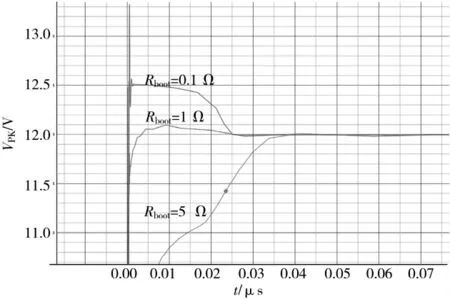

不調整Rf和Cf,仿真觀察不同RBST對于phase 波形過沖的影響,結果如圖6 所示。

圖6 BOOST 緩沖電路仿真波形

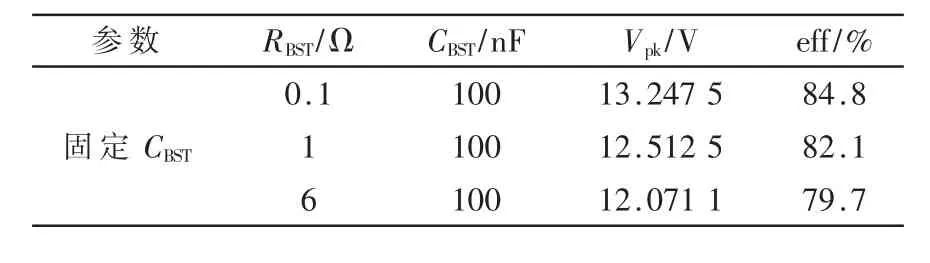

將仿真波形的最大過沖電壓值進行統計,列表比較不同RBST 對于Phase 波形的影響,如表2 所示。

表2 BOOST 緩沖電路仿真

仿真數據說明,針對SW-GND 緩沖電路,Cf越大,越能夠抑制波形的震蕩過沖。Rf過小會使緩沖電路處于欠阻尼狀態,延長震蕩時間,增大過沖;Rf過大會增大濾波頻域阻抗,降低濾波效果,也會增大過沖。緩沖電路能夠影響電源的輸出效率,由于Cf的變化決定了濾波頻段,因此在更大程度上影響了效率,而Rf決定了針對目標頻段的濾波效果。針對BOOST 緩沖電路,增大RBST的阻值能夠延緩MOSFET 的驅動電壓上升速率,從而影響MOSFET 的導通快慢,進而有效優化Phase 電壓過沖。

總的來看,BOOST 緩沖電路能夠更好地降低電壓過沖,但卻產生了不可接受的效率損失。

3 Buck 芯片緩沖電路的實驗

在上述仿真電路參數完全對應的實際PCB 電路板上進行電源測試,根據仿真和前述理論計算,調整Buck電源中的對應器件,測試不同條件下的Phase 波形。

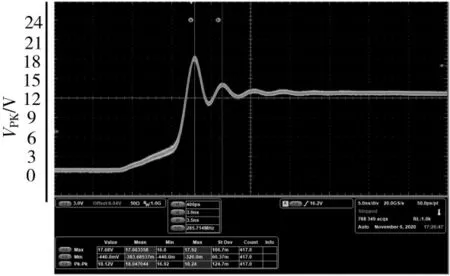

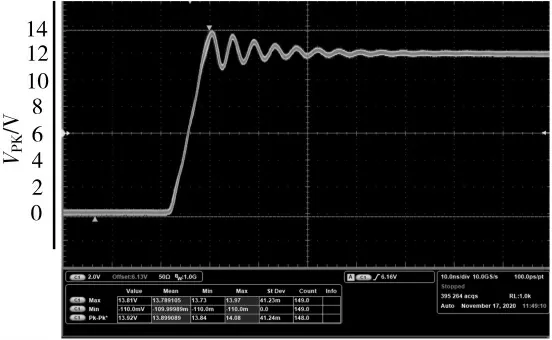

首先測試沒有外部緩沖設計的Phase 波形,并測得效率P1,如圖7 所示。

圖7 無外部緩沖的Phase 波形

加入SW-GND 緩沖電路,Cf=470 pF,Rf=3 Ω,測得波形,并測得效率P2,如圖8 所示。

圖8 SW-GND 緩沖的Phase 波形

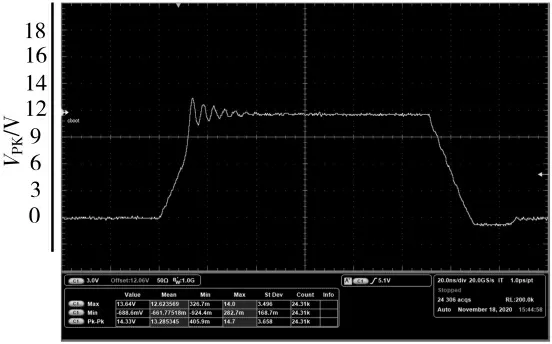

使 用BOOST 緩沖電路,RBST=1 Ω,CBST=0.1 μF,測得波形,并測得效率P3,如圖9 所示。

圖9 BOOST 緩沖的Phase 波形1

更換為RBST=6 Ω,CBST=0.1 μF,測得效率P4,如圖10所示。

圖10 BOOST 緩沖的Phase 波形2

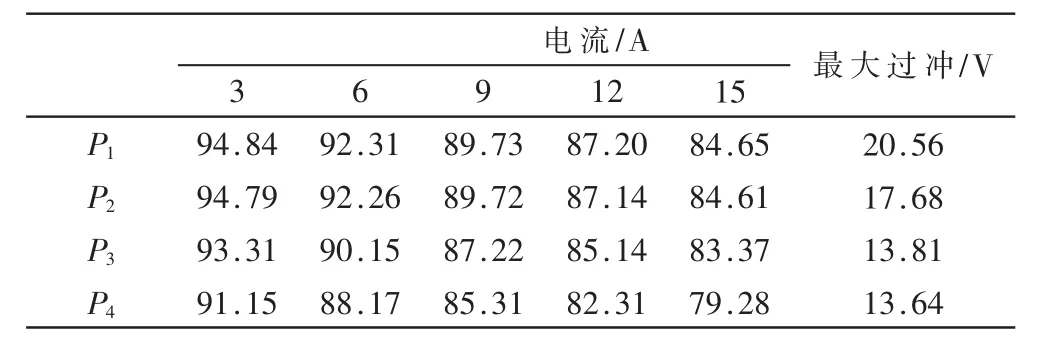

將實測結果的電壓過沖值和不同負載下的電源轉換效率P1、P2、P3、P4列表,如表3 所示。

表3 實際電路板實測

根據實測結果分析,SW-GND 緩沖電路的能夠在一定程度上削弱過沖,BOOST 緩沖電路抑制過沖的能力更強,但是緩沖電路勢必造成效率的損失,如果MOSFET在降額設計下過沖仍然可接受,盡量不要增加任何的緩沖電路以獲得最高的效率。當過沖不滿足MOSFET 的降額設計時,將增加SW-GND 緩沖電路作為首選,BOOST緩沖電路作為次選,這與仿真結論是相符的。

4 結論

本文在理論上推導出兩種緩沖電路的有效性和設計需求,并指出了每種緩沖電路的設計方法,基于緩沖電路對Buck 芯片的效率損失進行仿真分析,綜合比較緩沖性能和效率之間的關系,最后通過實驗驗證仿真分析的可行性。

運用此方法的理論計算,以仿真作為參考依據權衡緩沖效果和效率損失之間的關系,可用于指導Buck 芯片的緩沖電路設計。