專用電源嵌入式控制系統DSP端口問題研究

王偉強,趙楠,宋英利

(核工業理化工程研究院,天津 300180)

隨著嵌入式技術和數字信號處理器(digital signal processor,DSP)技術的不斷發展,DSP在工業領域的應用越來越廣泛。特別是在電源控制技術領域,TMS320F28x系列DSP占據大部分市場份額,其外設接口齊全適合進行電源嵌入式控制系統開發。串行外設接口(serial peripheral interface,SPI)是一種高速、全雙工、同步通信總線,只占用4根線可節約芯片引腳。SPI通信以主從方式進行,必須有一個主設備,可有多個從設備,通過片選信號來控制從設備。

在開發專用電源嵌入式控制系統中選用了美國德州儀器(TI)公司的TMS320F28335 DSP作為控制核心;采用觸摸顯示屏作為人機交互界面,DSP與觸摸顯示屏之間采用SPI通信。

TMS320F28x系列DSP提供了單從設備模式下SPI通信所需的信號。但對多從設備模式,需要通過DSP的通用輸入輸出端口(general-purpose input/output,GPIO)進行片選控制,對從設備進行選通、讀寫控制。

TMS320F28335DSP共有88個GPIO,對應芯片的88個引腳。由于芯片尺寸的限制,這88個引腳都是功能復用的,可根據用戶需要進行靈活編程配置。這88個GPIO分為A,B,C3組,分別對應GPIO0~GPIO31,GPIO32~GPIO63,GPIO64~GPIO87。

本文主要介紹在開發專用電源嵌入式控制系統的過程中發現的TMS320F28335 DSP端口控制存在的問題以及產生問題的條件,即在使用同一分組下的GPIO時,常用的修改GPxDAT寄存器來控制端口讀寫操作的程序指令無法控制兩個及以上端口產生相應動作的問題。針對這個端口控制問題,本文開展了相應研究并提出3種可能引起問題原因的假設并設計了一系列的驗證試驗,進行了逐一的試驗驗證,尋求引起端口控制問題產生的原因。隨后經過綜合分析提出了3種基于軟件編程的解決方案并進行試驗驗證。最后,對常用的TMS320F28x系列另外5種型號DSP進行了拓展驗證試驗,驗證是否存在相似的端口控制問題,以及本文提出的3種解決方案是否可解決這5種型號DSP的端口控制問題。

1 端口問題的發現

1.1 專用電源嵌入式控制系統硬件設計簡介

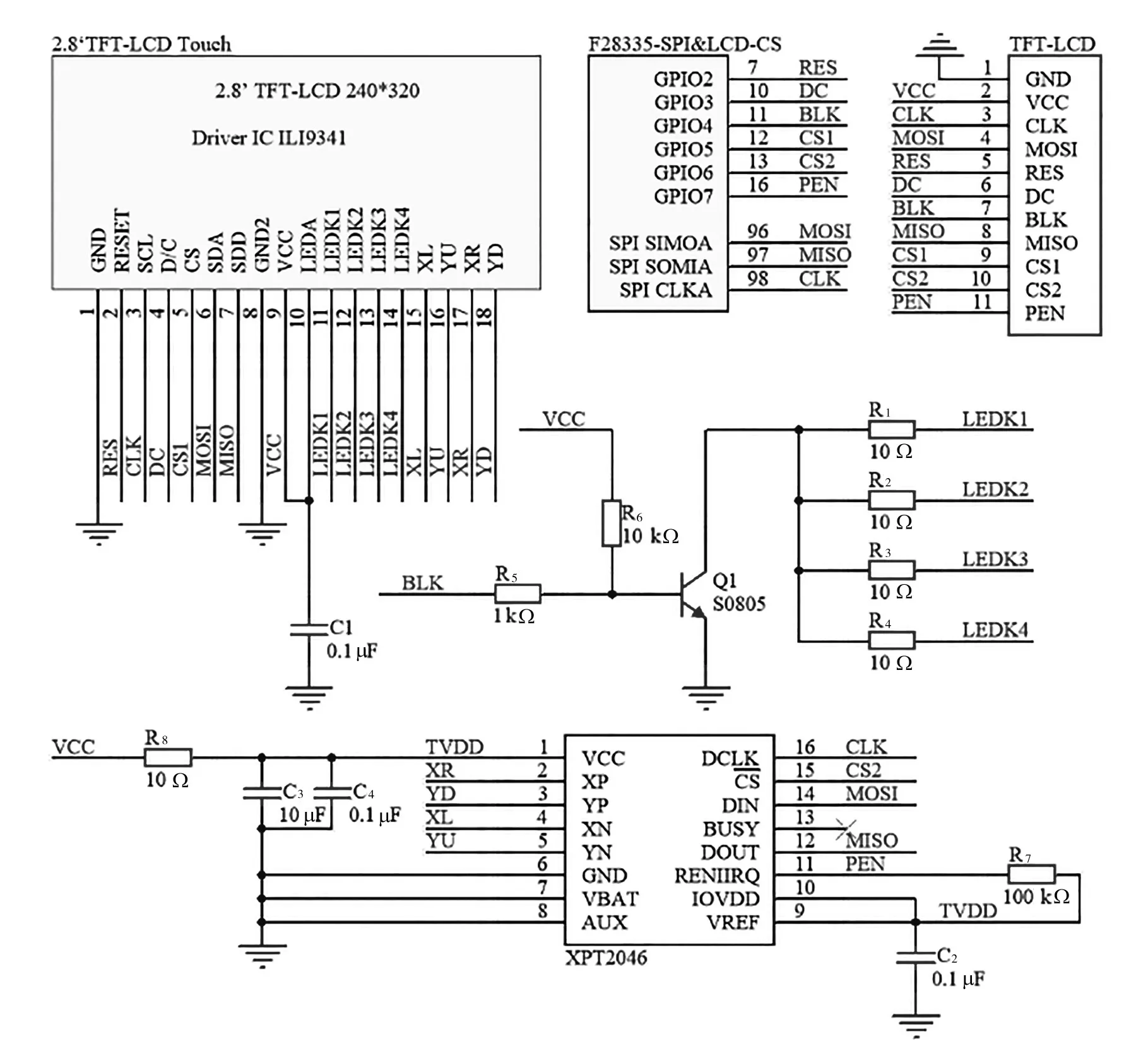

專用電源嵌入式控制系統主要用于專用電源逆變器的控制和核心電量參數的采集傳輸,采用TMS320F28335 DSP作為控制核心開展硬件設計,其系統數據顯示和人機交互接口采用2.8寸配置SPI接口的觸摸顯示屏。將DSP設置為SPI主設備,將觸摸屏上的顯示屏驅動芯片ILI9341和觸摸屏控制芯片XPT2046設置為SPI從設備,實現數據顯示和觸摸控制。DSP與觸摸顯示屏接口硬件原理圖如圖1所示。

圖1 DSP與觸摸顯示屏接口的硬件原理圖Fig.1 Hardware schematic of interface between DSP and touch screen

圖1中使用了DSP的6個GPIO接口作為SPI從設備的控制信號,具體詳見表1。

表1 DSP與觸摸顯示屏控制信號接口Tab.1 Control interface between DSP and touch screen

1.2 調試中發現的問題

按照設計要求編寫觸摸顯示屏部分的程序代碼,走查編譯完成后,下載到DSP中進行調試測試。在調試過程中發現觸摸顯示屏沒有任何反應。

使用示波器觀察DSP的SPI端口波形,發現波形異常,片選引腳CS1和屏幕數據/指令引腳DC波形不正確。反復檢查硬件電路和軟件代碼邏輯關系,并沒有發現問題。同時,在集成開發環境的調試模式下,采取單步執行對程序進行調試,2個片選控制信號波形正確。

1.3 問題復現最小系統搭建和試驗

選用TI公司的TMDSCNCD28335開發板,搭建問題復現最小系統,用于復現上述問題并利用該最小系統作為試驗驗證平臺,尋找產生問題的原因及可行的解決方案。通過綜合分析硬件電路的設計,使用兩個GPIO(GPIO12和GPIO13)模擬SPI屏幕使用的屏幕片選引腳CS1和屏幕數據/指令選擇引腳DC。

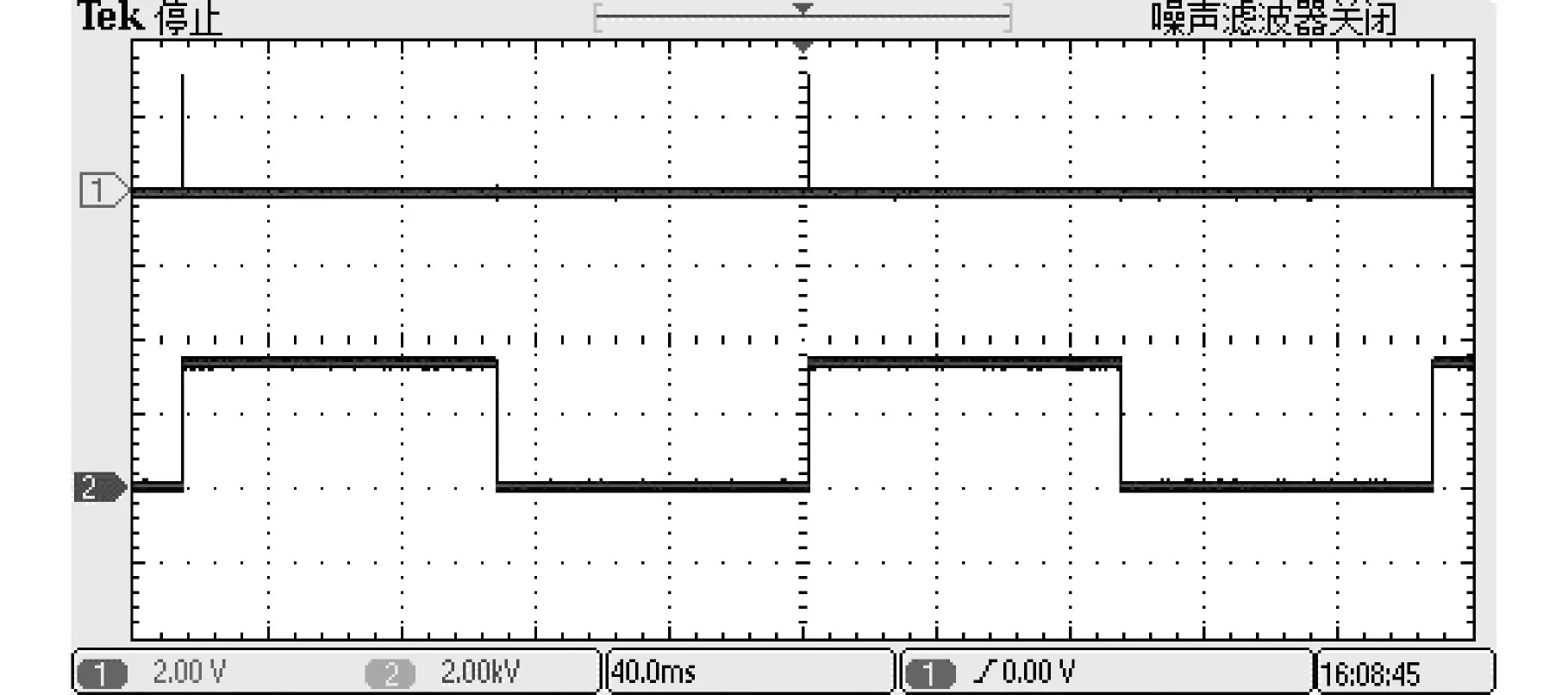

使用同樣GpioDataRegs.GPADAT.bit.GPIOx C語言控制指令語句修改GPxDAT寄存器的值來控制GPIO12和GPIO13端口產生連續高低電平變化。通過示波器捕捉端口波形,試驗波形如圖2所示(圖中上面波形為GPIO12、下面波形為GPIO13試驗波形),可以看到GPIO12端口沒有按照程序指令進行相應的動作,問題被復現。對試驗現象進行總結,得出結論:DSP同一分組下的GPIO端口,通過修改GPxDAT寄存器方式來控制組內的任意2個端口時,會出現上述端口未按照程序指令動作的問題;大部分情況下只有最后一條修改GPxDAT寄存器的控制指令會被正確執行,相應端口會產生電平變化。

圖2 問題復現最小系統試驗示波器波形Fig.2 Waveforms of problem repetition minimum test system

隨后對同一分組內2個以上端口開展了進一步的測試試驗,經試驗發現同樣存在上述同組端口的控制問題。為了簡化分析過程,本文主要針對2個端口的情況進行研究,對這個問題的產生原因做進一步的分析和試驗驗證。

2 端口問題產生原因分析

2.1 端口控制問題初步分析

在圖2中可以看到GPIO12的波形幾乎沒有電平變化,只是在某些位置產生了一些極短的脈沖。根據這一試驗結果分析,在程序代碼執行過程中,使用GpioDataRegs.GPADAT.bit.GPIOx指令語句對同組內端口進行控制,先被執行的控制GPIO12的指令并未使端口產生相應的電平變化,而后面被執行的控制GPIO13的指令可以使端口產生相應的電平變化。

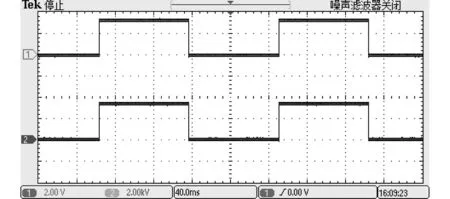

隨后進行了單步執行測試,控制指令語句都能夠使GPIO12產生正確的電平變化。經初步分析該故障可能與CPU執行延遲有一定關系。于是在對應指令語句后插入足夠的延遲,再進行測試研究。示波器波形如圖3所示(圖中上面波形為GPIO12、下面波形為GPIO13試驗波形),此時可以看到GPIO12和GPIO13都產生了正確的電平變化。

圖3 問題復現最小系統增加延遲后試驗示波器波形Fig.3 Waveforms of problem repetition minimum test system after adding delay program

2.2 引起端口控制問題原因的假設提出

綜合分析上面的試驗結果,總結可能引起端口控制問題的原因,在此基礎上提出如下3種假設:

假設一:CPU流水線在處理相同內存讀寫時產生時序安排錯誤,造成第2次指令覆蓋或者掩蓋了第1條指令的執行;

假設二:CPU在該段內存總線上有一定的時序安排錯誤,使第2次讀取修改寫入覆蓋或者掩蓋了第1條指令的讀取修改寫入;

假設三:該寄存器存在一定問題,使第2次讀取修改寫入覆蓋或者掩蓋了第1條指令的讀取修改寫入。

2.3假設一的驗證

如果假設一的條件成立,那么對其它地址的內容進行相似的操作,也會出現一致的現象。使用匯編指令編寫驗證試驗程序,去連續讀取、修改、寫入內存(也稱為靜態隨機存儲器(static random access memory,SRAM))中的某地址的16位內容,并在相應語句處設置斷點。使用集成開發環境中的工具,觀察該地址SRAM中的值。

經過測試試驗,觀察到SRAM中的值是正確的,因此“假設一”不成立。

2.4 假設二的驗證

如果假設二的條件成立,那么對該段內存總線上其它地址的內容進行相似的操作,也會出現一致的現象。使用類似的操作方式,使用匯編指令去連續讀取、修改、寫入GpioCtrlRegs.GPADIR寄存器的內容,并在相應語句后設置斷點,使用集成開發環境中的工具,觀察該寄存器的值。

經過測試試驗發現寄存器的值是正確的,因此“假設二”情況也不成立。

2.5 假設三的驗證

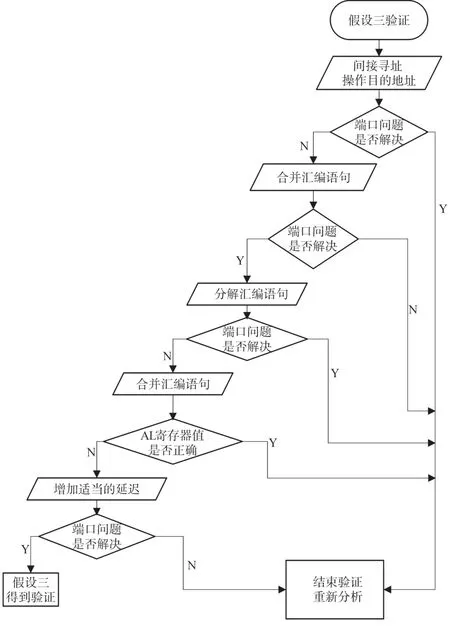

經過上面的驗證試驗研究,排除了前兩種假設。下面針對假設三開展驗證試驗研究,驗證試驗過程比較復雜,驗證流程圖如圖4所示。

圖4 假設三驗證流程圖Fig.4 Verification flow chart of hypothesis 3

首先設計試驗來驗證該寄存器的這種問題是否與尋址方式有關。由于編譯器在默認方式編譯C代碼時,產生了使用DP尋址,OR指令直接操作目的地址的方式進行操作。使用匯編語句實現與C語言控制指令語句相同的功能,采用XARn方式進行間接尋址來操作目的地址。經過測試發現,仍然存在端口控制問題。可以得出結論該寄存器的這種問題與尋址方式并無關聯。

對匯編控制語句進行合并和分解操作,定位存在問題的語句執行位置。

匯編指令語句OR指令本身是讀取、修改、寫入的復合指令。通過合并匯編指令的操作,定位語句執行過程中存在問題的位置。經過測試發現,端口控制問題得到了解決。可以基本確認語句執行的問題可能出現在OR語句的執行中間。

將OR匯編復合指令進行分解,設置合適的斷點并觀察AL寄存器的值,精確定位出現問題的語句執行位置。經過測試發現,AL寄存器的值實際上沒有因為控制指令語句的執行而發生相應的變化,即AL寄存器的值不正確。

通過上述2個測試試驗,定位了出現問題的執行語句位置。在該語句后加入一定數量的“NOP”延遲指令,產生一定時間的延遲。匹配寄存器指令語句執行和硬件變化的時間。從而驗證端口問題是否能得到解決。經過多次測試試驗,在加入5個“NOP”指令語句情況下,寄存器的值正確。

至此,可以判定“假設三”是引起這些問題的原因所在。

2.6 補充驗證試驗和小結

綜合分析總結上面的各項驗證試驗結果可以得出GpioDataRegs.GPxDAT寄存器的值在寫入后需要一定延時才能反應到端口的正確變化。

為了驗證所需的延遲是否與CPU時鐘有關聯,更改CPU的運行時鐘配置,測試使端口控制程序得到正確執行所需要的延遲指令時間,即在程序代碼中加入的最少“NOP”指令數量。試驗結果表明,當改變CPU運行時鐘配置時,所需的延遲指令時間無明顯增加,也就是說所需的延遲時間與CPU時鐘沒有關聯。

將原程序由RAM轉到Flash中執行,并關閉Flash運行加速,由于運行位置的變更使單條代碼的執行周期數發生了變化,CPU執行單條指令所需的時鐘周期將發生變化。測試使端口控制程序得到正確執行所需要的延遲指令時間。測試結果表明,所需的延遲指令時間無明顯變化。

通過分析可以得出GpioDataRegs.GPxDAT寄存器的寫入延遲與CPU運行頻率無關,而是與指令的運行處理器周期數目相關。對該寄存器做修改后,必須經過一定的處理器周期才能夠反應到對應硬件端口上的相應變化。因此,修改該寄存器的值后必須加入足夠的延遲才能夠避免產生端口控制的問題。

3 解決措施及措施驗證

很多嵌入式處理器,尤其是使用精簡指令集的處理器,使用軟件控制GPIO時,操作往往會被分成3步:讀取、修改、寫回。如果這3步是非原子性的,那么由于外部中斷或多線程執行等狀況,處理器不能保證執行結果的正確性,所以很多嵌入式處理器提供專用的SET,CLEAR和TOGGLE寄存器來對GPIO進行控制。由于這些寄存器的讀取無效,只有寫入才生效,因此嵌入式處理器只需要1個寫入指令即可完成對GPIO的控制。不需要預先知道原GPIO狀態,使GPIO的操作保持了原子性。TMS320F28x系列DSP盡管提供了用于原子操作的指令,但由于GpioData-Regs.GPxDAT寄存器修改的延遲,導致連續修改同一寄存器時出現了端口控制問題。因此需要使用GpioDataRegs.GPxSET/CLEAR/TOGGLE寄存器來操作GPIO或者在適當的位置加入一定的延遲指令等待寄存器完成修改,來解決端口控制問題。

根據試驗結果綜合分析研究,提出以下3種基于軟件程序的解決措施方案:

解決措施方案一:在通過位域方式編程修改寄存器GpioDataRegs.GPxDAT的值后須加入足夠的延遲才可避免產生錯誤的執行邏輯。考慮到代碼調試“RAM執行”和實際應用“Flash執行”的差異,可以經測試來驗證需要插入延遲指令的數量來避免邏輯錯誤。

解決措施方案二:當編程連續操作同一個寄存器GpioDataRegs.GPxDAT時,應避免使用位域方式進行操作,而是將多個操作合并到同一條語句操作內完成,這樣可以有效解決端口控制問題。

解決措施方案三:采用GpioDataRegs.GPx-SET/CLEAR/TOGGLE 3個寄存器中的任意一個寄存器的控制方式,代替通過GpioDataRegs.GPx-DAT寄存器進行端口控制的方式,可穩定實現預期功能。

在完成本文上述研究、試驗的基礎上,利用專用電源嵌入式控制系統進行了相應的測試試驗和考核試驗,驗證了以上3種措施方案都可以有效地解決端口控制問題。

嵌入式控制系統對實時性的要求往往較高,對3種措施方案的控制實時性進行分析驗證,這3種措施方案的實時性幾乎是一致的,盡管第1種解決措施方案使用了一定量的“NOP”指令作為延遲函數,但是經過測試該指令使用數量一般低于10個,相當于處理器停滯了10個周期。以TMS320F28335為例,DSP主頻在150 MHz的使用條件下,延遲指令最多會帶來66.6 ns的延遲。在實際的嵌入式控制系統中,直接操作GPIO通常用于“慢速”控制,該延遲對嵌入式控制系統的實時性幾乎不會產生影響。

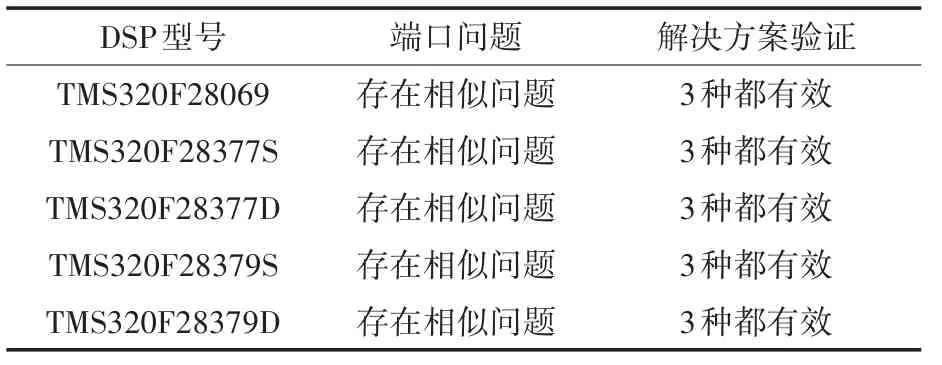

隨后,在TMS320F28x系列其他5種型號的DSP進行了相似問題的測試以及3種解決措施的驗證。主要驗證型號和結果如表2所示。

表2 拓展測試與措施驗證結果Tab.2 Additional testing and measure verification results

如需測試上述型號以外的TMS320F28x系列DSP或者其他系列的嵌入式處理器是否存在本文所述的GPIO端口控制問題,可以采用與本文類似的方法進行端口問題的測試驗證。測試時在測試程序中,以位域方式先給目標芯片的2個同組的GPIO控制寄存器賦值,然后調用延遲函數延遲一定的時間,并以位域方式將相同的2個GPIO控制寄存器賦相反的值,再延遲一定的時間,通過示波器觀察GPIO翻轉波形是否正確。

4 結論

本文通過對專用電源嵌入式控制系統開發過程中遇到的端口控制問題進行復現,經過綜合分析、推測假設與試驗驗證,證明了TMS320F28x系列DSP有部分型號存在GPIO端口控制上的問題,并分析出引起端口控制問題的原因。提出3種可行的解決方案,經測試,這3種方案均可以解決端口控制問題。在今后的使用中,如果硬件資源允許的條件下,在使用GPIO端口做片選控制和輸入輸出端口控制時,應避免將相應端口配置在同一分組下。如果硬件資源不允許,可采用本文提出的3種解決方案對控制軟件程序進行優化。另外,本文只是針對常用的TMS320F28x系列的6種型號DSP進行了測試驗證,今后還需要進一步驗證其他型號的DSP是否存在相似的問題。本文提出的相關研究思路和方法,可以作為分析及解決類似問題的參考。