DSP6x架構(gòu)的嵌入式CPU模擬技術(shù)研究與應(yīng)用

彭琿 張曉娜 張翔 于鑫

【摘要】? ? 首先分析DSP6x架構(gòu)嵌入式CPU的模擬需求,然后研究了DSP6x架構(gòu)的嵌入式CPU模擬器的架構(gòu)設(shè)計(jì)、組成與功能、運(yùn)行流程與接口設(shè)計(jì)等,最后設(shè)計(jì)實(shí)現(xiàn)了基于DSP6x架構(gòu)嵌入式CPU模擬技術(shù)構(gòu)建的嵌入式軟件測(cè)試平臺(tái)。

【關(guān)鍵詞】? ? DSP6x? ? 嵌入式CPU? ? 模擬仿真

引言:

DSP6x系列的CPU是典型的嵌入式系統(tǒng)芯片處理器。該系列CPU采用超長(zhǎng)指令字結(jié)構(gòu),具有易編程性,且編譯性能較好,同時(shí)該CPU上還集成了一些大容量的存儲(chǔ)器,使得應(yīng)用變得非常方便。所以廣泛應(yīng)用于通信導(dǎo)航、彈載星載、航空航天等多種領(lǐng)域的嵌入式裝備設(shè)備中。

本文以典型的DSP6x系列CPU為研究對(duì)象,通過對(duì)DSP6x系列嵌入式CPU內(nèi)核的結(jié)構(gòu)、組成、指令執(zhí)行過程和執(zhí)行時(shí)序的研究分析,介紹了對(duì)DSP6x系列芯片進(jìn)行仿真模擬的總體架構(gòu)、操作流程、指令集模擬執(zhí)行過程等。

一、DSP6x嵌入式CPU原理

1.1典型DSP6x架構(gòu)的CPU分析

典型DSP6x系列DSP包括DSP62x和DSP64x兩個(gè)定點(diǎn)系列和DSP67x一個(gè)浮點(diǎn)系列,其DSP芯片中包括CPU、存儲(chǔ)器及定時(shí)器、串口等外設(shè)。

DSP6x系列DSP含有不同大小的數(shù)據(jù)存儲(chǔ)器。與CPU一樣,DMA控制器(直接存儲(chǔ)訪問)、EMIF接口(外部存儲(chǔ)器接口)和省電邏輯電路等外設(shè),也是DSP必備的組成部分。通用寄存器組一般分為A組和B組。8個(gè)運(yùn)算功能單元的名稱分別為.L1、.L2、.S1、.S2、.M1、.M2、.D1、.D2。內(nèi)核控制寄存器包括AMR、CSR、IFR、ISR、ICR、IER、ISTP、IRP、NRP、PCE1、PC等控制器。控制邏輯是DSP6x處理器內(nèi)核各種運(yùn)行時(shí)序控制的單元。測(cè)試和仿真是接仿真器的接口。中斷是DSP6x處理器的中斷處理模塊。

1.2典型DSP6x架構(gòu)CPU原理分析

DSP6x系列CPU的總線分為兩種:程序總線和數(shù)據(jù)總線。程序總線主要負(fù)責(zé)將存儲(chǔ)在CPU芯片程序存儲(chǔ)器中的指令,傳送至CPU芯片的執(zhí)行器執(zhí)行。程序總線寬度為256位,一次取指操作是同時(shí)取8條指令,將8條指令同時(shí)通過程序總線傳遞給CPU執(zhí)行器。在執(zhí)行器上執(zhí)行時(shí),每條指令都獨(dú)占一個(gè)操作單元。取指、分配和譯碼三個(gè)指令操作,都可在一個(gè)CPU周期內(nèi)讀取并傳遞8條(32位)指令。這些指令的操作方式都是由控制寄存器組進(jìn)行控制。從在程序存儲(chǔ)器中讀取第一個(gè)取值指令包起,一個(gè)超長(zhǎng)指令字的處理流程就開始了。

DSP6x系列CPU芯片外存儲(chǔ)器及芯片外總線都是不區(qū)分程序和數(shù)據(jù)的。CPU芯片所有存儲(chǔ)器(內(nèi)部和外部的程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器),都是按字節(jié)進(jìn)行統(tǒng)一編址的。無論是讀外部指令或者對(duì)外交換數(shù)據(jù),CPU都需要通過DMA和EMIF。但CPU內(nèi)部交換數(shù)據(jù)時(shí)使用數(shù)據(jù)總線,在取指令時(shí)才使用程序總線。

與指令執(zhí)行相關(guān)的主要包括數(shù)據(jù)通路和控制寄存器。數(shù)據(jù)通路一般包括執(zhí)行指令的功能單元、通用寄存器組和數(shù)據(jù)總線。DSP6x系列CPU有兩個(gè)類似的數(shù)據(jù)通路,每個(gè)數(shù)據(jù)通路都有4個(gè)功能單元和1組通用寄存器。4個(gè)功能單元執(zhí)行指令的操作,所有算術(shù)邏輯運(yùn)算指令(除讀、存儲(chǔ)及轉(zhuǎn)移指令外)的源操作數(shù)和目的操作數(shù)都放在通用寄存器中,這樣指令運(yùn)算的速度就更快。CPU一般使用讀指令和存儲(chǔ)指令在通用寄存器組與片內(nèi)存儲(chǔ)器間進(jìn)行數(shù)據(jù)交換,在進(jìn)行數(shù)據(jù)交換時(shí),由兩個(gè)指令的數(shù)據(jù)尋址單元提供數(shù)據(jù)存儲(chǔ)的地址。

1.3指令執(zhí)行過程分析

DSP6x系列CPU的指令執(zhí)行過程都是按3級(jí)流水線模式。流水線的每一級(jí)由不同數(shù)量的執(zhí)行節(jié)拍組成。一般“取指”級(jí)有4個(gè)節(jié)拍;“譯碼”級(jí)有2個(gè)節(jié)拍;“執(zhí)行”級(jí)執(zhí)行節(jié)拍數(shù)不是固定的,不同指令有不同的節(jié)拍數(shù)。每個(gè)指令執(zhí)行的節(jié)拍數(shù)量的差別主要在“執(zhí)行”級(jí)。

“取指”指令的4個(gè)節(jié)拍分別是:PG、PS、PW、PR。“譯碼”指令的2個(gè)節(jié)拍分別是:DP和DC。在“譯碼”級(jí)中,在DP節(jié)拍期間,1個(gè)取值包的8條指令可根據(jù)并行執(zhí)行的需要,分成若干個(gè)執(zhí)行包。

在“執(zhí)行”指令中,定點(diǎn)計(jì)算和浮點(diǎn)計(jì)算的所占的流水線節(jié)拍數(shù)量是不同的,前者最多占5個(gè)節(jié)拍,而后者最多則可占有10個(gè)節(jié)拍。

二、DSP6x嵌入式CPU模擬器總體設(shè)計(jì)

2.1架構(gòu)設(shè)計(jì)

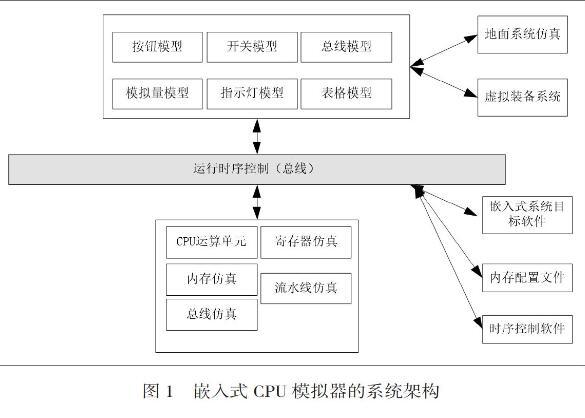

嵌入式CPU模擬器在設(shè)計(jì)上采用模塊化的結(jié)構(gòu)設(shè)計(jì)。其系統(tǒng)架構(gòu)設(shè)計(jì)如圖1所示。

從DSP6x的體系架構(gòu)上來分析,DSP62x、DSP64x和DSP67x的體系結(jié)構(gòu)是一致的,包括處理器流水線、算術(shù)運(yùn)算單元、內(nèi)存、寄存器等。在設(shè)計(jì)時(shí),采用向下兼容的模式,DSP67x兼容DSP64x,DSP64x又兼容dsp62x。

2.2組成與功能

嵌入式CPU模擬器主要由目標(biāo)碼文件解析、內(nèi)存模擬、指令集模擬解析、算術(shù)運(yùn)算單元模擬、總線模擬、流水線模擬、寄存器模擬、外設(shè)接口仿真等功能模塊組成。

1.目標(biāo)碼文件解析

DSP6x處理器的目標(biāo)碼格式為COFF文件格式。模擬器讀取目標(biāo)碼文件中的數(shù)據(jù)到模擬器仿真內(nèi)存中,讀取的數(shù)據(jù)包括代碼段的數(shù)據(jù)、數(shù)據(jù)段的數(shù)據(jù)、向量表段的數(shù)據(jù)等。

2.內(nèi)存模擬

按照DSP6x處理器的內(nèi)存分布來動(dòng)態(tài)創(chuàng)建內(nèi)存空間。

3.指令集模擬解析

模擬器模擬DSP6x系列的180多條指令,包括存儲(chǔ)類、算術(shù)類、邏輯類、搬移類、程序轉(zhuǎn)移類等類別的指令。模擬解析每種類別的指令在不同的運(yùn)算功能單元上運(yùn)行。

4.算術(shù)運(yùn)算單元模擬

模擬器模擬DSP6x架構(gòu)CPU的6個(gè)算術(shù)運(yùn)算單元ALU、2個(gè)乘法器和1個(gè)地址產(chǎn)生器等。模擬這6個(gè)算術(shù)運(yùn)算單元ALU和2個(gè)乘法器在1個(gè)CPU周期內(nèi)同時(shí)執(zhí)行8條指令的運(yùn)算過程。

5.寄存器模擬

模擬器模擬DSP6x處理器的A和B兩個(gè)通用寄存器組,以及通用內(nèi)核寄存器。模擬其利用通用接口函數(shù),對(duì)通用寄存器組和特殊功能寄存器進(jìn)行訪問和位操作的運(yùn)行過程。

6.總線模擬

模擬器模擬DSP6x處理器的程序總線和數(shù)據(jù)總線。模擬總線的位數(shù)為32位。程序總線和數(shù)據(jù)總線運(yùn)行過程采用并行模擬的技術(shù)進(jìn)行模擬。

7.流水線模擬

模擬器模擬DSP6x的“取指、譯碼、執(zhí)行”3級(jí)流水線的工作過程,并根據(jù)3級(jí)流水線各級(jí)的實(shí)際工作節(jié)拍,模擬指令在各級(jí)的CPU工作節(jié)拍。

8.外設(shè)接口仿真

模擬器模擬外設(shè)接口。在外設(shè)接口模塊中,包含接口仿真所需要的接口函數(shù)以及時(shí)序控制與調(diào)度模塊,來完成外設(shè)仿真的實(shí)時(shí)性。

2.3 運(yùn)行流程設(shè)計(jì)

在嵌入式CPU模擬器運(yùn)行流程中,首先導(dǎo)入源代碼進(jìn)行交叉編譯,交叉編譯器編譯后的二進(jìn)制目標(biāo)碼導(dǎo)入到嵌入式CPU模擬內(nèi)存中,然后通過嵌入式代碼指令集執(zhí)行。在執(zhí)行過程中,當(dāng)訪問特定端口地址時(shí),響應(yīng)綁定的外設(shè)仿真函數(shù),最后外設(shè)仿真函數(shù)的接口數(shù)據(jù)源與仿真測(cè)試環(huán)境構(gòu)建進(jìn)行數(shù)據(jù)交互,完成整個(gè)嵌入式軟件測(cè)試的運(yùn)行流程。

2.4外部接口設(shè)計(jì)

在嵌入式軟件外部接口中,嵌入式CPU模擬器與外設(shè)接口的訪問都是通過外部接口寄存器進(jìn)行的,每個(gè)外部接口的寄存器與具體地址空間一一對(duì)應(yīng)。訪問外部接口寄存器,就是訪問特殊的地址空間。通過設(shè)定地址空間綁定函數(shù),關(guān)聯(lián)外設(shè)與外設(shè)仿真接口函數(shù),實(shí)現(xiàn)外部接口仿真。

根據(jù)上述嵌入式軟件外部接口仿真過程,設(shè)計(jì)外部初始化接口和外部參考時(shí)鐘接口。在外部初始化接口中,根據(jù)外設(shè)寄存器的端口地址,把外設(shè)關(guān)聯(lián)到相應(yīng)的外設(shè)仿真函數(shù)中,實(shí)現(xiàn)IO、AD/DA、串口、CAN、1553B等外設(shè)與仿真外設(shè)庫的關(guān)聯(lián)。外部參考時(shí)鐘實(shí)現(xiàn)外部接口設(shè)備的時(shí)序仿真與控制。寄存器讀寫接口實(shí)現(xiàn)相關(guān)的內(nèi)存、寄存器的讀寫功能。

在嵌入式軟件外部接口中,還設(shè)計(jì)了寄存器讀寫接口、內(nèi)存讀寫接口、中斷事件觸發(fā)接口、數(shù)據(jù)傳遞接口、內(nèi)核處理器的控制接口等。內(nèi)核處理器的控制接口包括啟動(dòng)接口、停止接口、繼續(xù)執(zhí)行接口和復(fù)位接口。

三、結(jié)束語

在通用計(jì)算機(jī)平臺(tái)上,模擬并運(yùn)行嵌入式軟件,是提高嵌入式軟件開發(fā)與測(cè)試效率的通用方法,不同嵌入式系統(tǒng)模擬的技術(shù)不同,但是關(guān)鍵技術(shù)都是嵌入式CPU對(duì)指令執(zhí)行過程的模擬。本文重點(diǎn)研究了嵌入式CPU模擬的技術(shù)方案,限于篇幅的限制,其具體實(shí)現(xiàn)的細(xì)節(jié)這里就不再類似。有興趣的讀者可以查閱本作者其他類似論文。

參? 考? 文? 獻(xiàn)

[1]蔡建平,關(guān)于嵌入式應(yīng)用開發(fā)技術(shù) 單片機(jī)與嵌入式系統(tǒng)應(yīng)用 2001年第1期

[2](美)奧沙納(Oshana,R),(美)雷林(Kraeling,M.)主編;單波等譯.嵌入式系統(tǒng)軟件工程:方法、實(shí)用技術(shù)及應(yīng)用[M].北京:清華大學(xué)出版社,2016

[3](美)施部.克.威(V,S.K.)著,伍微譯.嵌入式系統(tǒng)原理、設(shè)計(jì)及開發(fā)[M].北京:清華大學(xué)出版社,2012

[4]文玉亮(導(dǎo)師:宋彬)H.264編碼算法的DSP優(yōu)化與實(shí)現(xiàn),《西安電子科技大學(xué)碩士論文》—2008-01-01

[5]董培(導(dǎo)師:沈玉蓀)H.264編碼器在DSP和智能手機(jī)平臺(tái)上的優(yōu)化實(shí)現(xiàn),《北京工業(yè)大學(xué)碩士論文》—2008-03-01