氣墊船縱橫傾信號處理電路測試性設計及BIT實現

王國書,劉桂峰,吳杰長,陳 軍

(海軍工程大學 動力工程學院,武漢 430033)

1 引言

氣墊船航態特殊,高速航行時船體處于墊升狀態,整船無水下操縱部件,槳舵控制系統形成控制信號作用于空氣舵、射流舵、變距槳等實現對船體姿態的控制。受海上工作環境影響,極易發生故障,且該電路的故障檢測與定位比較困難,為此,本文以縱橫傾信號處理電路為例,開展測試性設計與自測試電路設計工作。

測試性也稱“可測性”,是指裝備能夠及時、準確確定其工作狀態,并有效隔離內部故障的一種設計特性,最早在1975年由F.Liour提出[1],目前廣泛應用于武器裝備、電子系統的總體優化和設計改進[2]。國內對測試性工作的研究應用非常廣泛,文獻[3-7]分別對慣性組合、雙饋風力發電機、自動裝彈機、雷達裝備等開展測試性研究工作,通過建模、分析與改進,取得較好的故障檢測與隔離效果。但以上研究均未考慮對某些關鍵部件的自測試問題,一些測試需在系統停機或者占用部分系統資源的基礎上進行。為此,本文首先對縱橫傾信號處理電路進行測試性建模與分析,在此基礎上,設計自測試(built-in test,BIT)電路,通過BIT裝置以實時監測、診斷的方式,實現測試性模型中部分關鍵測試項目,故障發生時BIT主動測試并將故障信號發送至上位機,從而提高電路的可靠性與可測性。

2 縱橫傾信號處理電路測試性建模

2.1 多信號建模方法

多信號模型是美國康涅狄格大學的Pattipati和Deb[8]等在研究定量、定性、結構以及信息流模型基礎上,于1994年提出的測試性建模方法,本質上是一種有向圖模型,以系統結構框圖為基礎,通過標明功能信號流方向和各組成單元之間的相互連接關系并為其標注測試點的位置,并在測試點上添加相應的測試項目來建立模型[5]。建立多信號模型的一般步驟如下:

① 結合裝備實際結構,對建模主體進行功能層次劃分;② 根據裝備中信號流向關系,繪制多信號有向圖,添加測試點與測試,并為測試關聯故障模式;③ 開展測試性分析,根據測試報告對模型進行修改[9]。

2.2 縱橫傾信號處理電路測試性建模

2.2.1縱橫傾信號處理電路組成及功能分析

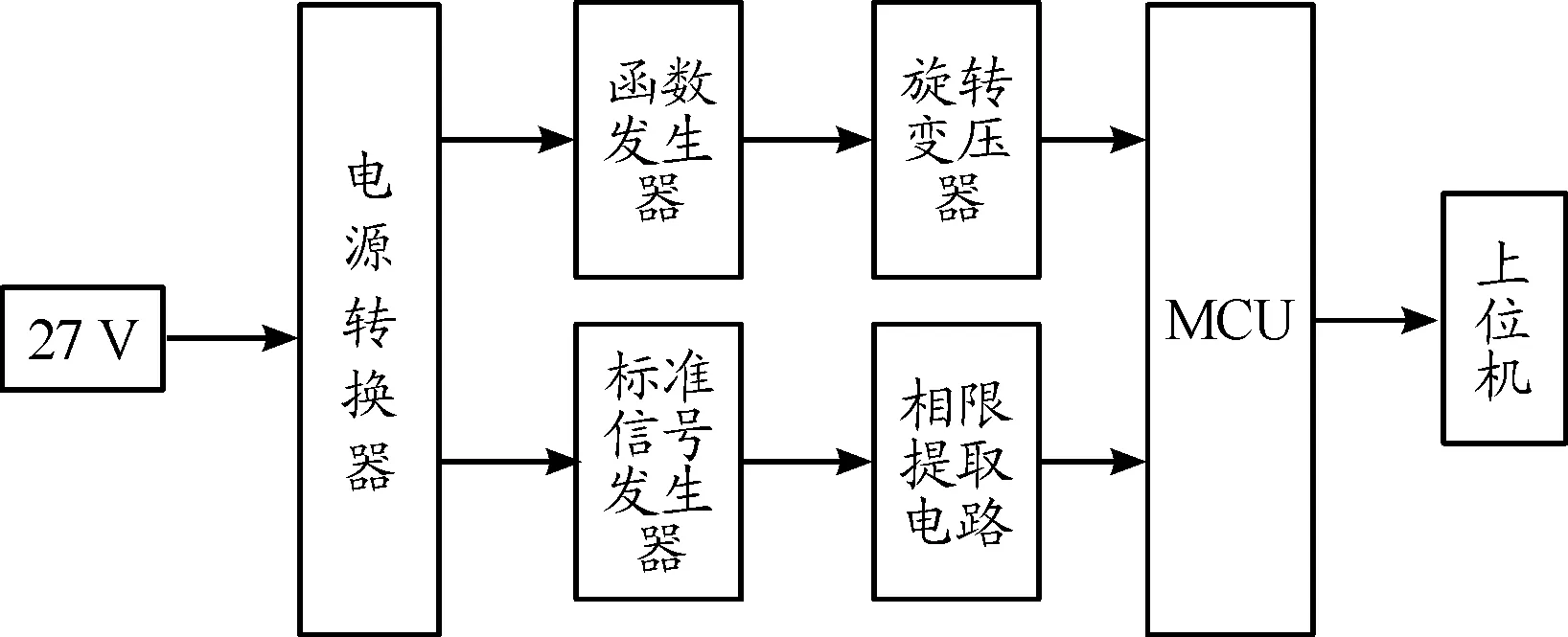

縱橫傾信號處理電路主要包括電源轉換器、函數發生器、旋轉變壓器、標準信號發生器、相限提取電路和MCU,除此之外,還包括運放器1、2和放大器,電路內部總體結構如圖1所示。

圖1 信號處理電路內部總體結構框圖

電源轉換器(s1,s2):將27 V DC電源轉換成±15 V DC,實現供電轉換,并保護系統免受供電電源中噪聲與電壓波動的干擾;

函數發生器(s3):通過控制電容充放電產生KSinωt交流信號;

旋轉變壓器(s4):位于縱橫傾信號傳感器內部,通過轉子角位移改變原、副邊繞組接觸面產生幅值不同于輸入原交流信號的KSin(ωt+a)Sinθ信號;

標準信號發生器(s5):產生標準信號;

相限提取電路(s6):用于比較標準信號發生器與旋轉變壓器的電信號,計算KSin(ωt+a)Sinθ與KSinωt的相位差,得到縱橫傾的“正負值”;

MCU(s7):對KSin(ωt+a)Sinθ交流電進行幅值計算,并將幅值與相限提取電路得到的正負值一道發送至上級PLC工控機。

運放器1、2與放大器:對電信號進行放大。

2.2.2多信號模型的構建

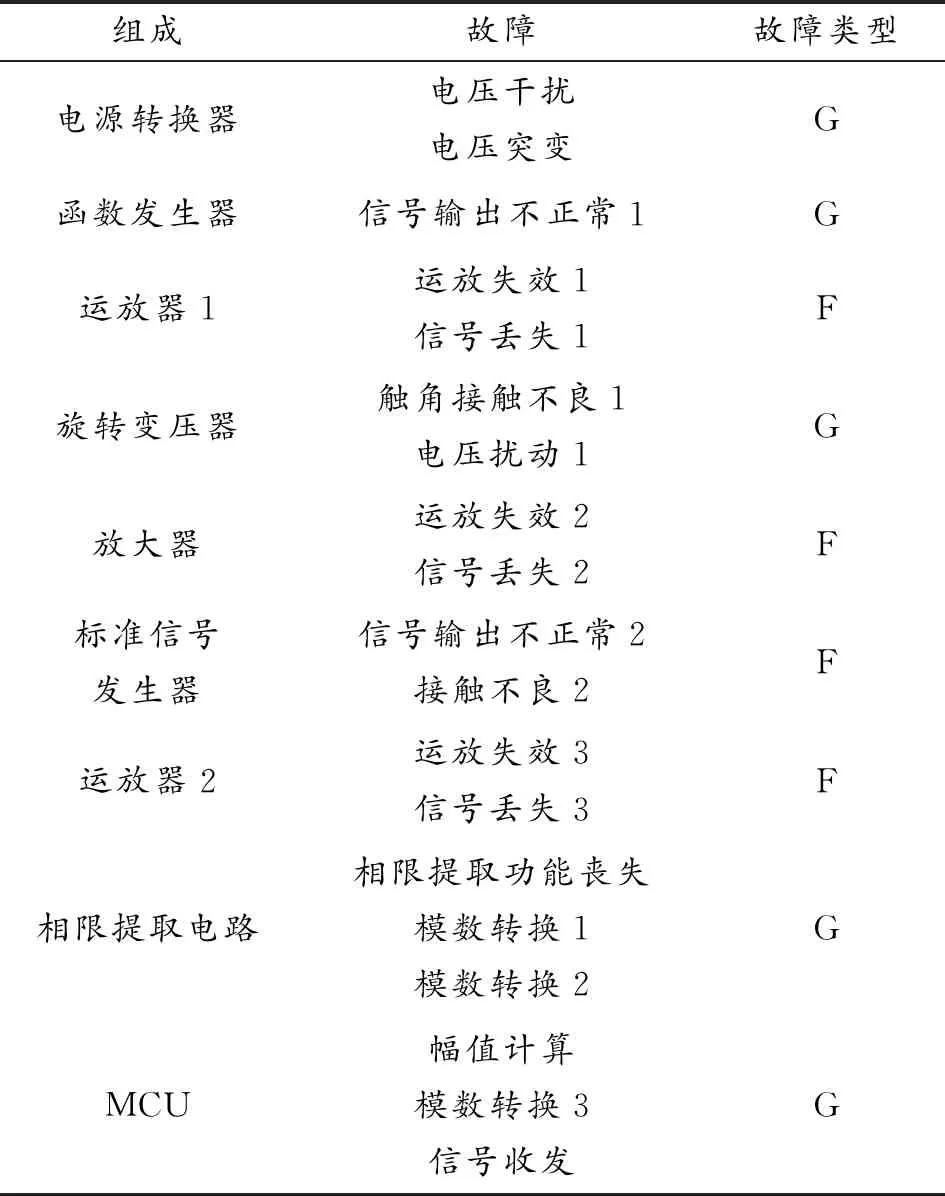

基于2.2.1中對信號處理電路功能結構分解,包含的功能結構都可能會產生故障,可以是功能性故障F也可能是全局性故障G,接下來定義各組成部分常見故障模式,具體如表1所示。

表1 故障模式清單

針對以上故障,為其設置測試項目:t1:DC/DC電源轉換裝置±15V DC電壓測試;t2:DC/AC模塊(函數發生器)60V AC電壓測試;t3:運放器1輸出電壓測試;t4:旋轉變壓器輸出電壓測試;t5:標準信號發生器輸出電壓測試;t6:運放器2輸出電壓測試;t7:相限提取電路輸出信號測試;t8:放大器放大信號測試;t9:MCU輸出信號測試。

該模塊的測試點為TP1~TP6,每個測試點對應的測試分別為:ST(TP1)={t1};ST(TP2)={t3,t5};ST(TP3)={t1};ST(TP4)={t2};ST(TP5)={t8,t9};ST(TP6)={t4,t6,t7}。

利用TEAMS建模軟件對其建模結果如圖2所示。

圖2 信號轉換模塊多信號模型示意圖

2.3 測試性分析

2.3.1靜態分析與測試性預計

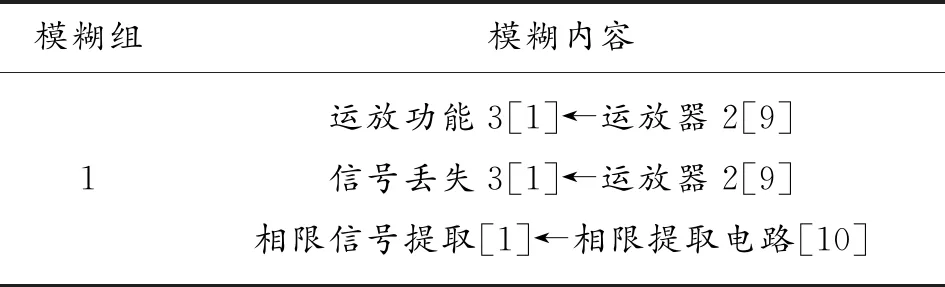

首先對其進行靜態分析,發現不存在冗余測試和未檢測故障,但是存在一組模糊組,如表2所示。

表2 模糊組清單

由表2看出,出現上述3種故障時,故障源可能在運放器2或者相限提取電路,維修時需逐個檢測,導致效率低、耗時長,同時延長了停機時間。

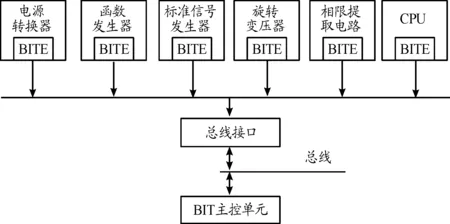

根據對FDR和FIR指標進行預計報告,發現針對本次研究所定義故障的檢測率達到了100%,但是故障隔離率為88.89%,低于規定的測試性指標,故障模糊數組為1.17。測試性預計總體報告如圖3所示。

圖3 測試性預計總體報告截圖

2.3.2測試性改進

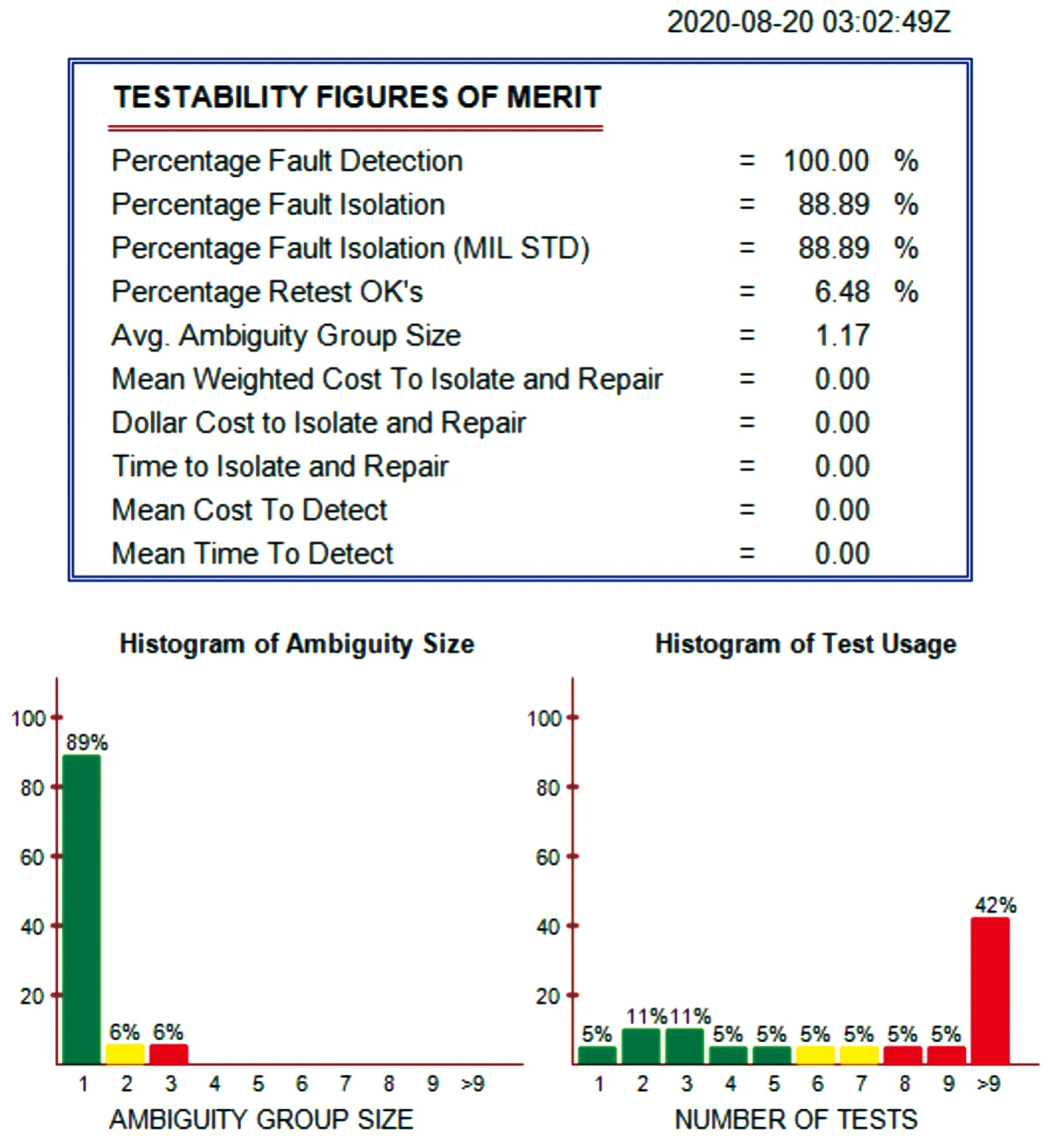

根據模糊組清單,以添加測試點或測試的方式,提高故障檢測與故障隔離能力。

添加的測試點和測試位于運放器2輸出端。

對其測試性參數預計報告如圖4所示,針對本次研究定義的故障,其檢測率、隔離率均達到100%,并且故障模糊組為1,不存在冗余測試與未覆蓋故障。說明在添加測試點與測試后,信號處理電路測試性能力顯著提高。

圖4 改進后測試性報告截圖

3 測試項目的BIT設計

3.1 BIT技術

機內測試也稱為機內自檢測,我國國軍標將其定義為:系統或設備內部提供的檢測和隔離故障的自動測試能力。BIT設計的目的在于,通過設置用于狀態監控、故障檢測與隔離的自檢裝置或者軟件、硬件來使裝備具有良好的測試性,使裝備本身就能夠進行自檢工作,檢查工作是否正常或者確定出哪一部位發生了故障[10-14]。

在對BIT進行設計時,首先要明確BIT設計要求及其分類關系,根據實際需要選擇合適的BIT類型[15]。BIT具體分類方法有很多,按照一般論述,BIT按實現方式分為硬件BIT和軟件BIT;按照工作方式可分為工作前、工作中、工作后BIT;按照組成結構分為分布式BIT和集中式BIT[2]。

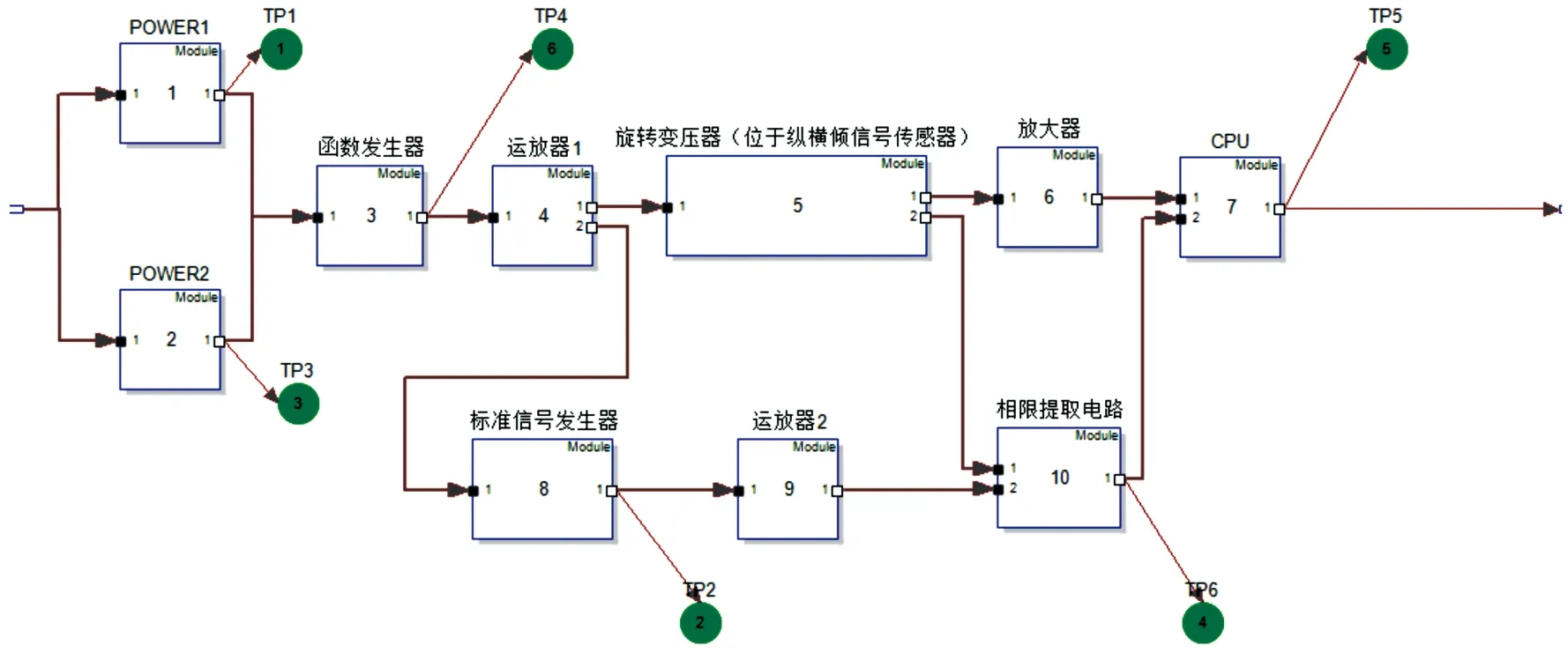

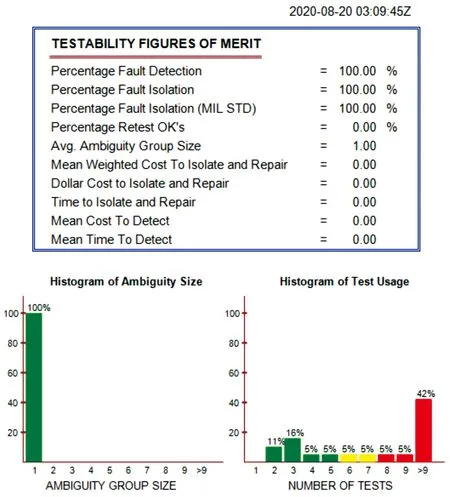

本文設計中采用集中-分布式結構,將主控單元的軟件優勢與BIT裝置的硬件優勢結合起來,具體來說:主控單元可采用軟件或者軟硬件結合的方式,實現測試的功能,很大程度上減少了硬件電路的配置,避免過度占用系統內部資源;針對各功能結構設置獨立的BIT裝置,可以實現對故障的精確定位,減少故障檢測時間,提高故障維修效率,從而提高裝備系統的測試性水平[16]。圖5表示了縱橫傾信號處理電路BIT總體結構示意圖。

圖5 縱橫傾信號處理電路BIT總體結構框圖

3.2 BIT電路設計

根據上文對電路的分析,27 V DC輸入電源在電源轉換器(s1,s2)處理后輸出為±15 V DC,實際電路存在某些電子元器件比較“脆弱”,電源轉換器輸出過壓會導致組件中“脆弱”元件“燒壞”,輸出過低則達不到組件中部分關鍵元件工作電壓從而使組件無法正常工作,該情況下發生全局性故障G;函數發生器s3工作正常是后續“相限提取”與“幅值計算”基礎,發生故障會影響整個模塊功能;標準信號發生器本身可靠性很高,對其進行BIT電路設計會占用其部分資源,影響其工作可靠性;相限提取電路與MCU實現功能相似,所以本文以下針對電源轉換器、函數發生器、運放器2和相限提取電路進行BIT電路設計,實現其自測試功能。

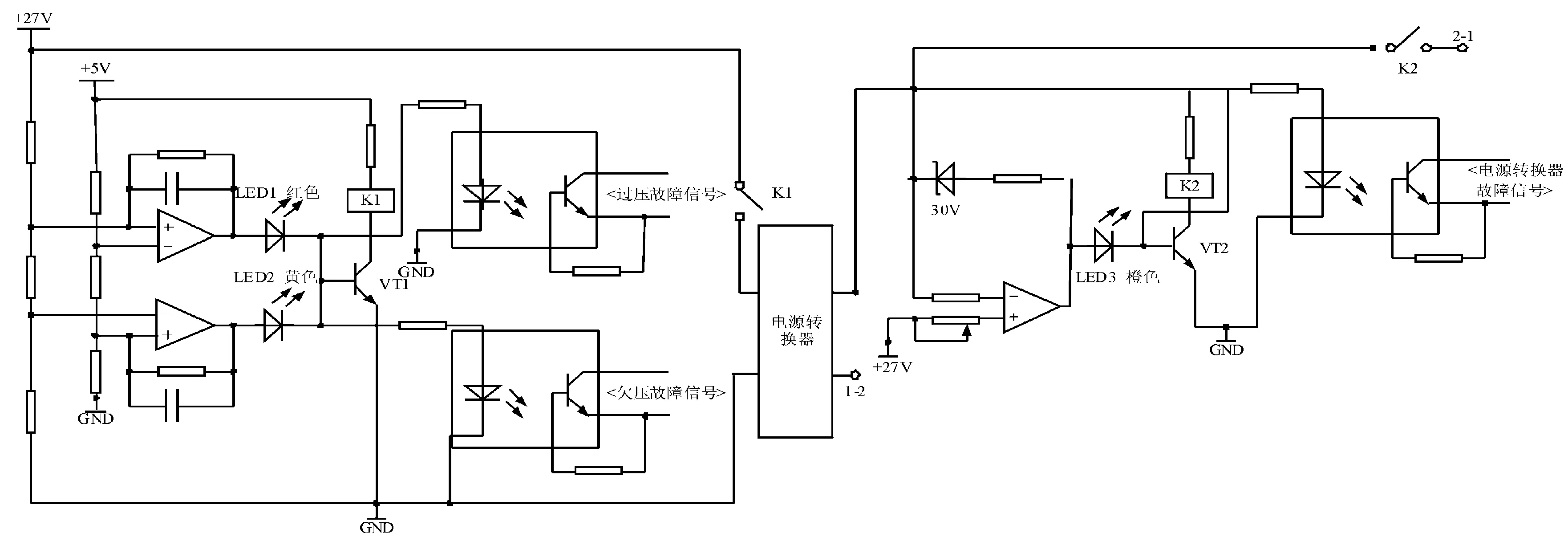

3.2.1電源轉換模塊自測試電路

針對電源轉換器設置工作中硬件BIT,對電源轉換模塊設置輸入電壓和輸出電壓的檢測,分別保護電源轉換器和內部電路。在系統開機時自動執行測試項目,上下電壓比較器分別作為電壓過高或過低時的門限,過壓時,上電壓比較器輸出高電平,發光二極管導通,三極管基極獲高電平導通,繼電器K1動作,使開關斷開,同時光耦向BIT主控單元發出過壓故障信號。低電平時工作原理與此相同。圖6電源轉換器左側為具體電路設計。

圖6電源轉換器右側為輸出端口自測試電路,功能為對輸出±15 V AC的檢測,穩壓二極管負責對過壓的檢測,輸出電壓超過30 V自動導通,LED3亮,VT2基極獲得高電壓并導通,從而線圈通電使K2斷開,光耦向BIT主控單元發送“電源轉換器故障信號”;欠壓保護電路與輸入端口BIT工作原理類似,將通過輸入端口BIT自測試的電信號作為比較基準,與輸出電壓做比較。

圖6 電源轉換器自測試電路圖

電源轉換器有輸出信號,證明輸入27V通過了輸入端口的自測試,在合理范圍內,電源轉換器輸出信號超出正常范圍,說明是轉換器本身出現故障。

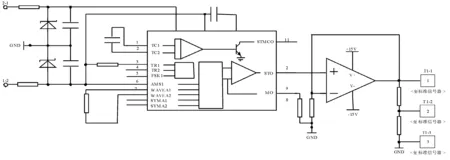

3.2.2函數發生器內建自測試電路

函數發生器3個輸出端口輸出400 Hz的交流信號,拾取輸出端3輸出交流信號,圖7為函數發生器電路原理框圖,通過集中-分布式BIT實現對交流信號頻率和峰值的檢測,設計方法為將3腳輸出接入單穩態觸發電路,實現對正弦脈沖的整流,輸出方波進入BIT主控單元,通過程序編譯,對頻率進行計算;3腳接入峰值檢波電路,并在輸出端設置電壓比較器,原理類似于圖6,由供電27 V電壓作為基準,對幅值進行監測、比較,當高于/低于規定幅值,相應,光耦導通,故障信號上傳至上位機。

圖7 函數信號發生器原理框圖

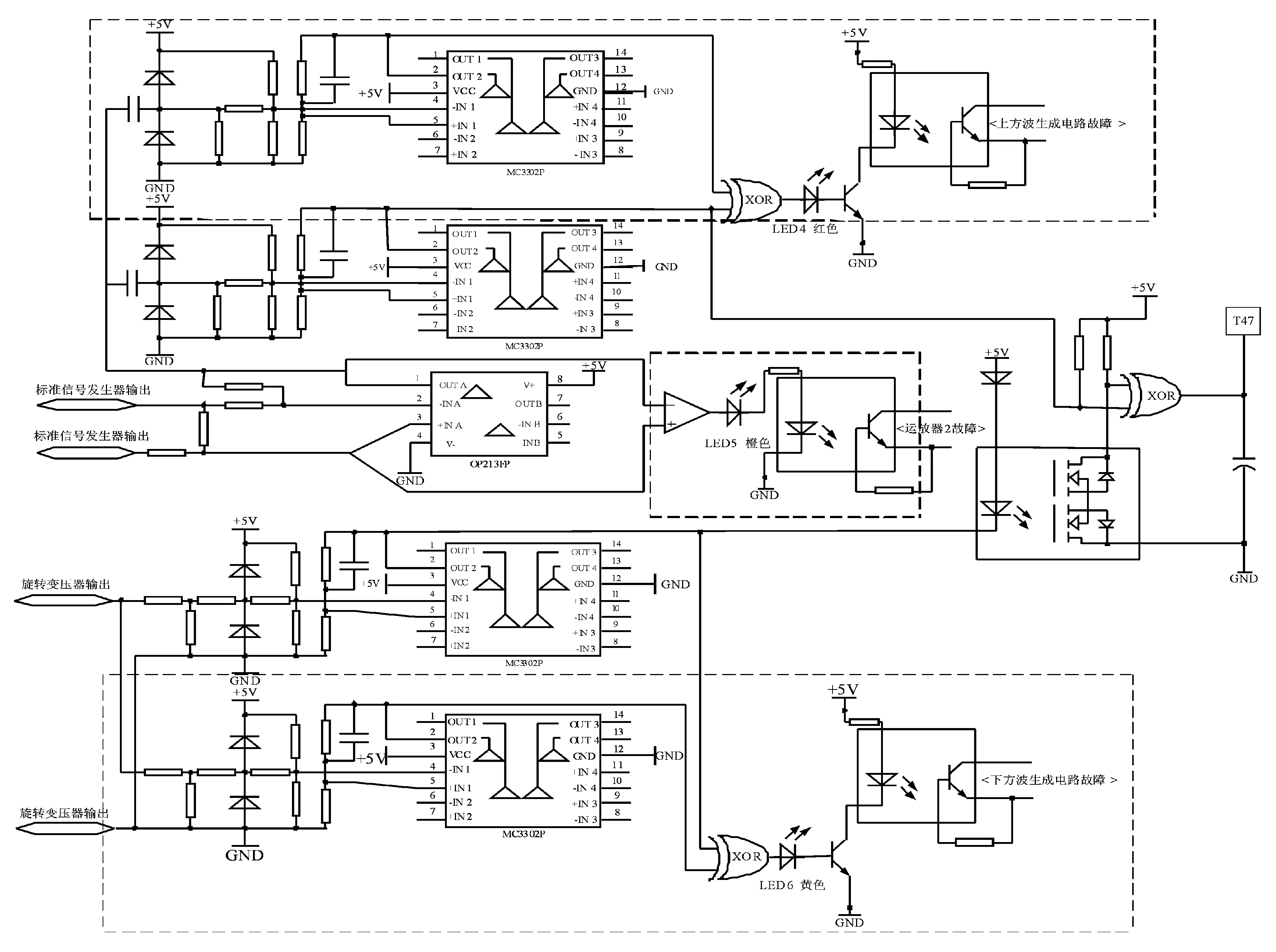

3.2.3相限提取電路內建自測試電路

運放器2對來自標準信號發生器的電信號進行放大,通過在運放器2輸入、輸出端口引出電信號至電壓比較電路,放大功能失效時,比較器輸出高電平,LED5亮,同時發出報警信號。對于上下方波生成電路,由于相限提取中對方波質量要求較高,且直接測試難度大,分別對其設置冗余BIT電路,冗余單元和被測單元接收相同的信號,同時工作,互不影響,輸出信號通過異或門進行比較,實現對被測單元功能的檢測。具體電路設計如圖8所示。

圖8 運放器2及相限提取電路自測試電路圖

4 結論

針對目前縱橫傾信號處理電路測試性差、故障診斷難度大的問題,基于TEAMS構建電路的多信號模型,根據靜態分析結果,通過在模型中添加測試點與測試,使對本次研究中定義的常見故障的隔離率從88.89%提升至100%,證明該方法能有效提升縱橫傾信號處理電路測試性能力與水平。

為實現多信號模型中部分關鍵的測試,結合不同電路的工作特點,選擇了合適類型的BIT設計方法;采用集中-分布式結構,在有效降低BIT主控裝置電路配置的同時,設計的分布式BIT電路能夠實現對故障的精確定位。有效提升該信號處理電路的測試性能力,對于指導裝備后期設計改進等具有重要意義。