襯底浮空的新型絕緣體上硅基橫向功率器件分析*

唐春萍 段寶興? 宋坤 王彥東 楊銀堂

1) (西安電子科技大學微電子學院, 寬禁帶半導體材料與器件教育部重點實驗室, 西安 710071)

2) (西安微電子技術研究所, 西安 710071)

針對有機半導體領域的發展要求, 報道了一種能夠應用于有機半導體領域襯底浮空的新型SOI LDMOS(silicon on insulator lateral double-diffused metal oxide semiconductor)功率器件, 不同于傳統無機半導體中SOI LDMOS功率器件, 該新型器件可以與絕緣的柔性襯底結合應用于有機半導體領域, 這給有機半導體領域的研究方向提供了新的可能. 本文通過仿真和流片實驗共同驗證了當常規SOI LDMOS缺失襯底電極后,比導通電阻和閾值電壓均無明顯變化, 但擊穿電壓會因為缺失襯底電極和縱向電場而下降15%左右. 針對該現象提出了一個具有表面襯底電極和漂移區氧化槽的新型SOI LDMOS功率器件, 該新型器件能夠重新給襯底提供電極、優化橫縱向電場、不明顯改變比導通電阻與閾值電壓, 同時將常規SOI LDMOS的擊穿電壓提高57.54%, 緩解了應用于有機半導體領域帶來的不良影響. 為傳統功率半導體應用于有機半導體領域的研究提供了可能, 對于有機半導體研究領域的拓展具有創新意義.

1 引 言

傳統無機半導體中功率器件能夠實現電能的變換與控制, 目前已經廣泛地應用于國民經濟的各個領域. 其中LDMOS(lateral double-diffused MOSFET, LDMOS)因能夠作為功率放大器、開關電源等設備應用于家電、汽車電子、計算機和通訊等領域而在科學研究和工業領域都發展迅猛. 20世紀60年代SOI(silicon on insulator)技術被發現并應用于LDMOS領域. SOI LDMOS因具有低功耗、低漏電流、低寄生電容和高可靠性等獨特優點而被廣泛應用于功率集成電路和高壓集成電路. 目前國內外關于能夠提高LDMOS和SOI LDMOS性能的手段有很多, 其中包括降低表面電場(reduced surface field, RESURF)技術[1-3]、場板技術[4-7]、橫向變摻雜[8-10]和橫向變厚度[11]等表面終端技術, 也包括降低體內電場(reduced bulk field,REBULF)技術[12-14]、多浮空埋層技術[15]和圖形化埋氧層技術[16,17]等體內終端技術, 還包括橫向和縱向超結技術[18-21]等.

目前LDMOS的研究大多在無機半導體領域,但隨著半導體行業的發展, 有機半導體的導電性能逐步被人們認識, 同時發現有機半導體有許多性能優于無機半導體, 因此有機半導體領域在半導體行業掀起了一個新的研究熱潮[22-24]. 有機材料及其器件可以實現硅等無機半導體的信息顯示、傳感、存儲、光電轉換等功能. 并且就目前工業發展來看,有機電子材料及其器件的主要發展方向是在簡單電路中取代無機晶體管, 從而在有機半導體領域中實現潛在的應用價值. 雖然有機半導體領域發展很快, 但目前仍然存在有機材料電學性能有限、有機集成電路發展緩慢等局限性問題. 無機材料能夠彌補有機半導體材料電子性能較差的缺陷, 因此可將無機材料與有機材料結合. 同時, 由于目前有機半導體領域關于功率器件、集成電路等領域的研究還處于空白, 因此開始考慮能否將LDMOS作為開關電源、功率放大器等設備應用于有機半導體領域. 有機半導體功率器件使得有機集成電路的構成更完善、未來應用前景更加廣闊, 同時還能實現傳統無機半導體功率器件與有機半導體領域新的突破與創新.

由于有機半導體領域大多具有絕緣基底, 這使得其器件均位于柔性絕緣襯底上, 意味著常規LDMOS的襯底將浮空并且缺失襯底電極, 從而缺失RESURF技術, 因此性能將會變差. 本文通過仿真發現, LDMOS和SOI LDMOS在襯底浮空后, 擊穿電壓(breakdown voltage, BV)會分別下降23.3%和17.4%. 同時考慮有機半導體領域大多需要器件具有較薄的襯底厚度, 而SOI LDMOS中的埋氧層能夠實現在較薄襯底厚度時承受較大耐壓, 因此本文重點研究了襯底浮空的SOI LDMOS的性能變化, 并針對襯底浮空的現象, 提出了如圖1(b)所示的具有P+多晶硅作表面襯底電極和漂移區氧化槽的新型SOI LDMOS結構.

圖1 兩種器件結構示意圖 (a) 常規SOI LDMOS結構;(b) 帶有表面襯底電極和漂移區氧化槽的新型SOI LDMOS結構Fig. 1. The schematic diagrams of the two devices are as follows: (a) Conventional SOI LDMOS structure; (b) a novel SOI LDMOS structure with a surface electrode and a drift oxidation groove.

2 器件結構

RESURF技術是器件發展的一個重要表面終端技術, 即將外延層厚度減薄使其完全被耗盡, 外延層能承受的反向偏壓會提升. 外延層耗盡區中的電場與襯底耗盡區中的電場相互作用, 使得外延層中電場分布不再是單峰值的三角電場, 而是具有兩個峰值的電場分布, 從而使得表面電場峰值降低.而襯底、外延層界面處的縱向PN結的電場峰值會先達到硅材料的臨界電場強度, 使得擊穿發生在體內, 從而實現表面電場的優化.

圖1(a)為常規且具有RESURF技術的SOI LDMOS結構. 因為具有襯底電極和縱向電場, 所以能在減薄外延層厚度的同時實現RESURF技術, 但是當SOI LDMOS應用于有機半導體領域后襯底會浮空, 繼而缺失襯底電極和縱向電場, 因此SOI LDMOS將無法實現RESURF技術, 其埋氧層也不再有優化電場的優勢. 針對上述問題, 本文提出了如圖1(b)所示的具有P+多晶硅作表面襯底電極和漂移區氧化槽的新型SOI LDMOS結構. 其中增加表面襯底電極會因為重新給襯底提供電極而改善襯底浮空的現象, 而在漂移區增加一個氧化槽, 使得實際漂移區長度增加, 能夠在比導通電阻變化不大的情況下提升SOI LDMOS的擊穿電壓[25,26].

3 襯底浮空的SOI LDMOS仿真與實驗結果

設計SOI LDMOS的性能指標為: 器件耐壓60 V, 工作漏電流50 mA, 器件仿真結構參數如表1所列. SOI LDMOS用途主要是驅動10個LED燈, 設計的漂移區長度為4 μm, 柵寬為400 μm.主要工藝流程如下: 選取晶向為 〈 100〉 的P型SOI基襯底; 由于深N阱防止漏電, 從而進行深N阱注入, 并通過退火使得雜質擴散完成推阱; 因為高壓P阱具有防止器件閂鎖的作用, 所以通過注入獲得高壓P型輔助層和N型漂移區; 通過氧化刻蝕獲得有源區和柵氧化層; 通過注入退火生成低壓P阱和N阱, 其中低壓P阱即為器件基區, 低壓N阱作為緩沖區域, 緩解漏電極高峰電場來提高器件穩定性; 通過淀積獲得多晶硅并進行多晶硅重摻雜形成柵電極; 通過N+和P+注入獲得源極、漏極和基區接觸; 通過光刻淀積獲得器件的接觸孔和金屬布線; 通過金屬淀積獲得頂層技術; 最后進行金屬電極表面鈍化. 圖2所示為實驗后的8 in晶圓圖片和其在電子顯微鏡下的截面圖與俯視圖.

表1 常規SOI LDMOS與襯底浮空SOI LDMOS器件仿真最優參數Table 1. Simulation optimal parameters of conventional SOI LDMOS/ substrate floating SOI LDMOS devices.

圖2 實驗結果 (a) 8 in晶片; 電子掃描顯微鏡下的SOI LDMOS結構截面圖(b)和俯視圖(c)Fig. 2. Experimental results: (a) 8-inch wafer; (b) sectional view and (c) vertical view of SOI LDMOS under an electron scanning microscope.

借助中國航空工業集團公司的下屬公司江蘇七維測試技術有限公司的測試平臺完成了8 in晶圓測試. 測試設備為測試儀T862和探針臺JC8001;測試溫度為20—24 ℃; 測試濕度為(45% +/—10%)RH; 測試間潔凈度為10000級. 下面通過仿真和流片實驗及其測試來對比分析具有RESURF技術常規SOI LDMOS在襯底浮空前后的性能變化.

圖3所示為常規且帶有RESURF技術的SOI LDMOS在結構參數和摻雜濃度相同時, 襯底浮空前后的表面電場和縱向電場仿真結果對比圖. 如圖3(a)所示, 在襯底浮空前, 器件耐壓主要取決于柵邊緣的P阱和漂移區構成的PN結與漏端N+N結, 在表面電場圖中表現為表面有兩個峰值, 一個位于柵電極附近, 另一個位于漏極附近. 在襯底浮空后, 由于襯底對表面電場的調制作用變差, 表面耐壓主要取決于P阱和漂移區構成的PN結, 因此表面電場分布逐漸不均勻, 趨于三角電場, 此時器件更容易擊穿. 如圖3(b)所示, 襯底浮空前SOI LDMOS因為埋氧層的調制, 能夠在較薄襯底時實現較好耐壓. 在襯底浮空后, 器件的縱向電場分布明顯變差, 埋氧層的調制作用變差, 電場峰值會下降25%左右.

圖3 襯底厚度Tsub = 15 μm, 漂移區長度LD = 4 μm的SOI LDMOS電場分布圖 (a) 表面電場分布圖; (b) 縱向電場分布圖Fig. 3. Electric field distribution graph for SOI LDMOS with substrate thickness of 15 μm (Tsub = 15 μm) and drift zone length of 4 μm (LD = 4 μm): (a) Surface electric field distribution graph; (b) longitudinal electric field distribution graph.

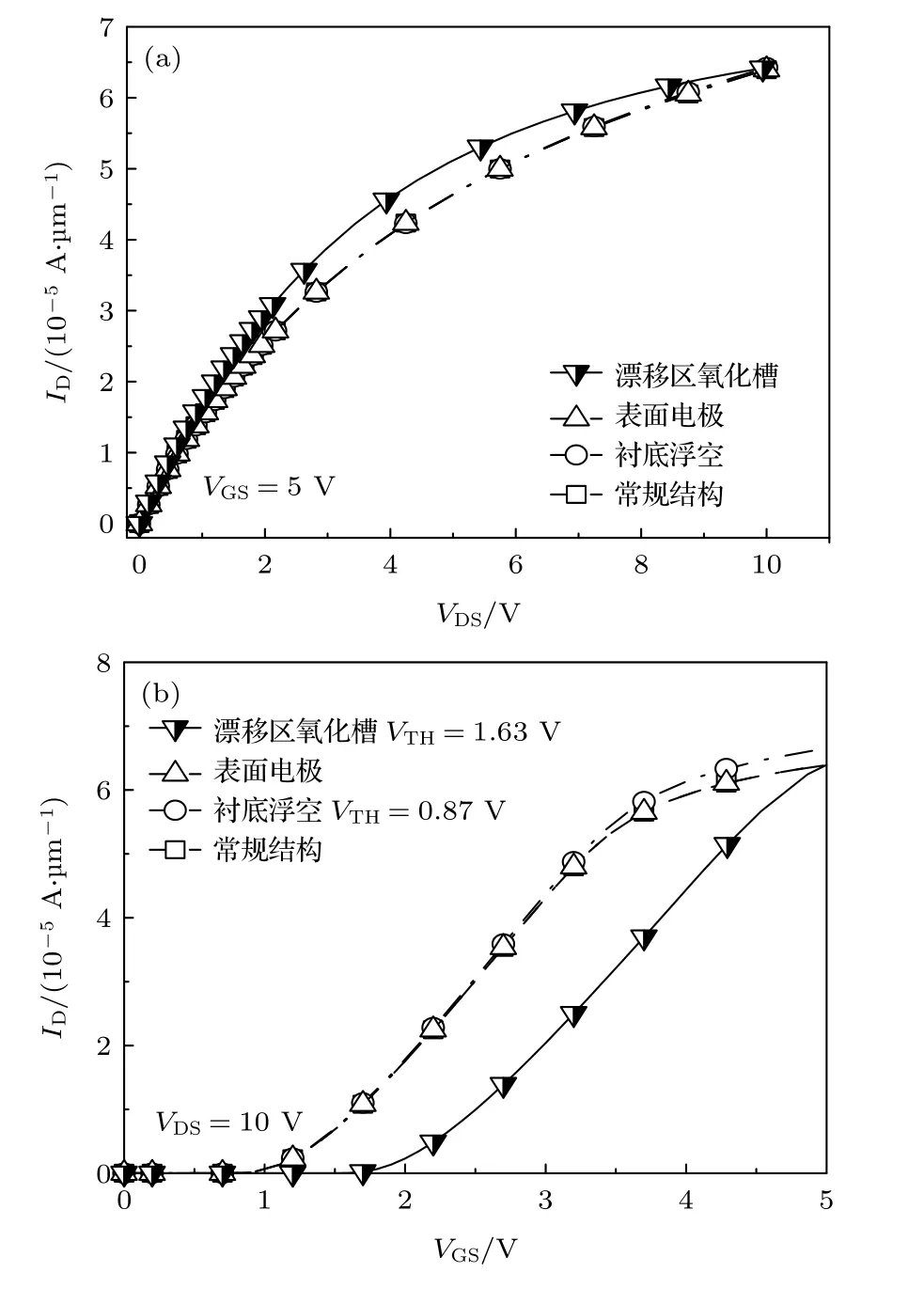

圖4 所示為常規且帶有RESURF技術的SOI LDMOS在襯底浮空前后的輸出和轉移特性仿真與實驗結果對比圖. 仿真和實驗均基于襯底厚度為15 μm和漂移區長度為4 μm的SOI LDMOS.由于使用ISE-TCAD進行器件仿真時, 雖然考慮了諸如載流子運輸模型、載流子產生-復合模型、遷移率模型等影響因素, 還考慮了載流子散射、能帶變窄等非理想因素, 但相較于實驗所得器件而言,還是處于較理想狀態. 工藝過程中, 由于儀器的精密程度、外延層生長環境和退火條件等因素的影響, 使得實驗所得器件性能略差于仿真所得器件,因此實驗所得器件的電流會低于仿真所得結果. 從圖4還可以看出, 不論是仿真結果還是實驗結果,襯底浮空對SOI LDMOS轉移和輸出特性的仿真與實驗結果均無明顯影響. 其中如圖4(b)所示, 因為在襯底浮空后, 襯底對漂移區電場調制效果減弱, 表面電場變弱, 漂移區中載流子速度變慢, 器件準飽和漏電流變小. 因為器件柵極結構和基區摻雜沒有變化, 所以在仿真和實驗結果中器件的閾值電壓均不變.

圖4 襯底厚度Tsub = 15 μm, 漂移區長度LD = 4 μm的SOI LDMOS仿真和實驗結果對比 (a) VGS = 5 V時的輸出特性曲線; (b) VDS = 10 V時的轉移特性曲線Fig. 4. Comparison of simulation and experimental results for SOI LDMOS with substrate thickness of 15 μm (Tsub =15 μm) and drift zone length of 4 μm (LD = 4 μm): (a) Output characteristic curve when VGS = 5 V; (b) transfer characteristic curve when VDS = 10 V.

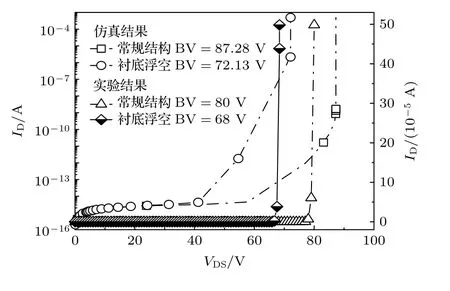

圖5 所示為常規且帶有RESURF技術的SOI LDMOS在襯底浮空前后的擊穿特性仿真與實驗結果對比圖. 從圖5中的仿真結果可以看出, 在相同結構參數和摻雜濃度時, 襯底浮空后, 擊穿電壓從87.28 V降低到72.13 V, 下降了17.4%. 導致常規SOI LDMOS襯底浮空后擊穿電壓降低的主要原因如圖6所示, 圖6為上述兩種結構在摻雜濃度相同時仿真擊穿電壓與漂移區摻雜濃度的關系曲線. 由于襯底浮空后, 缺失襯底電極使得原器件失去RESURF技術, 電場分布也會變化, 從而使得器件最優擊穿電壓對應的漂移區濃度發生變化, 因此常規SOI LDMOS在襯底浮空后擊穿電壓會降低. 兩種結構的比導通電阻(specific on-resistance,RON,sp)均為2.21 mΩ·cm2, 沒有明顯變化. 并且由于埋氧層的優勢, 零柵壓下器件的漏電流均為5 ×10—14A/μm左右. 從圖5中實驗結果可以看到, 在襯底浮空后, 器件的擊穿電壓從80 V下降到60 V.雖然性能有所下降, 但是仍然可以驅動10個LED燈.

圖5 SOI LDMOS擊穿特性的仿真和實驗結果對比圖Fig. 5. SOI LDMOS comparison of simulation and experimental results of breakdown characteristics.

圖6 漂移區摻雜濃度對SOI LDMOS兩種結構對應的擊穿電壓的影響Fig. 6. Effect of doping concentration in drift region on breakdown voltage of two SOI LDMOS structures.

4 新型SOI LDMOS的仿真與優化

常規且帶有RESURF技術的SOI LDMOS在應用于有機半導體領域時會使其襯底浮空, 進而缺失襯底電極和RESURF技術, 性能就會有所降低. 因此提出具有P+多晶硅作表面襯底電極和漂移區氧化槽的新型SOI LDMOS結構. 該新型結構的工藝相較于第3節不同的部分如下: 1)在N阱和P阱工藝完成后, 在器件左端刻蝕一個窗口, 淀積多晶硅并進行P型重摻雜, 從而獲得表面襯底電極; 2)器件表面生長鈍化層, 在N阱表面刻蝕出一個窗口, 通過干氧工藝生長氧化槽. 該新型結構可以通過轉印工藝與柔性襯底結合, 作為開關電源、功率放大器等設備應用于有機集成電路,從而實現其在研究領域、應用前景等方面的拓展.下面將針對常規SOI LDMOS、襯底浮空的SOI LDMOS、增加表面襯底電極和襯底浮空的SOI LDMOS以及同時具有P+多晶硅作表面襯底電極和漂移區氧化槽的SOI LDMOS這幾種器件的性能進行分析比較.

圖7所示為四種器件的表面電場和縱向電場的對比圖. 如圖7(a)所示, 在襯底浮空后, 漂移區不能完全耗盡, 表面電場分布趨于三角電場. 加上表面襯底電極后, 曲線和有襯底浮空前重合, 器件性能得到優化. 再在漂移區加上氧化槽以后, 漂移區有效長度增加, 器件的表面拓展到槽表面, 能夠達到對表面電場的優化效果. 器件的表面電場增加一個新的電場峰, 達到優化表面電場的目的. 如圖7(b)所示, 常規SOI LDMOS因為埋氧層的調制, 能夠在較薄襯底時實現較好耐壓. 當襯底浮空后, 器件的縱向電場分布明顯變差, 經過表面襯底電極和漂移區氧化槽的橫縱向電場的同時優化, 器件的縱向電場耐壓提升.

圖7 幾種SOI LDMOS的電場分布圖 (a) 表面電場分布圖; (b) 縱向電場分布圖Fig. 7. Electric field distribution of several SOI LDMOS:(a) Surface electric field distribution; (b) longitudinal electric field distribution diagram.

圖8和圖9所示為幾種器件的擊穿、轉移、輸出特性曲線. 由圖8可知, 在襯底浮空后, SOI LDMOS的擊穿電壓從87.28 V降低到72.13 V, 下降了17.4%, 加上表面襯底電極后, 擊穿電壓恢復到常規SOI LDMOS的擊穿電壓. 比導通電阻都為2.21 mΩ·cm2, 沒有明顯變化. 在漂移區加上氧化槽以后, 橫縱向電場得到同時優化, 擊穿電壓提高到137.5 V, 相比于常規SOI LDMOS增加了57.54%. 由圖9可知, 增加漂移區氧化槽之前的幾種器件閾值電壓為0.87 V, 襯底浮空對閾值電壓沒有明顯影響. 在加了漂移區氧化槽后, 閾值電壓(threshold voltage,VTH)增加到1.63 V. 與此同時, 襯底浮空對器件的電流、比導通電阻均沒有明顯影響. 通過上述分析可知, 該新型SOI LDMOS能夠較好地緩解襯底浮空后的不良影響, 并且還能在比導通電阻變化不大的情況下提高其擊穿電壓.

圖8 幾種SOI LDMOS的擊穿特性圖Fig. 8. Breakdown characteristics of several SOI LDMOS.

圖9 幾種SOI LDMOS的仿真結果 (a) 輸出特性曲線;(b) 轉移特性曲線Fig. 9. Simulation results of several SOI LDMOS: (a) Output characteristic curve; (b) transfer characteristic curve.

圖10 所示為該新型SOI LDMOS結構中漂移區濃度ND、氧化槽寬度DOX和厚度TOX等參數對擊穿電壓BV和比導通電阻RON,sp的影響曲線.如圖10(a)所示, BV隨ND的增加呈現出先上升后下降的變化趨勢, 而RON,sp則呈現出下降的趨勢, 因此綜合考慮漂移區濃度最終選取5 × 1016—6 × 1016cm—3. 如圖10(b)所示, BV隨DOX的增加先迅速上升后變化不大, 而RON,sp變化趨勢則與BV相反, 因此選取DOX為3—4 μm. 如圖10(c)所示, BV隨TOX的增加先上升后下降, 而RON,sp則隨之增加呈現持續上升的趨勢, 因此最終選取TOX為0.5—0.6 μm, 表2所列為該新型器件優化后對應的結構參數. 最終該新型SOI LDMOS的擊穿電壓為137.5 V, 比導通電阻為1.96 mΩ·cm2,能夠實現在RON,sp基本不變的情況下將常規SOI LDMOS的BV增加57.54%, 從而實現常規SOI LDMOS在應用于有機半導體領域后襯底浮空時的性能優化, 也實現了將功率開關器件與有機半導體領域的新的突破與創新.

圖10 新型SOI LDMOS的幾種參數對BV和RON, sp的影響 (a) ND的影響曲線; (b) DOX的影響曲線; (c) TOX的影響曲線Fig. 10. Influence of several parameters of new SOI LDMOS on BV, RON,sp: (a) Influence curve of ND; (b) influence curve of DOX; (c) influence curve of TOX.

表2 新型SOI LDMOS器件仿真最優參數Table 2. Simulation optimal parameters for novel SOI LDMOS devices.

5 結 論

本文通過仿真和流片實驗兩種方式共同驗證當常規且帶有RESURF技術的SOI LDMOS在應用于有機半導體領域后, 襯底會浮空使得常規SOI LDMOS缺失襯底電極和RESURF技術, 同時使得SOI LDMOS中埋氧層優化電場的作用也消失, 進而使得常規SOI LDMOS的擊穿電壓從87.28 V下降到72.13 V. 針對該現象, 提出的具有P+多晶硅作表面襯底電極和漂移區氧化槽的新型SOI LDMOS結構能在比導通電阻沒有明顯變化的情況下, 將襯底浮空的SOI LDMOS擊穿電壓從72.13 V上升137.5 V, 相比常規SOI LDMOS增加了57.54%. 在實現SOI LDMOS與柔性襯底結合且不降低器件原本性能的同時, 實現了傳統無機半導體功率器件與有機半導體領域新的突破與創新. 不僅能彌補有機半導體材料電子性能較差的缺陷, 同時還能拓展有機半導體的研究領域. 未來可以通過工藝的創新和改進, 給有機半導體領域功率半導體方向提供更多的創新和可能性.