采用FPGA減小控制延時的逆變器直流側電容均壓策略

王位, 汪光森, 周斌, 張振宇

(海軍工程大學 軍用電氣科學與技術研究所,武漢 430033)

0 引 言

電磁發射技術是一種將電磁能轉化為負載動能,使負載達到發射目標速度的新型發射技術,該技術在不同的發射領域均具備較大的技術優勢和廣泛的應用前景[1]。電磁發射技術的本質是能量的變換[2]。因此,是具有高性能指標、強可靠性和廣泛適用性的能量變換裝置,是電磁發射系統的關鍵環節,而能量變換裝置的核心設備就是逆變器[3-4]。

隨著二極管中點箝位式(NPC)拓撲結構的廣泛應用,多電平逆變器得到了長足的發展[5]。其中,NPC/H橋五電平逆變電路因為具備拓撲結構簡單、開關器件電壓應力低、直流電源數量少等優點,被各領域大功率逆變器廣泛采用[6-7]。但是該型拓撲結構固有的直流側電容電壓波動等問題,制約了其在電能變換質量有較高要求的應用領域的發展[8-9]。

針對該型拓撲結構直流側電容電壓不均的問題,國內外學者進行了廣泛研究,主要提出了以下幾種方法:零序電壓注入法、冗余矢量法、虛擬矢量法和目標函數法[10-15]等。文獻[10]對傳統調制方法進行了對比,提出了一種適用于三電平的零序電壓注入調制策略,優化了中點電壓平衡控制的動態響應速度。文獻[11]提出了一種在選擇冗余矢量時增加過渡開關狀態的新型空間矢量脈寬調制技術(SVPWM)。文獻[12]和文獻[13]通過重新計算虛擬矢量,在滿足調制需求的同時進一步優化了均壓控制效果。文獻[14]和文獻[15]提出構建計算直流側電容電壓函數的主動控制方法。此外,文獻[16]提出一種應用于多電平高壓直流轉換器的基于FPGA的電容均壓控制策略,其目的是為了減小轉換過程中開關器件的開關次數,加快均壓排序算法計算速度。

在逆變器應用中,均壓控制大多數是基于調制過程實現的。均壓控制的關鍵在于模擬量采樣的時效性。上述研究策略能夠在一定程度上實現對均壓控制的目的,但是也都不可避免的面對采樣與控制之間存在幾倍于開關周期的延時問題。目前關于均壓策略的研究多集中于針對調制算法或均壓算法的設計,而對均壓算法執行過程中由硬件架構等因素引入的延時或其他形式誤差對均壓執行效果的影響的研究相對較少。另外,目前國內外對于五電平NPC/H橋逆變器直流側電容均壓策略的研究對象負載電路連接方式多為星形連接,各相并不獨立[17-19]。

本文以某型電磁發射系統的獨立雙三相共母線五電平NPC/H橋逆變器為研究對象,針對其直流側電容電壓不均衡問題,提出一種均壓優化控制策略,實現在控制器內部FPGA芯片輸出脈沖矢量前進行直流側電容電壓大小關系判斷的設計。目的是為了減小控制延時以避免均壓調節反向的發生,優化直流側電容均壓效果、抑制電容電壓的波動,并通過半實物實時仿真平臺對提出的采用FPGA的均壓優化控制策略的可行性和有效性進行驗證。

1 逆變器拓撲結構與均壓控制原理

本文的研究對象為應用于某型電磁發射系統的獨立雙三相共母線五電平NPC/H橋逆變器。其直流側采用雙三相共直流母線的連接方式,2個逆變單元并聯于直流電源正負極兩端。直流側電路主要由一個直流電源和兩組直流支撐電容構成。每組支撐電容分為上支撐電容Cup和下支撐電容Cdn,如圖1所示。

圖1 獨立雙三相共母線五電平NPC/H橋逆變器拓撲圖Fig.1 Topology of independent double three-phase common bus five-level NPC/H bridge inverter

1.1 功率單元拓撲結構

逆變器交流側由兩條能量鏈組成,每條能量鏈為一個逆變單元,每個逆變單元包含三組五電平NPC/H橋功率單元。功率單元電路為五電平NPC/H橋拓撲結構,如圖2所示。

圖2 五電平NPC/H橋逆變電路拓撲結構圖Fig.2 Block diagram of five-level NPC/H inverter circuit

逆變器的負載端為獨立六相發射電機,每個逆變單元分別為發射電機一套三相繞組負載供電,兩套三相繞組之間相位差為30°。每套三相繞組之間相互獨立,各相間供電電壓和電流、相位差120°。一組功率單元對應為電機的一相獨立繞組供電。開關器件絕緣柵雙極型晶體管(IGBT)XP/XN和箝位器件功率二極管XPD/XND采用雙管并聯的模式。在逆變過程中,并聯IGBT采用同一驅動信號進行驅動,發揮相同的開關通斷功能。因此,可將并聯器件等效為一個器件模塊。簡化的五電平NPC/H橋功率單元拓撲結構,如圖3所示。

圖3 五電平NPC/H橋功率單元拓撲結構圖Fig.3 Block diagram of NPC/H five-level power unit

圖中:T為IGBT模塊;D為二極管模塊;Cup為上支撐電容;Cdn為下支撐電容。P為功率單元正極,N為功率單元負極,O為中點。H橋逆變電路由左、右2個NPC三電平橋臂組成。每個三電平橋臂由4個開關管和2個箝位二極管組成,開關管T1、T2、T3、T4和二極管D1、D2組成左橋臂,橋臂中點為OL;開關管T5、T6、T7、T8和二極管D3、D4組成右橋臂,橋臂中點為OR。橋臂中點OL與OR之間串接負載單相繞組,流過繞組的電流為Ix,x代表雙三相逆變器任意一相。設繞組電流由OL流向OR為電流正方向。直流母線電壓為UDC,在充電初始狀態兩個支撐電容電壓分別為UDC/2。設功率單元輸出的單位電平為E,滿足關系:E=UDC/2。

1.2 功率單元均壓控制原理

五電平NPC/H橋功率單元可輸出五種電平:-2E、-E、0、+E、+2E。其中,“-2E”、“0”和“+2E”這3種電平分別只有唯一輸出通路,而“-E”電平和“+E”電平的輸出通路分別有兩種。如圖4、圖5和圖6所示。

圖4 五電平NPC/H橋功率單元單輸出通路:“-2E”、“0”和“+2E”電平Fig.4 NPC/H bridge five-level power unit output single channel of “-2E” level,“0” level and “+2E” level

圖5 五電平NPC/H橋功率單元雙輸出通路:“+E”電平Fig.5 NPC/H bridge five-level power unit output double channels of “+E” level

圖6中加粗線路為功率單元在不同電平條件下的輸出通路,箭頭方向表示電流流通方向,虛線IGBT表示其開關狀態為“開通”。結合圖5和圖6可知,當輸出“±E”電平時,存在冗余輸出通路。冗余輸出通路的輸出作用相同,但對直流側電容充放電作用不同。因此,可根據所需輸出電平值,結合直流側電容電壓大小關系和繞組電流方向,選擇合適的輸出通路,令電壓值偏大的電容放電或令電壓值偏小的電容充電的過程。

設上支撐電容Cup電壓值為UCup,下支撐電容Cdn電壓值為UCdn。在滿足UCup>UCdn條件下,輸出“+E”電平時:若Ix>0,則選擇輸出通路“圖5(a)”,對Cup放電;反之,若Ix<0,則選擇輸出通路“圖5(b)”,對Cdn充電。同理,輸出“-E”電平時:若Ix>0,則選擇輸出通路“圖6(a)”,對Cdn充電;若Ix<0,選擇輸出通路“圖6(b)”,對Cup放電。可將“+E”和“-E”電平對應的2種開關矢量稱為冗余矢量。

圖6 五電平NPC/H橋功率單元雙輸出通路:“-E”電平Fig.6 NPC/H bridge five-level power unit output double channels of “-E” level

2 均壓控制延時的影響與優化策略

上述基于冗余輸出通路的均壓調節策略是通過逆變器中控制器的調制算法和冗余矢量選擇算法實現的。計算和選擇冗余矢量的依據是每個開關周期起始采樣得到的模擬量數值。本文研究對象控制器的調制與控制時序如圖7所示。

控制器采用DSP+FPGA的雙芯片組合架構,電壓脈沖調制策略采用空間矢量調制算法。控制器的控制周期即為逆變器的開關周期。每個控制周期被均分為奇周期和偶周期。如圖7所示,從在DSP中進行模擬量采樣、均壓矢量選擇和傳輸矢量,到FPGA實際執行矢量的過程中平均存在1.5個開關周期的控制延時。

圖7 控制器調制時序與控制延時Fig.7 Controller modulation timing and control delay

控制延時在均壓調節過程中將導致均壓欠調和均壓調節反向兩種現象的發生。下面分別闡述上述兩種現象對直流側電容均壓的影響。

2.1 均壓欠調

本系統采用的開關頻率為1.25 kHz,電壓測試的穩態峰值頻率40 Hz。每個開關周期采樣一次,一個周期的輸出電流平均經歷31次采樣。均壓欠調發生的原因是電流采樣時刻與均壓矢量輸出之間存在延時。本裝置某次電壓測試實驗波形如圖8所示。

每個縱向虛線間隔代表一個開關周期。以在一個開關周期內電流過零的某相為例,如圖8(c)所示,在T1周期,采集得到I>0,并依據這一采樣結果進行了相應均壓矢量的選擇。但是由于控制延時的存在,當輸出矢量實際發揮作用時,其執行周期是在T2周期。而此時,電流已經反向變為I<0,從而導致該相輸出通路的均壓調節起到了與預期相反的作用。

某一相電流過零,另外兩相電流必然不過零。由均壓控制延時引起的三相中的過零一相均壓調節反向,導致三相均壓調節能力被減弱的現象可稱為均壓欠調。該現象的發生與逆變器開關頻率和電流頻率的關系有關。由于在一般情況下開關頻率遠大于電流頻率,所以在現有的均壓控制策略執行過程中均壓欠調是不可避免的。

不過,若某相功率單元的電流在2個開關周期間過零,該相電流相比于另外兩相必然是絕對值最小。在圖8中T2周期進行均壓調節時,2個電流不過零相才是均壓調節的主力。過零相的電流最小,對電容的充放電能力最弱。因此,由均壓控制延時引起的均壓欠調是導致直流側電容電壓波動的次要原因,并非主要原因。

圖8 電壓測試實驗波形Fig.8 Experimental waveform of voltage test

2.2 均壓調節反向

均壓控制延時除了會導致均壓欠調外,相似的問題在電容電壓大小關系的判斷上也同樣存在。而且,此時的判斷誤差導致的負效果更加明顯。本裝置某次電壓測試實驗波形如圖9所示。

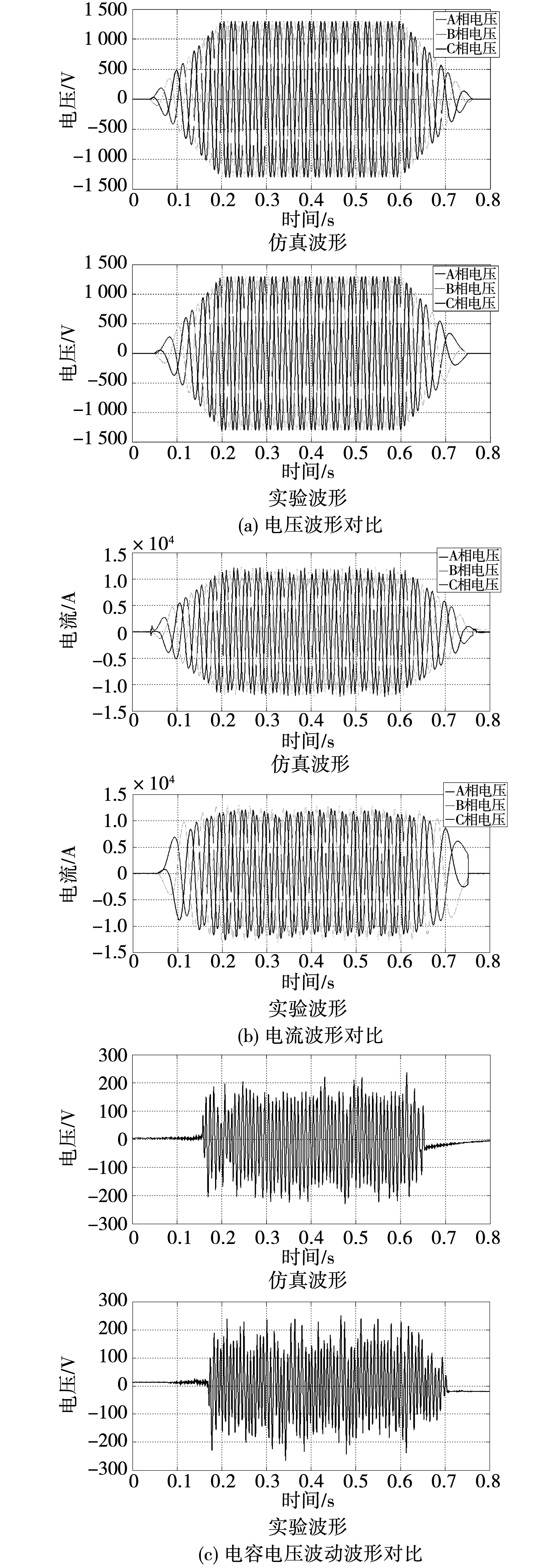

在T4周期采樣的得到電容電壓關系:UCup>UCdn,并依據這一采樣結果進行了相應均壓矢量的選擇。但是在T5周期實際執行矢量時,電容電壓大小關系已經反向,變為:UCup 綜上,由均壓控制延時引起的均壓調節反向是導致電容電壓差值波動加劇、電容電壓不均衡度增加的主要原因。因此,基于現有的控制器架構和、冗余輸出通路的均壓調節策略,對其進行優化設計,避免均壓控制延時引發的均壓調節反向的發生,從而優化電容均壓效果具有一定實際意義。 在本控制系統中,每個控制器對應控制逆變器的一套三相逆變單元。在優化前的控制結構中,控制器的模擬量采樣、PWM脈沖計算和均壓調節控制等功能由DSP芯片完成。FPGA僅作為DSP的擴展串口執行開關矢量輸出功能。在實現減小均壓控制延時的優化目標時,并不需要獲取直流側電容的實際電壓數值,僅需實時準確的獲得上、下電容電壓大小關系,從而正確判斷均壓調節方向。因此,在設計基于FPGA的均壓優化控制策略時,首先需要在模擬量采樣板卡上設計一個直流側電容電壓比較電路,實時采集電容電壓大小關系。比較電路的輸出信號通過底板與主控制板上FPGA的I/O接口連接,均壓比較電路原理圖如圖10所示。 圖10 均壓比較電路原理圖Fig.10 Schematic diagram of voltage balance comparing circuit 其次,將PWM脈沖計算功能的實現方法進行調整。開關矢量占空比的計算和輸出電平的計算兩部分功能保留在DSP中實現,將開關矢量選擇的功能轉移到FPGA中實現。然后,通過DSP將三相電流的方向和PWM輸出脈沖的電平值傳輸給FPGA用于均壓矢量選擇。最后,結合均壓比較信號、電流方向和輸出電平值,在FPGA中進行開關矢量選擇并輸出。優化后的均壓控制時序如圖11所示。 圖11 優化后的均壓控制時序圖Fig.11 Controller modulation timing and control delay 圖11中,在奇、偶周期的起始時刻,FPGA會裝載本半周期的開關矢量,根據占空比在相應的時刻輸出。為了防止開關矢量切換過程中出現橋臂直通的現象發生,在每半個開關周期的起始位置和終止位置都會布置死區。在本系統中,開關周期為800 μs,死區設置為7 μs。那么,優化后的均壓策略選擇在半周期開始前的死區進行電壓關系判斷與均壓矢量的選擇。均壓控制延時被從約1 200 μs減小至7 μs,可以忽略不計,消除均壓控制延時導致對電容電壓關系判斷的錯誤,從而優化直流側電容電壓的均衡效果。上述內容構成了采用FPGA減小控制延時的均壓優化控制策略。 為了進一步驗證上文敘述的基于FPGA減小控制延時的均壓優化控制策略的可行性和有效性,搭建了基于某型電磁發射系統架構的半實物實時仿真平臺,如圖12所示。該平臺由三臺控制器(一主兩底)、實時仿真機、接口板以及上位機組成。 圖12 半實物實時仿真平臺Fig.12 Semi-physical real-time simulation platform 該平臺可對某型電磁發射系統的多種工況進行實時仿真,主要用于對控制器軟件算法功能的驗證,具備較高的準確性。下面對在同一工況下的實時仿真結果與實驗結果進行對比。在電壓測試工況下母線電壓為2 000 V,測試電壓幅值峰值為1 300 V,測試電壓頻率峰值為40 Hz,采集得到電流峰值為12 000 A左右,電容電壓波動幅值為230 V左右。實驗平臺與實時仿真平臺的電流波形與直流側電壓差值波形對比,如圖13所示。 圖13中,當逆變器負載電流大于9 000 A進入瞬時大電流工況后,直流側電容電壓波動加劇的現象。 圖13 仿真波形與實驗波形對比Fig.13 Comparison between simulation waveform and experimental waveform 應用上述半實物實時仿真平臺對上文提出的基于FPGA減小均壓控制延時的均壓優化控制策略進行了驗證。實時仿真工況保持與上文實驗工況相同的電壓測試:峰值電壓1 300 V,峰值頻率40 Hz。采用均壓優化控制策略前后,直流側電容電壓波形對比如圖14所示。 圖14 電容電壓波動波形對比Fig.14 Capacitance voltage oscillation waveform comparison 圖14中,在采用優化的均壓策略后,直流側電容電壓波動的幅值明顯降低,由230 V左右降低至100 V左右,降低了56.5%。 直流側電容電壓的差值引起的中點電流Io會產生中點能量損耗Ws,滿足關系式 (1) 其中Zo為中點電路等效阻抗。設中電電路等效阻抗為單位阻抗,其對應的中點能量損耗為單位中點能量損耗。那么,從單位能量損耗角度對比分析均壓優化效果,如圖15所示。 圖15 單位中點能量損耗波形對比Fig.15 Unit midpoint energy loss waveform comparison 圖15中,在上述電壓測試工況下,優化前單位中點能量損耗為6 729 J,優化后單位中點能量損耗為850 J,降低了87.4%。 本文提出的采用FPGA減小控制延時的均壓優化控制策略,消除了均壓控制延時,抑制了均壓控制延時引起的均壓調節反向的發生。在典型瞬時大電流、大功率工況下,可將電容電壓波動幅值降低了56.5%,單位中點能量損耗降低了87.4%。該優化控制策略可拓展應用于其他領域的獨立N相共母線NPC/H橋多電平逆變器的直流側電容均壓控制策略中。2.3 采用FPGA的均壓優化控制策略

3 實時仿真驗證

3.1 半實物實時仿真平臺

3.2 均壓優化控制策略驗證

4 結 論