基于FPGA的H.264碼流實時傳輸系統設計

(中北大學 電子測試技術國家重點實驗室,太原 030051)

0 引言

伴隨著移動通信技術標準從1 G~4 G,再到5 G的迭代更新,數字視頻質量也從標清,高清,全高清到超高清發生了翻天的改變[1],隨之而來的是海量的視頻數據和傳輸過程中的帶寬壓力。多媒體處理技術的發展產生諸多對龐大原始視頻數據的視頻壓縮編碼算法,應用比較廣泛的有H.264、H.265、JPEG、MJPEG等,不同的編碼算法適用于不同的場合,從軟件處理到硬件編碼,實現方式也不盡相同[2-3]。國內可查的使用嵌入式平臺進行視頻編碼的有中北大學儀器科學與動態測試教育部重點實驗室,該實驗室以TMS320C6678 DSP平臺實現的HEVC硬件H.265視頻壓縮算法,壓縮后視頻數據減少大約 39~74%[1],效果較好。不少學者利用計算機軟件進行編碼算法研究,如電子科技大學的朱艷玲提出的基于H.264宏塊編解碼算法的研究[4]。為了響應國家對集成電路行業的扶持政策,本設計選用華為海思半導體的Hi3516A平臺,此平臺支持H.264、H.265、MPEG等編碼算法,綜合考慮編碼效率、容錯能力、網絡親和性等因素,選擇H.264算法進行硬件編碼。海思平臺應用于安防監控領域的多種場景,側重IP攝像機的系統布局[5-6]。但面對攝像頭采集的視頻數據生成的編碼碼流遠距離傳輸問題,海思平臺就顯得捉襟見肘[7],因此本系統利用海思平臺網絡接口創造性地使用RAW_SOCKET協議將編碼碼流傳輸至FPGA平臺[8-9],FPGA平臺能很好地實現較于TCP(transmission control protocol)協議相對簡單的UDP(user datagram protocol)協議,可成功對接海思平臺,完成H.264碼流的接收。本文著重于介紹如何利用FPGA進行H.264碼流傳輸,最后介紹系統功能的測試。

1 方案設計

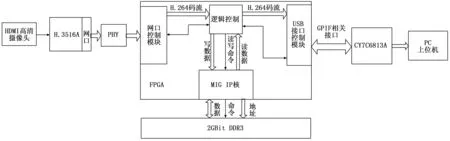

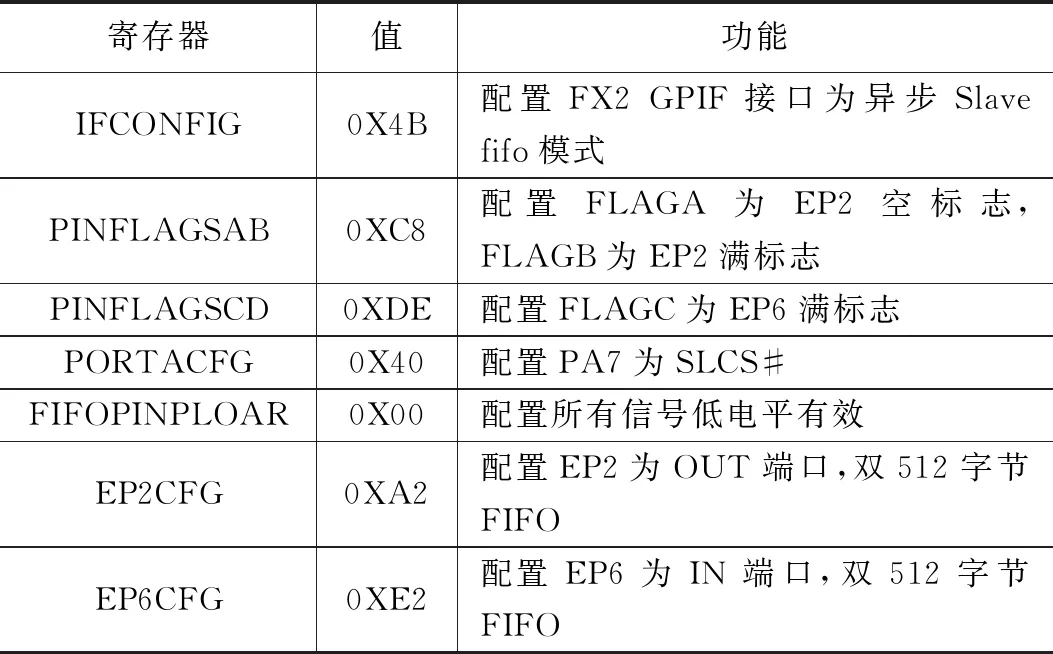

本系統主要由H.264碼流生成源Hi3516A平臺、網口模塊、DDR3模塊、USB2.0模塊和USB上位機軟件組成,系統框圖如圖1所示。

圖1 系統總體框圖

系統主控制器選擇賽靈思公司spartan6 xc6slx45,此芯片含有43 661個邏輯單元,54 576個觸發器,116個18 kB塊RAM,最大用戶IO可達358個,且集成有GTP、PCIE、MCB等高速硬件控制器,在電子工程領域應用廣泛,因此足以支持本設計的資源需求[10-11]。Hi3516A平臺負責采集HDMI攝像頭數據,采用H.264算法進行編碼壓縮,平均碼流速率控制在4 Mbps;生成的碼流由FPGA平臺網口模塊接收,該模塊實現UDP協議;系統選用1片2 Gbit DDR3芯片作為緩存介質,以解決速率匹配和數據緩存問題;系統功能的驗證由USB2.0模塊將碼流數據PC回傳,上位機軟件接收并本地保存,而后線下進行數據完整性、視頻播放流暢性等系統功能測試分析。

2 H.264碼流源生成模塊介紹

Hi3516A是華為海思半導體公司推出的一款多功能通信媒體處理芯片,旨在提供新一代HD IP攝像機SOC方案,其內部集成ARM Cortex-A7處理器內核及H.264、H.265、MJPEG、JPEG等硬件編碼器,主頻可達600 MHz;具有多路視頻實時編碼能力,支持的最大輸入分辨率可達5 M Pixel;輸入時序為8/10/12/14 bit RGB Bayer DC時序, BT.601、 BT.656、 BT.1120和MIPI、 LVDS/Sub-LVDS、HiSPi等;支持RGMII/GMII網口輸出。此芯片能滿足監控領域的各種場景需求[12-13]。Hi3516A采用ARM+H.264/AVC硬件編碼器的方案實現H.264編碼,內部各硬件模塊和控制器之間采用ARM公司先進微控制器總線結構AMBA3.0實現高速互聯,性能強大[14-15]。

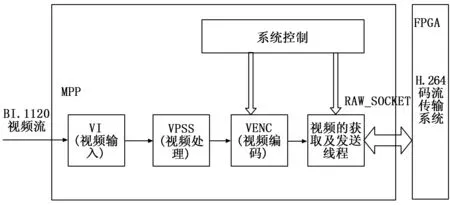

本設計選用Hi3516A作為HDMI高清攝像頭數據壓縮編碼平臺,利用網口輸出編碼碼流來為系統提供H.264碼流源。軟件工作流程如圖2所示。

圖2 Hi3516A軟件實現流程圖

鑒于H.264碼流接收端采用FPGA作為主控制器這一場景,以太網幀的構建從前導碼、幀開始符、Mac幀頭、IP層到UDP層均需用戶一一實現,且開始接收以太幀的判定邏輯是識別Mac幀頭的目的Mac地址是否為用戶所設定的。如此,在Hi3516A Linux嵌入式環境下編程實現普通socket協議難以滿足該場景需求,普通socket協議是以用戶IP地址為網絡通信基礎的。與Linux系統可實現復雜的網絡協議棧相比,FPGA僅實現簡單的UDP協議。為避免Linux系統和FPGA平臺對接時與數據傳輸無關的其他協議對系統產生干擾,在此Hi3516A嵌入式平臺使用RAW_SOCKET協議實現UDP編程,用戶指定目的Mac地址使FPGA能準確接收UDP數據包。結果表明,此種方式成功解決了Hi3516A和FPGA平臺的對接問題。

3 FPGA控制邏輯設計

系統由以太網控制模塊,DDR3控制模塊和USB接口控制模塊組成,以太網控制模塊完成H.264碼流的接收,DDR3完成速率匹配和數據緩存功能,USB2.0模塊完成數據PC回傳以便系統功能的測試分析。

3.1 以太網接收控制邏輯

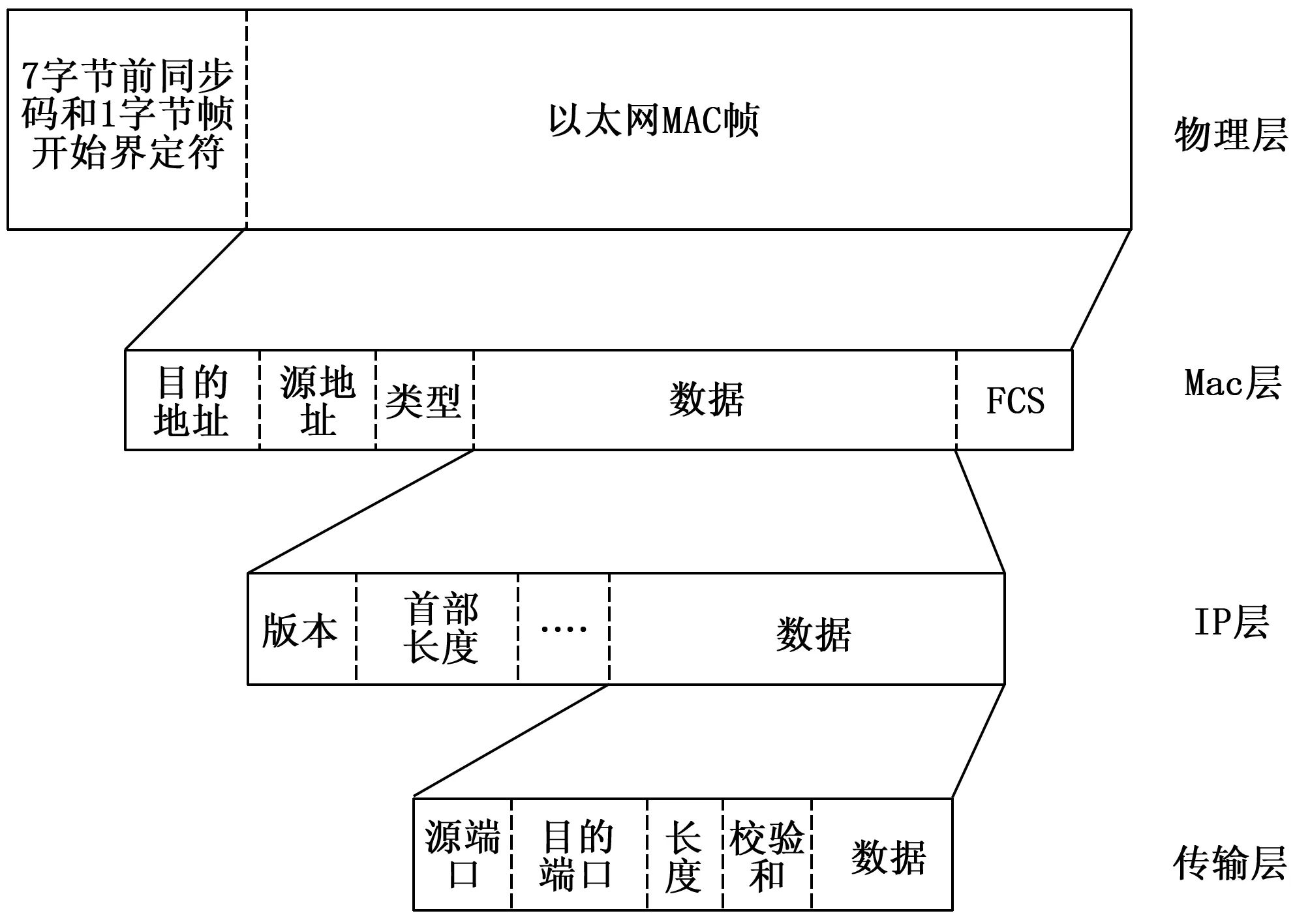

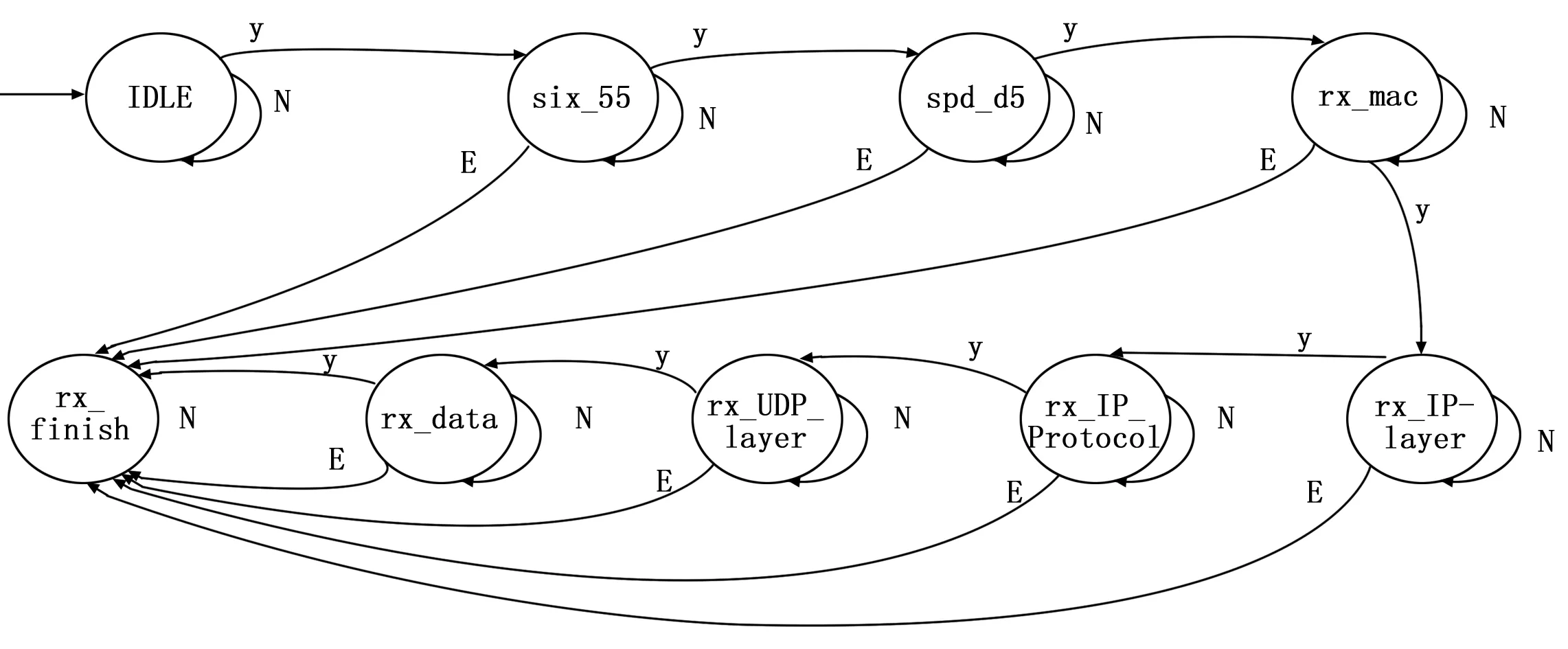

UDP,即用戶數據報協議,適用于圖像視頻傳輸及網絡監控數據交換等對傳輸速度要求較高的場合,UDP協議自帶尋址信息,只提供端到端的數據傳輸服務。與TCP的復雜性相比,UDP協議在FPGA平臺具有更高的可實現性。綜合考慮,系統選用UDP協議來完成碼流接收。完整的以太網幀結構層次和UDP接收數據狀態轉換邏輯如圖3~4所示。

圖3 以太網幀結構層次

圖4 UDP接受數據狀態轉換邏輯

3.2 DDR3控制邏輯

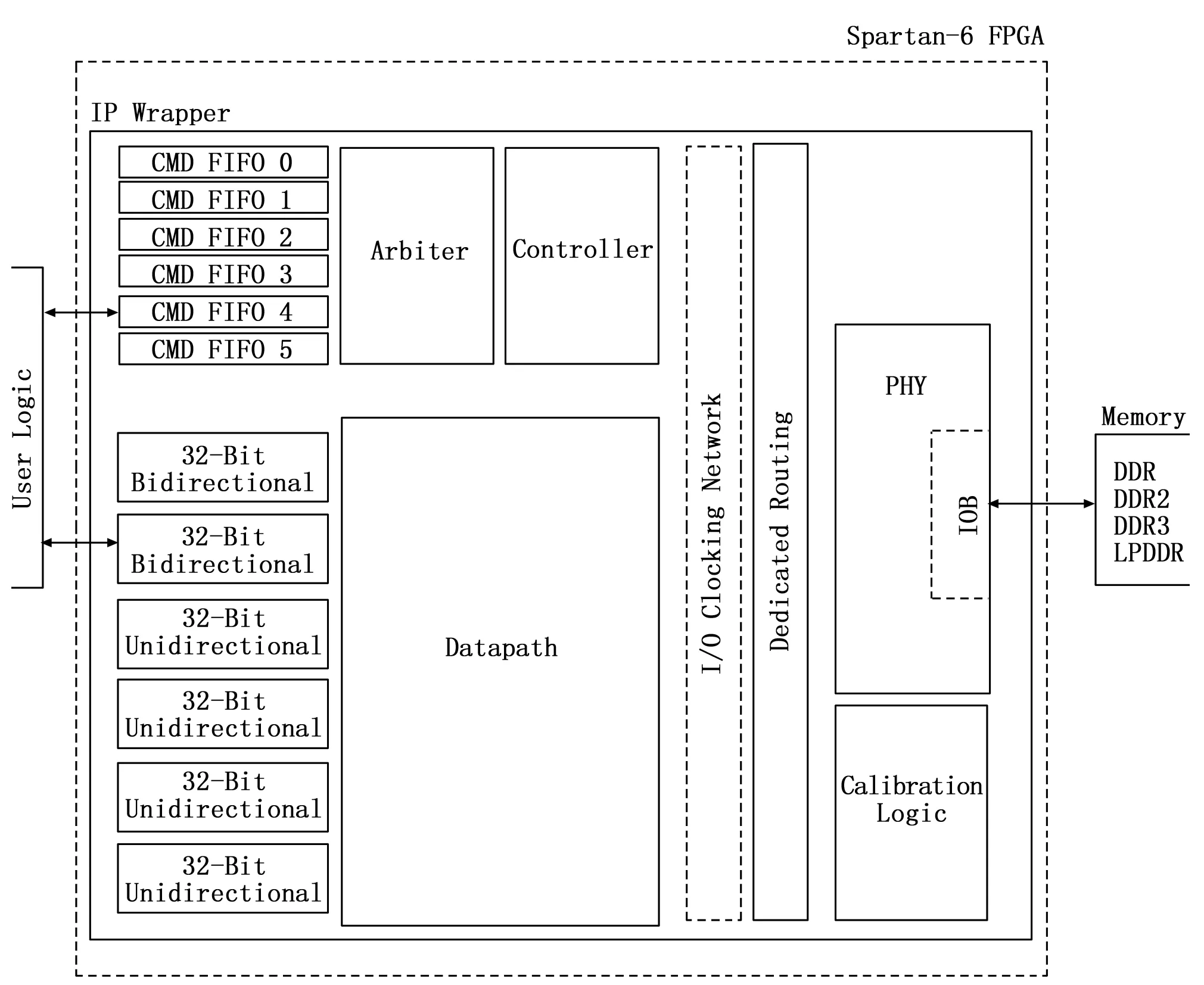

硬件上選用Micron公司2Gbit容量的DDR3-SDRAM存儲芯片MT41J128M16LA-187E作為緩存介質,賽靈思公司ISE開發軟件提供MIG(Memory Interface Generator) IP核來為xc6slx45生成DDR3控制器設計模塊,MIG IP核其邏輯框圖如圖5所示[16]。此種方式屏蔽DDR3[17]復雜的接口時序設計,簡化為簡單命令FIFO和數據FIFO的操作,用戶可通過USER Logic來靈活快速地設計自己的DDR控制邏輯。

圖5 MIG IP核邏輯功能示意圖

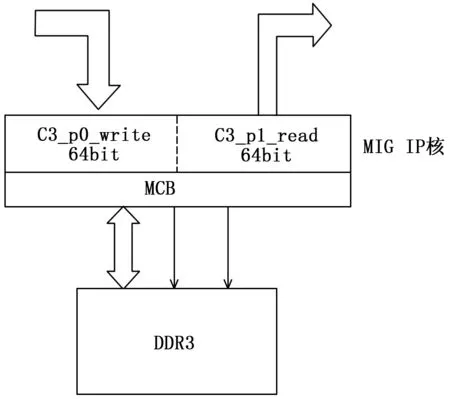

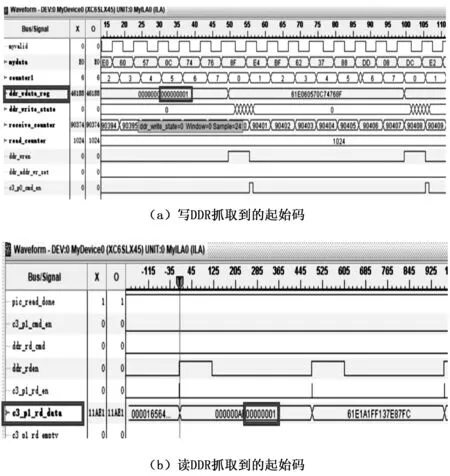

本系統將MIG IP核配置為雙端口實現碼流的邊寫邊讀功能,端口Port 0和Port 1均為64 bit寬度,時鐘速率為312.5 MHz。DDR3寫FIFO時有數據64 bit對齊要求,此模塊將以太網模塊接收的H.264碼流字節組成64 bit寬度,以突發寫模式連續寫進DDR3中,突發長度1。DDR3的讀取控制信號由USB 2.0模塊產生,以突發讀模式讀取DDR3中數據,突發長度為64,即一次讀取512字節(64*64 bit/8)的數據塊。為保證每次讀DDR信號到來時讀FIFO中有足夠的有效數據,本模塊設計了寫計數變量receive_counter和讀計數變量read_counter,只有當寫計數大于讀計數時才生成有效的讀命令信號。圖6為DDR讀寫數據流模式,圖7為DDR讀寫時chipscope抓取到的H.264碼流I幀Nalu單元起始碼(00 00 00 01)。

圖6 DDR讀寫數據流模式

圖7 DDR讀寫過程抓取Nalu起始碼

3.3 USB2.0控制邏輯

采用Cypress公司EZ-USB FX2LP系列的CY7C68013A作為USB接口芯片,此芯片內部集成8 051微控制器,可支持的時鐘為48 MHz,24 MHz,12 MHz,且含有小容量片上RAM,滿足其固件程序的運行。該芯片自帶的4 kB FIFO足以支持其在Master模式或Slave模式下所有數據傳輸應用場合[18-19]。

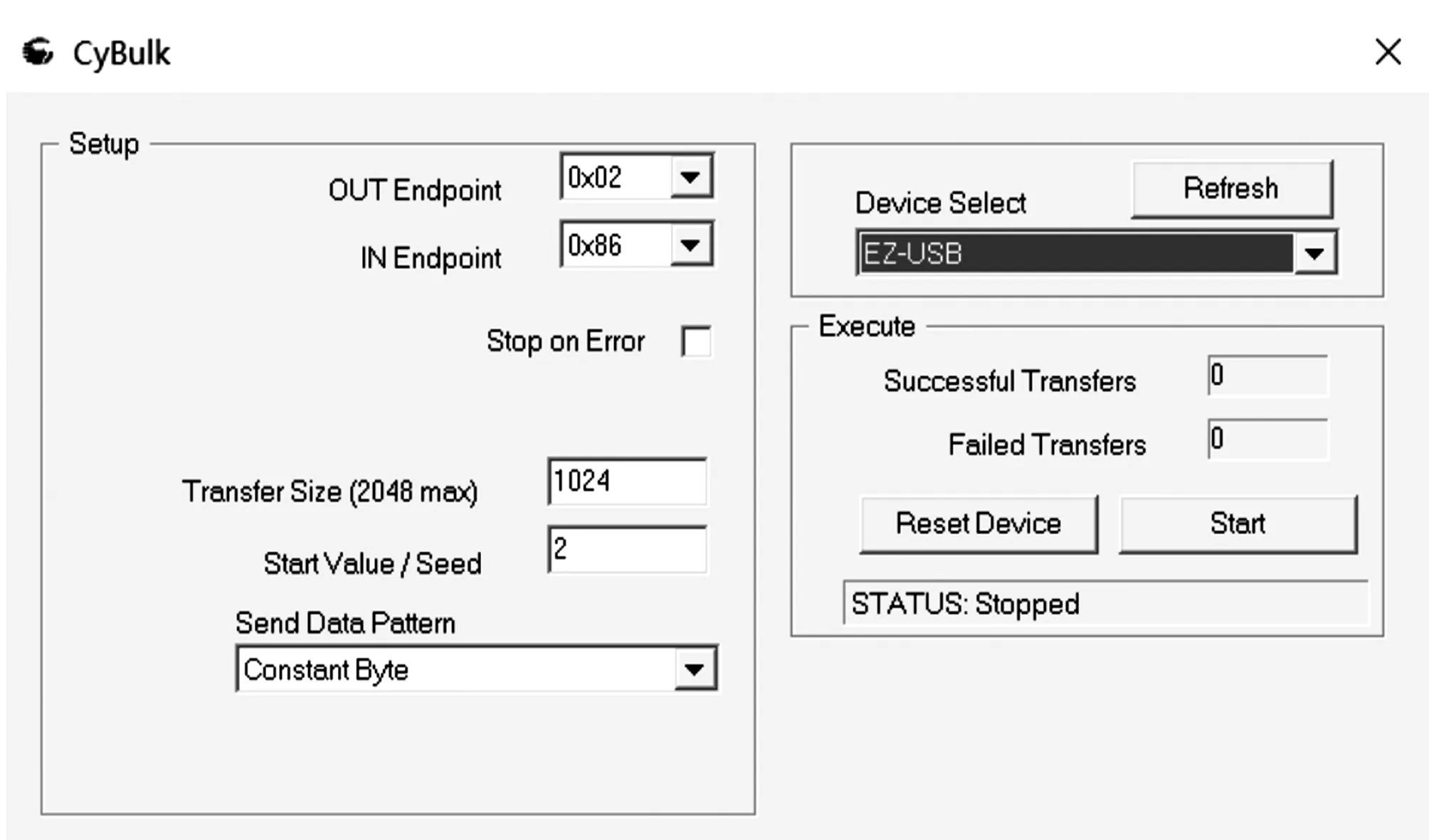

本模塊通過配置FX2固件程序使該芯片工作在Slave FIFO異步讀寫模式,EP2輸出端點和EP6輸入端點各配置2個512 B的FIFO,其中一個FIFO寫滿或讀空的情況下會轉向另一個FIFO的讀寫。FX2固件相關寄存器配置如表1所示。

4 系統功能測試

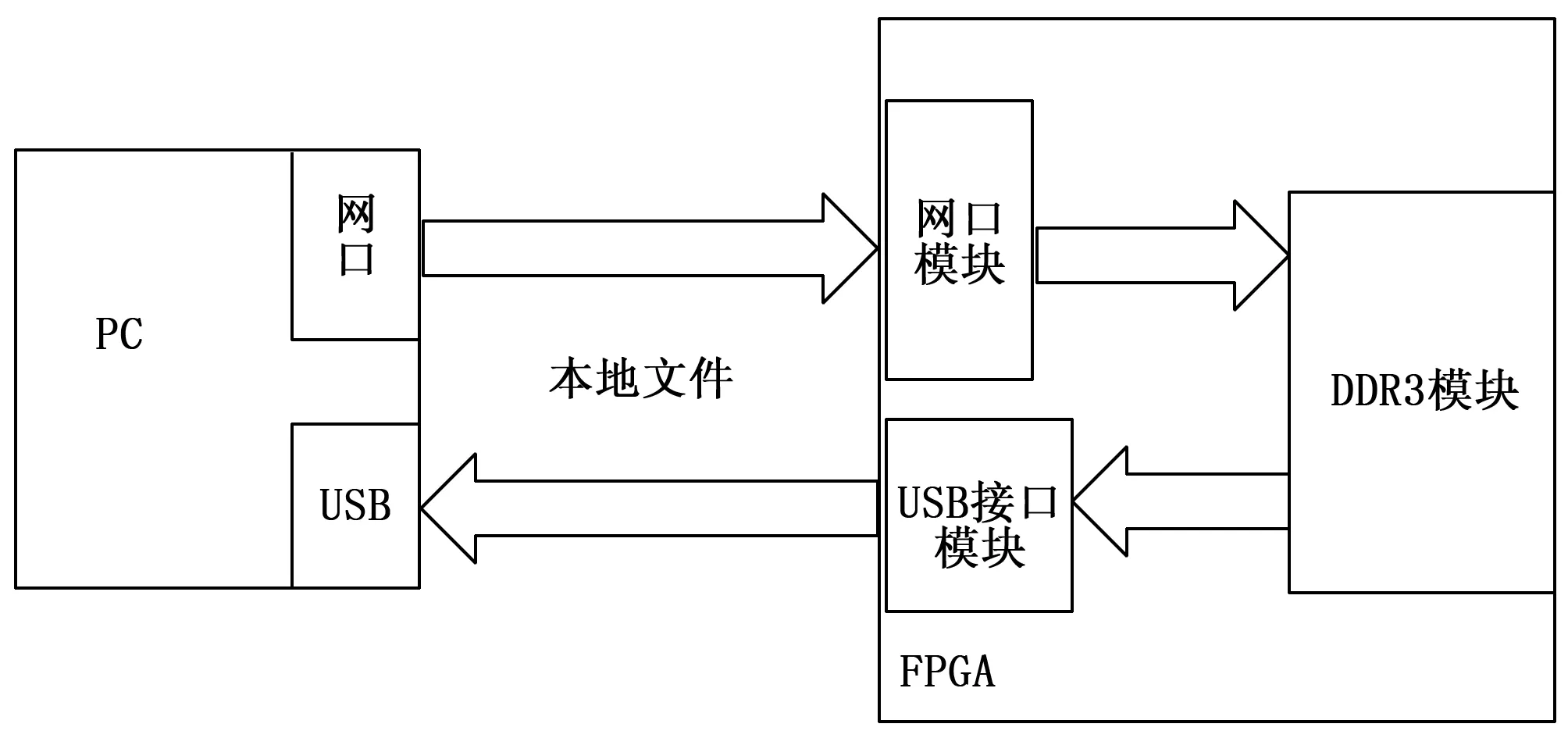

通過修改FX2官方提供的上位機源碼添加接收數據的本地保存功能,此上位機可實現接收成功時數據自動保存到本地文件功能,輸入輸出端口選擇功能,USB設備選擇功能,傳輸數據塊大小選擇功能(僅支持512倍數的數據塊大小),數據接收成功失敗計數功能(以512 B或kB為單位)。界面如圖8所示。

表1 FX2固件相關寄存器配置

圖8 USB上位機界面

系統功能的測試從模擬傳輸本地文件和實際傳輸Hi3516A編碼生成的H.264碼流兩方面進行。模擬本地文件傳輸示意圖如圖9所示,PC端使用RAW_SOCKET編程實現UDP協議,將本地8 023-2 015.pdf文件(55 844 864字節)通過PC端網口發送到此H.264碼流傳輸系統。

圖9 模擬本地文件傳輸示意圖

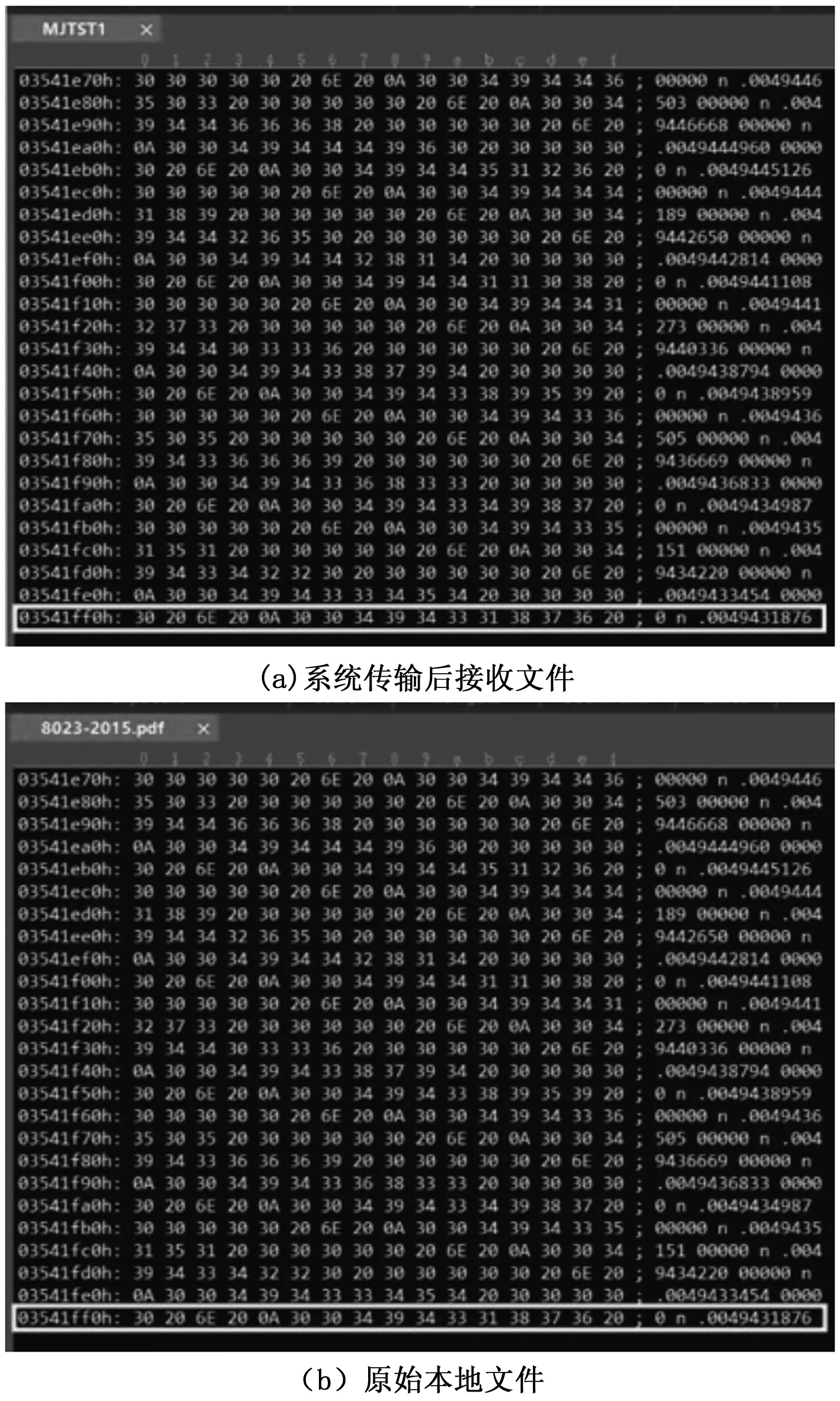

通過對比原始文件和上位機接收到的數據文件來測試系統傳輸數據的完整性。使用UltraEdit軟件打開原始文件和接收到的數據文件,對比結果如圖10所示。

圖10 上位機接收文件和原始本地文件數據對比

可發現經系統傳輸后接收文件從開始到最后地址0x03541ff0和原始文件數據相匹配,數據大小皆為55 844 864字節,因此可得出數據傳輸完整的結論。

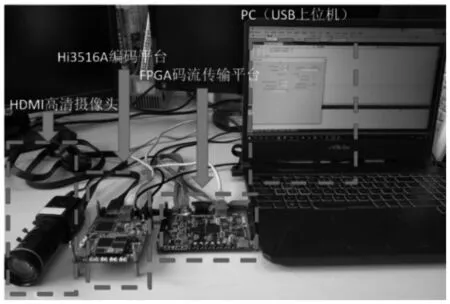

H.264碼流傳輸實物圖如圖11所示。

圖11 系統實物圖

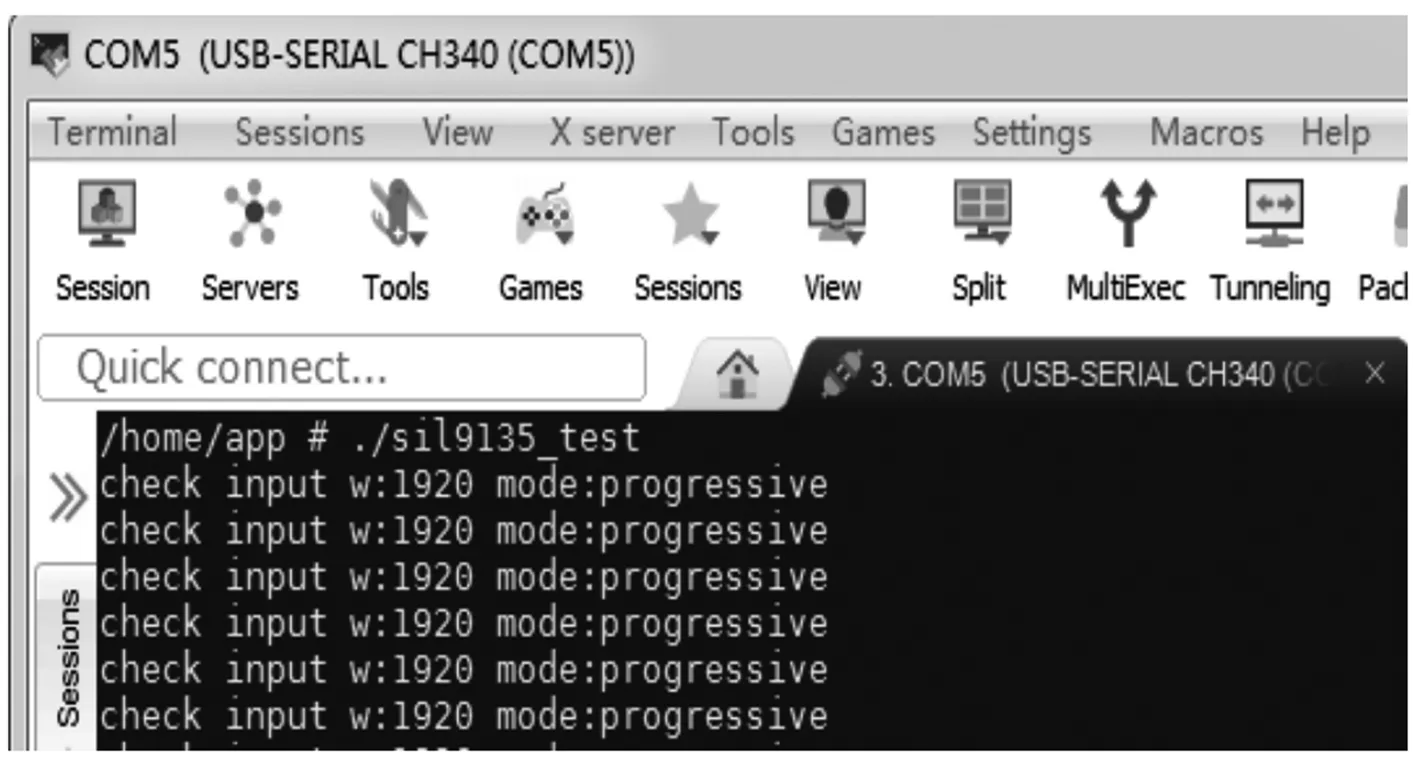

HDMI攝像頭,Hi3516A,FPGA依次上電,系統穩定3 s后,在Hi3516A終端串口輸入命令./sil9135_test,測試HDMI攝像頭是否成功識別,如圖12所示。

圖12 HDMI攝像頭視頻輸入測試

串口打印結果mode:progressive表示視頻為逐行掃描格式,w:1920表示視頻分辨率為1 920*1 080。終端輸入./Hi3516A_hdmi_rawsocket命令啟動系統編碼,2 s等待編碼延遲后,啟動USB上位機接收碼流數據,上位機顯示接收數據量大于51 200,即50 MB字節時,停止接收數據。

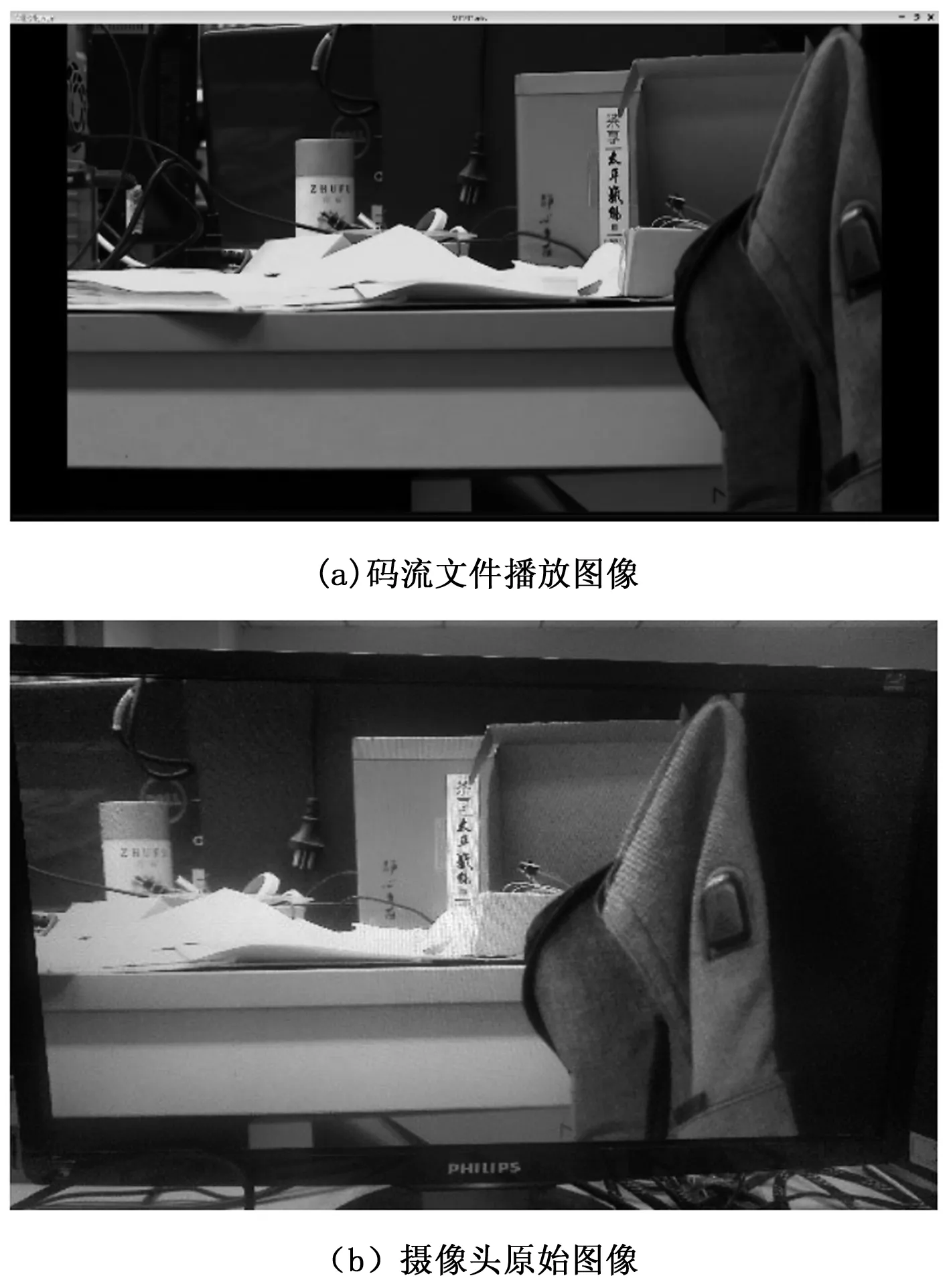

通過MilkPlayer軟件播放保存的碼流文件,系統傳輸后碼流文件播放和攝像頭原始圖像顯示對比如圖13所示。

圖13 碼流文件播放圖像和攝像頭原始圖像對比效果

由圖13可知,畫面顯示完整,細節清晰,播放流暢,無明顯卡頓及花屏綠屏等丟幀亂碼現象。

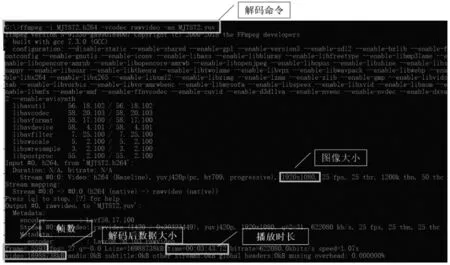

利用FFmpeg軟件[20]解碼上位機接收到的碼流文件為YUV4:2:0格式,解碼命令為ffmpeg -i MJTST.h264 -vcodecrawvideo-an MJTST.yuv。參數i指定輸入文件,vcodec指定解碼對象為視頻文件,rawvideo指定解碼為原始yuv格式視頻數據。如圖14所示。

圖14 FFmpeg解碼H.264碼流文件

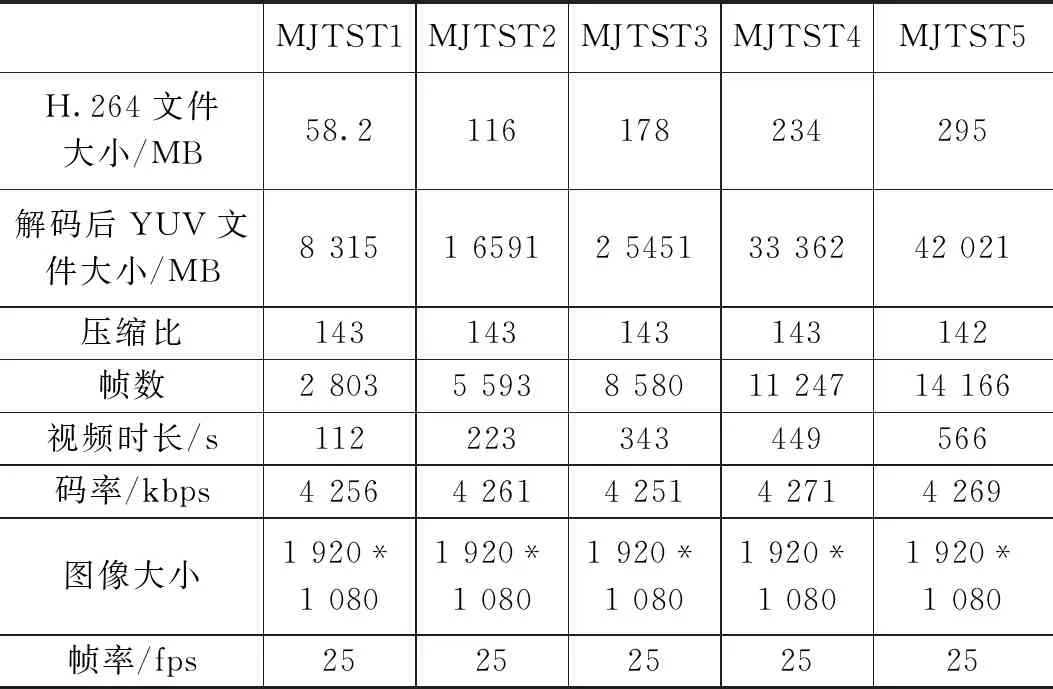

如圖14所示,從解碼結果中可提取視頻時長、圖像大小、比特率、幀率、幀數、文件大小等信息,統計結果如表2所示。

表2 FFmpeg解碼H.264碼流文件結果統計

其中,平均碼率為H.264文件大小與視頻時長的比值,幀率為幀數與視頻時長的比值,壓縮比為解碼后YUV文件大小與H.264文件大小的比值。由表2統計結果可知圖像大小為1 920*1 080,視頻幀率為25 fps,符合編碼設定參數,由5組數據可計算平均碼率為4 261.6 kbps,與設定的碼率4 096相比,有(4 261.6-4 096)/4 096=4%的誤差,平均壓縮比為143,編碼效果良好。

經測試,系統在12 h左右本地保存數據量達22.3 GB,24 h左右數據量達43.5 GB,且播放存在部分卡頓現象,2 s左右能自動恢復流暢播放,可認為系統能夠完成長時間傳輸及存儲碼流的任務。

綜合上述分析,可得出系統數據傳輸完整,編碼效果良好,傳輸及存儲碼流時長達到設計要求的結論,此系統成功實現了H.264碼流實時傳輸的設計任務。

5 結束語

此設計實現的H.264碼流傳輸系統能成功對接Hi3516A平臺的網口,將編碼碼流通過FPGA進行處理和轉發,在海思半導體平臺原有IP攝像機和網絡流媒體應用方案的基礎上,極大拓展了其應用可能性,如在航空航天等一些需要大量圖像數據遠距離傳輸的場合,此系統可突破原網絡雙絞線傳輸百米的限制,將圖像數據從高空到地面遠距離回傳以進行后續的分析利用。本系統也存在需改進之處,如使用USB2.0接口回傳數據,在后續的研究開發中,可將其拓展為已相當成熟的USB3.0接口,此處Hi3516 A 4 Mbps的輸出碼流速率情況下USB2.0接口也足以滿足傳輸速度需求。另外系統還可使用LVDS、RS485/422等其它接口進行數據的轉發處理以增加其多場合實用性。