時間觸發(fā)光纖通道節(jié)點設(shè)計與實現(xiàn)*

詹 鵬,周 新

(1.中國西南電子技術(shù)研究所,成都 610036;2.空軍裝備部駐成都地區(qū)第三軍事代表室,成都 610036)

0 引 言

航空電子系統(tǒng)的發(fā)展經(jīng)歷了分立式、聯(lián)合式到綜合化的發(fā)展過程,機載綜合化電子系統(tǒng)變得越來越復(fù)雜。作為航電系統(tǒng)信息傳輸?shù)耐ǖ溃瑱C載總線網(wǎng)絡(luò)變得越來越重要,綜合化航電系統(tǒng)對機載總線網(wǎng)絡(luò)的傳輸速率、確定性、可靠性等都提出了較高要求。常用的控制器局域網(wǎng)(Controller Area Network,CAN)、以太網(wǎng)等總線網(wǎng)絡(luò)采用了事件觸發(fā)傳輸方式,數(shù)據(jù)傳輸時刻是隨機的,當多個節(jié)點同時發(fā)起傳輸時可能發(fā)生沖突,在網(wǎng)絡(luò)負荷較重時,數(shù)據(jù)傳輸?shù)募皶r性無法得到保證。時間觸發(fā)傳輸通過分時復(fù)用的方法,將整個信道的傳輸時間劃分為若干時隙并分配給各個節(jié)點,可有效避免數(shù)據(jù)包爭用物理鏈路,解決了網(wǎng)絡(luò)可能存在的沖突、數(shù)據(jù)幀擁塞排隊問題。時間觸發(fā)傳輸通過全局時間同步實現(xiàn)無沖突的數(shù)據(jù)傳輸,數(shù)據(jù)傳輸?shù)淖畲髸r延是可預(yù)知的。時間觸發(fā)傳輸與事件觸發(fā)傳輸相比,在傳輸確定性上有很大優(yōu)勢。采用時間觸發(fā)傳輸機制的常用總線包括時間觸發(fā)協(xié)議(Time-triggered Protocol,TTP)、時間觸發(fā)CAN(Time-triggered CAN,TT-CAN)、時間觸發(fā)以太網(wǎng)(Time-triggered Ethernet,TTE)[1]等,并受到了廣泛的關(guān)注和應(yīng)用。

光纖通道(Fiber Channel,F(xiàn)C)是美國國家標準委員會制定的高速串行傳輸協(xié)議。FC具備高帶寬、高可靠性、高穩(wěn)定性等優(yōu)點,采用了光纖互連,抗電磁干擾能力強,業(yè)界在此基礎(chǔ)上提出了光纖通道航空電子環(huán)境(Fibre Channel Avionics Environment,FC-AE)協(xié)議族。FC在F-35、“長弓阿帕奇”等項目中已得到了成功應(yīng)用。FC采用了交換式全雙工通信方式,不存在數(shù)據(jù)沖突問題,但交換機的存儲轉(zhuǎn)發(fā)機制同樣使通信延遲具有不確定性(網(wǎng)絡(luò)交換排隊延遲)。普通的FC采用事件觸發(fā)傳輸方式,由于傳輸速率較高,當網(wǎng)絡(luò)負荷較低時數(shù)據(jù)傳輸時延較低,可滿足常規(guī)應(yīng)用需求,然而在網(wǎng)絡(luò)負荷較重的場合,數(shù)據(jù)傳輸時延的影響就會凸顯出來。借鑒時間觸發(fā)傳輸思想,可在FC網(wǎng)絡(luò)中引入時間觸發(fā)傳輸機制,從而提高數(shù)據(jù)傳輸?shù)臅r間確定性。

考慮到FC傳輸確定性問題,文獻[2]提出了一種基于令牌桶的優(yōu)先級和加權(quán)輪轉(zhuǎn)相結(jié)合的調(diào)度算法,以提高FC的實時性。針對時間觸發(fā)傳輸?shù)臅r隙分配問題,文獻[3]提出了基于稀疏模型的時間觸發(fā)光纖網(wǎng)絡(luò)調(diào)度方案,提高傳輸確定性。針對FC的協(xié)議實現(xiàn)問題,文獻[4]基于FPGA設(shè)計實現(xiàn)了普通光纖通道數(shù)據(jù)收發(fā)系統(tǒng);文獻[5-6]采用FPGA設(shè)計實現(xiàn)了FC節(jié)點;文獻[7]基于FPGA實現(xiàn)了FC協(xié)議CRC的并行高效算法,使消耗的FPGA邏輯資源更少;文獻[8]基于FPGA設(shè)計實現(xiàn)了FC協(xié)議分析器,具備FC協(xié)議與以太網(wǎng)協(xié)議的轉(zhuǎn)換功能。針對交換機設(shè)計實現(xiàn)問題,文獻[9]設(shè)計實現(xiàn)了基于時間調(diào)度網(wǎng)絡(luò)的光纖通道交換機,文獻[10]基于FPGA實現(xiàn)了一種高性能、大容量的48口FC交換機。

當前介紹FC節(jié)點、交換機的設(shè)計與實現(xiàn)的文獻較多,部分文獻提出了時間觸發(fā)傳輸概念、方案,但針對時間觸發(fā)光纖通道從整體傳輸方案、網(wǎng)絡(luò)同步、具體邏輯設(shè)計實現(xiàn)、到實物測試驗證進行系統(tǒng)性描述的公開文獻較少。本文基于時間觸發(fā)傳輸思想,在普通FC總線的基礎(chǔ)上對傳輸協(xié)議進行改進,增加時間觸發(fā)傳輸功能,采用主從方式實現(xiàn)網(wǎng)絡(luò)時間同步,僅需對網(wǎng)絡(luò)節(jié)點終端進行協(xié)議改造的方法,提出了相應(yīng)的設(shè)計方案,然后在FPGA上進行了邏輯實現(xiàn),最后在實物平臺上進行了測試驗證。

1 時間觸發(fā)傳輸設(shè)計與實現(xiàn)

1.1 總體方案設(shè)計

本文基于時間觸發(fā)傳輸思想,在網(wǎng)絡(luò)節(jié)點時間同步的基礎(chǔ)上,將總線傳輸按周期進行劃分,每個周期預(yù)先規(guī)劃相應(yīng)的時隙給各節(jié)點(即發(fā)送時間表),所有數(shù)據(jù)傳輸都由時間表來驅(qū)動。網(wǎng)絡(luò)節(jié)點發(fā)送時間表的設(shè)計規(guī)劃原則:在各個節(jié)點的發(fā)送時隙內(nèi)獨占鏈路資源,其他節(jié)點均不能使用該鏈路(對應(yīng)的接收節(jié)點同一時刻僅接收來自唯一一個節(jié)點的數(shù)據(jù),即不會出現(xiàn)同一時刻兩個節(jié)點同時向同一節(jié)點發(fā)送數(shù)據(jù))。在交換式FC網(wǎng)絡(luò)中,交換機采用了空分交換結(jié)構(gòu),所以網(wǎng)絡(luò)中存在多條傳輸鏈路可以互不影響地同時工作,采用手動方式設(shè)計發(fā)送時間表會較為復(fù)雜,可編寫相應(yīng)的時間調(diào)度算法程序來規(guī)劃時隙。各個節(jié)點按照預(yù)先規(guī)劃的時隙可以互不沖突地使用網(wǎng)絡(luò)資源,在交換機中就不會存在數(shù)據(jù)緩沖、排隊的現(xiàn)象,保證了數(shù)據(jù)傳輸?shù)拇_定性。交換機僅需按照路由進行全速轉(zhuǎn)發(fā)即可,對交換機也無特殊要求,采用普通FC交換機即可。此外,根據(jù)規(guī)劃好的發(fā)送時間表,可以方便地得到各個節(jié)點的接收時間表(不同時隙接收來自不同節(jié)點的數(shù)據(jù)包)。節(jié)點在接收到數(shù)據(jù)包時,需根據(jù)接收時間表對數(shù)據(jù)來源進行驗證,從而提供了一種對數(shù)據(jù)傳輸合規(guī)性的檢測。

普通FC協(xié)議包括5層:FC-0定義了物理連接的特性、速率;FC-1定義了傳輸字的組成,傳輸信號的編解碼方式以及錯誤控制;FC-2定義了幀、數(shù)據(jù)包的構(gòu)成及傳輸方式;FC-3為通用服務(wù)層,作為預(yù)留擴展層;FC-4定義了不同的上層協(xié)議映射方式。本文提出的時間觸發(fā)傳輸FC總線基于普通FC協(xié)議,總線協(xié)議分層如圖1所示。

圖1 時間觸發(fā)光纖通道協(xié)議分層

所提出的時間觸發(fā)光纖通道協(xié)議在原FC協(xié)議的基礎(chǔ)上增加了一個時間觸發(fā)控制管理層,用于實現(xiàn)時間觸發(fā)傳輸功能,其他層次與普通FC相同,所以本文提出的時間觸發(fā)光纖通道協(xié)議兼容于普通FC。時間觸發(fā)控制管理層主要實現(xiàn)網(wǎng)絡(luò)節(jié)點的時間同步,以及節(jié)點的時間觸發(fā)數(shù)據(jù)傳輸,該層不會對收發(fā)的數(shù)據(jù)包內(nèi)容作任何修改,僅通過網(wǎng)絡(luò)時間同步后,實現(xiàn)對時間觸發(fā)傳輸?shù)目刂疲纯刂茢?shù)據(jù)包在允許的發(fā)送時間窗口將數(shù)據(jù)發(fā)送出去,而在非發(fā)送時段則對數(shù)據(jù)包進行緩存,并按照接收時間表對接收數(shù)據(jù)進行合規(guī)性檢測。

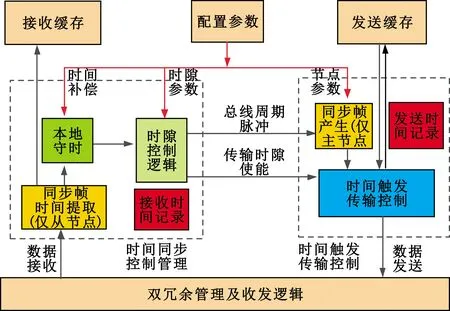

基于普通FC總線協(xié)議,本文提出的時間觸發(fā)傳輸節(jié)點的邏輯設(shè)計方案如圖2所示。時間觸發(fā)FC協(xié)議在FPGA邏輯上實現(xiàn),主要包括處理器接口、發(fā)送緩存、時間觸發(fā)傳輸控制、接收緩存、時間同步控制管理、配置參數(shù)、雙冗余管理、FC鏈路收發(fā)等邏輯功能單元。

圖2 節(jié)點整體設(shè)計方案框圖

當有數(shù)據(jù)包需要發(fā)送時,通過處理器接口將數(shù)據(jù)寫入到發(fā)送緩存中,在時間觸發(fā)傳輸控制模塊的管理下將發(fā)送緩存中的數(shù)據(jù)取出并送到雙冗余管理模塊中;雙冗余管理模塊根據(jù)配置實現(xiàn)對雙路或者單路FC數(shù)據(jù)的輸出,數(shù)據(jù)包經(jīng)過FC收發(fā)邏輯和光電轉(zhuǎn)換后輸出到網(wǎng)絡(luò)上。

當接收到數(shù)據(jù)包時,數(shù)據(jù)通過光電模塊、FC鏈路收發(fā)邏輯后,雙冗余管理模塊根據(jù)節(jié)點冗余配置將數(shù)據(jù)送到接收邏輯中;時間同步控制管理模塊對接收數(shù)據(jù)進行甄別,當檢測到為同步幀時則取出數(shù)據(jù)包中的同步時間信息,并更新本地時鐘;若為普通數(shù)據(jù)包則經(jīng)過合規(guī)性檢測后送入接收緩存中,對數(shù)據(jù)包進行緩存后通過處理器接口送給處理器。

其中時間觸發(fā)傳輸控制、時間同步控制管理兩個功能模塊是實現(xiàn)時間觸發(fā)傳輸?shù)年P(guān)鍵。采用本設(shè)計實現(xiàn)的時間觸發(fā)光纖通道總線網(wǎng)絡(luò)中的節(jié)點分為主節(jié)點和從節(jié)點兩類(網(wǎng)絡(luò)中主節(jié)點僅有一個,其他均為從節(jié)點),所以主/從節(jié)點在邏輯實現(xiàn)上存在一定的差異。

1.2 時間同步設(shè)計

為了實現(xiàn)時間觸發(fā)傳輸,各個節(jié)點之間需要實現(xiàn)精確的時間同步,使網(wǎng)絡(luò)中各節(jié)點的時間同步到一個統(tǒng)一的參考時間。時間同步通常可采用硬件和軟件兩種方式實現(xiàn),硬件同步方法精度高,但額外的硬件增大了開銷;軟件同步方法采用算法實現(xiàn),成本低且較靈活。

本文采用主從時間同步的軟件實現(xiàn)方案,所有節(jié)點同步到主節(jié)點的時間,并采用軟件進行時間偏移補償,實現(xiàn)精確的時間同步。主從時間同步方案如圖3所示,網(wǎng)絡(luò)中設(shè)置一個主節(jié)點,其他節(jié)點為從節(jié)點,所有節(jié)點均以主節(jié)點的時間為基準,主節(jié)點采用分發(fā)同步幀(數(shù)據(jù)幀中包含時間信息)的方式實現(xiàn)整個網(wǎng)絡(luò)的時間同步。

圖3 時間同步示意圖

為了維持各個節(jié)點時間的實時同步,主節(jié)點需要周期性地廣播同步幀,同步幀的發(fā)送周期為總線周期,同步幀中包含了主節(jié)點的時間信息。在未收到同步幀的時間內(nèi),從節(jié)點靠本地時鐘進行守時;當收到同步幀后,則用接收到的時間對本地時間進行更新。采用該方式可實現(xiàn)網(wǎng)絡(luò)中所有節(jié)點的時間同步,且該時間同步方式無需對交換機進行修改,通用的FC交換機就可以滿足應(yīng)用要求,對網(wǎng)絡(luò)硬件的改動較小。采用如上所述的分發(fā)同步幀的方式,整個網(wǎng)絡(luò)的節(jié)點可實現(xiàn)時間的初同步,但同步時間精度不高,從節(jié)點與主節(jié)點之間存在一個相對固定的時間偏差,該時間偏差主要由數(shù)據(jù)包收/發(fā)時延、交換路由時延、線纜傳輸時延組成,偏差值通常為微秒級。

同步幀由主節(jié)點經(jīng)過交換機后分發(fā)到各個從節(jié)點,由于各個從節(jié)點與主節(jié)點之間的傳輸路徑不同,該時延也不相同。為了提高網(wǎng)絡(luò)時間同步精度,需要對該傳輸時延進行測量和補償。本設(shè)計采用與IEEE1588類似的方法對時間偏移進行測量[11],其測量原理如圖4所示。

圖4 時間偏移測量原理

時間偏移具體測量分兩步:首先主節(jié)點向從節(jié)點發(fā)送一個數(shù)據(jù)包,主節(jié)點記錄下發(fā)送時間t1,從節(jié)點記錄下接收時間t2;然后從節(jié)點向主節(jié)點發(fā)送一個數(shù)據(jù)包,從節(jié)點記錄下發(fā)送時間t3,主節(jié)點記錄下接收時間t4。主節(jié)點通過發(fā)送數(shù)據(jù)幀的方式將記錄的時間信息發(fā)送給從節(jié)點,通過式(1)計算后就可得到主從節(jié)點的時間偏差值Δt。

(1)

采用以上方法對每個從節(jié)點的時間偏移都進行獨立的測量,然后在各從節(jié)點端分別進行補償,從而提高時間同步精度。時間偏移測量過程中為了避免引入處理器軟件產(chǎn)生的抖動,時間點記錄均采用FPGA邏輯實現(xiàn)。此外,網(wǎng)絡(luò)拓撲固定后,各從節(jié)點與主節(jié)點之間的時延也相對固定,所以可以僅測量一次時間偏移,并將補償數(shù)據(jù)存儲起來,后續(xù)在網(wǎng)絡(luò)拓撲不變的情況下可直接使用。

網(wǎng)絡(luò)節(jié)點時間同步傳輸?shù)腇PGA邏輯具體實現(xiàn)方案如圖5所示。

圖5 時間同步傳輸設(shè)計

時間同步控制管理主要完成本地守時、接收包的時間記錄(用于時間補償)、根據(jù)配置參數(shù)產(chǎn)生傳輸時隙控制信號。若節(jié)點為主節(jié)點,還需要送出總線周期信號,用于觸發(fā)同步幀的產(chǎn)生;對于從節(jié)點而言,則應(yīng)具有同步幀時間提取功能,可以從總線上接收的同步幀中提取出時間信息,結(jié)合時間補償參數(shù)后對本地時間進行周期更新。

時間觸發(fā)傳輸控制主要完成數(shù)據(jù)包發(fā)送時間記錄(用于時間同步補償)、時間觸發(fā)傳輸控制,根據(jù)傳輸時隙使能信號控制數(shù)據(jù)發(fā)送,僅在配置的時隙內(nèi)允許數(shù)據(jù)包的發(fā)送,其他時間則禁止發(fā)送,未發(fā)送的數(shù)據(jù)包則在發(fā)送緩存中等待傳輸時隙的開啟;對于主節(jié)點而言,還具備同步幀產(chǎn)生的功能,根據(jù)送來的總線周期脈沖信號,周期性向網(wǎng)絡(luò)上廣播同步幀,將主節(jié)點的時間信息通過同步幀發(fā)送出去。

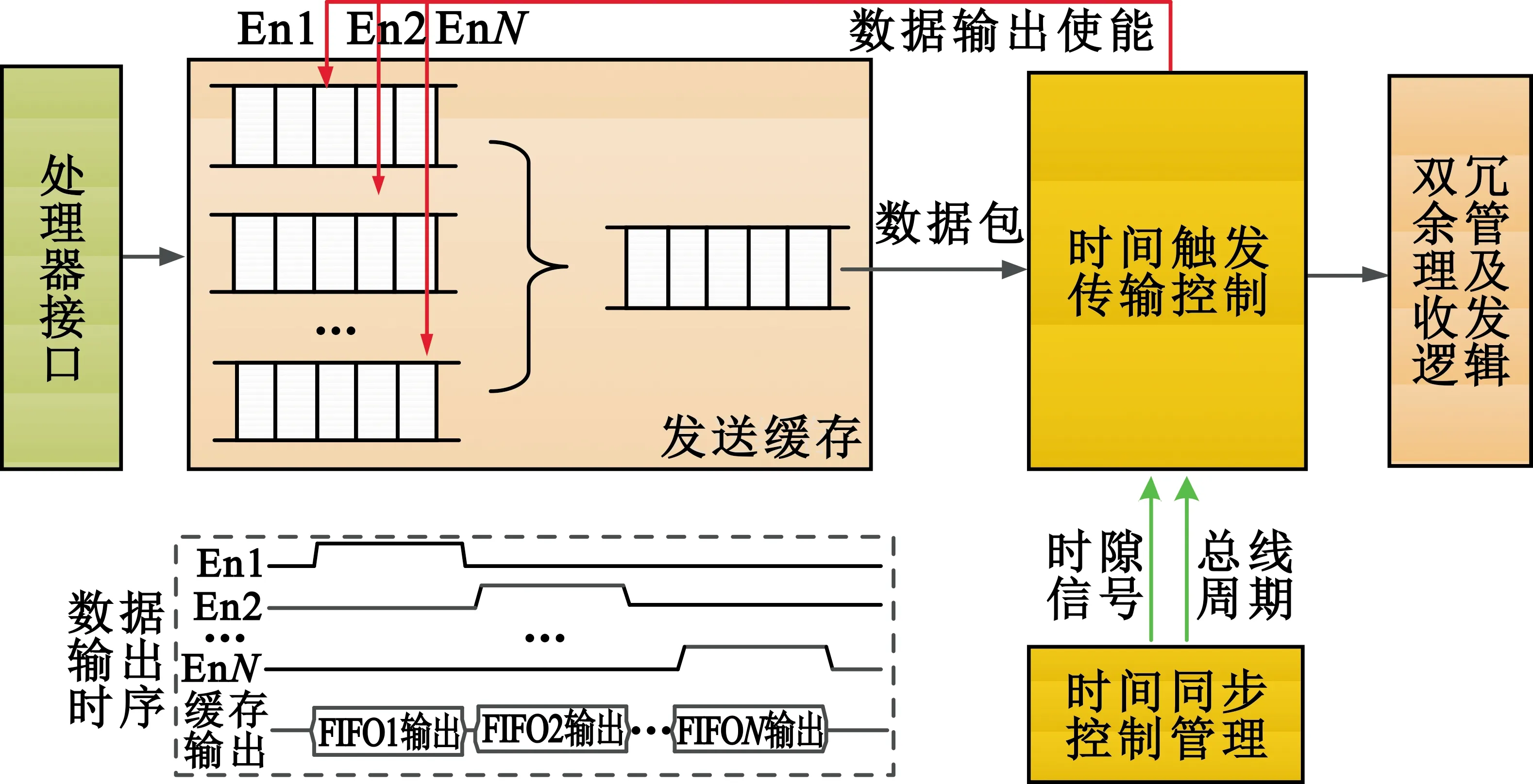

1.3 多緩存時間觸發(fā)傳輸設(shè)計

時間觸發(fā)傳輸機制通過分時復(fù)用的方法,解決了網(wǎng)絡(luò)可能存在的沖突、數(shù)據(jù)幀擁塞排隊問題,節(jié)點分時獨占網(wǎng)絡(luò)可以很好地解決網(wǎng)絡(luò)數(shù)據(jù)傳輸?shù)牟淮_定性問題。由于FC為全雙工交換網(wǎng)絡(luò),且采用了空分交換結(jié)構(gòu)的交換機,當兩個節(jié)點通過交換機傳輸數(shù)據(jù)時,通過交換機其他端口進行互連的多對節(jié)點之間仍可同時傳輸數(shù)據(jù),且互不影響,即多個節(jié)點之間可以同時進行數(shù)據(jù)傳輸,數(shù)據(jù)包傳輸?shù)哪康牡刂肪幌嗤K裕诳辗纸粨Q結(jié)構(gòu)的網(wǎng)絡(luò)中,對于節(jié)點時隙的分配不應(yīng)該是每個節(jié)點獨占整個網(wǎng)絡(luò)資源,而是獨占某一條鏈路資源。因此,根據(jù)時隙規(guī)劃,在一個總線周期內(nèi),某一節(jié)點發(fā)送到不同其他節(jié)點的傳輸時隙是不同的,在某個時隙僅允許傳輸?shù)揭?guī)定的節(jié)點。因此,若數(shù)據(jù)包發(fā)送仍然采用單發(fā)送緩存的方式則無法滿足應(yīng)用的需求,會存在排隊阻塞的問題。為此,本文實現(xiàn)方案中采用了多緩存方式,以滿足基于空分交換網(wǎng)絡(luò)的時間觸發(fā)傳輸,邏輯設(shè)計方案如圖6所示。

圖6 多緩存結(jié)構(gòu)時間觸發(fā)傳輸邏輯設(shè)計方案

網(wǎng)絡(luò)中每個節(jié)點均配置多個發(fā)送緩沖區(qū),緩沖區(qū)按照數(shù)據(jù)包發(fā)送的目的地址進行分類。在一個總線周期內(nèi),每個發(fā)送緩沖區(qū)允許輸出的時隙不同,且互不重疊,允許輸出的時隙通過預(yù)先離線規(guī)劃進行配置。上層應(yīng)用將待發(fā)送的數(shù)據(jù)按目的地址分流到不同的緩沖區(qū)進行緩存,時間觸發(fā)傳輸控制根據(jù)節(jié)點時隙配置參數(shù),分時取出不同緩沖區(qū)中的數(shù)據(jù)發(fā)送出去。

2 實驗及結(jié)論

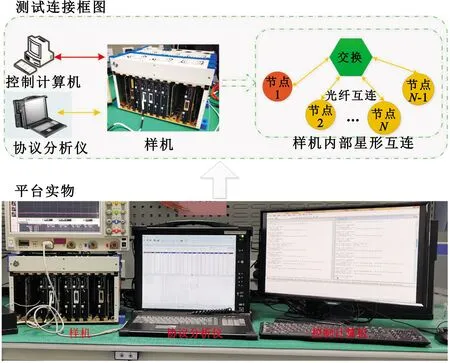

為驗證文中提出的時間觸發(fā)傳輸設(shè)計與實現(xiàn)方案的正確性和有效性,搭建了測試驗證環(huán)境,如圖7所示,主要包括樣機、控制計算機和協(xié)議分析儀,選擇樣機中的節(jié)點進行測試驗證,組建星形交換網(wǎng)絡(luò),由控制計算機給節(jié)點輸入操作指令,使網(wǎng)絡(luò)中的節(jié)點按照設(shè)定的時隙傳輸數(shù)據(jù),使用協(xié)議分析儀可對網(wǎng)絡(luò)上傳輸?shù)臄?shù)據(jù)包進行捕獲、存儲和分析。

圖7 實物平臺及測試連接框圖

樣機交換網(wǎng)絡(luò)中選取4個節(jié)點,包括1個主節(jié)點和3個從節(jié)點,節(jié)點ID及時隙分配信息如表1所示。表中的偏移表示相對于同步幀的時間偏移,3個從節(jié)點每個周期發(fā)送一次數(shù)據(jù)給主節(jié)點,鏈路速率設(shè)置為2 Gb/s。

表1 節(jié)點配置表

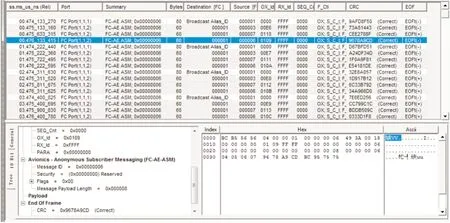

為便于操作和觀察,總線周期設(shè)置為1 s,控制計算機通過串口命令控制從節(jié)點的數(shù)據(jù)發(fā)送,約1 s啟動一次數(shù)據(jù)傳輸,通過協(xié)議分析儀對主節(jié)點的端口通信數(shù)據(jù)進行抓取。

圖8為從節(jié)點不發(fā)送數(shù)據(jù)時主節(jié)點周期性廣播同步幀的情況。從抓取的數(shù)據(jù)包可以看出,同步幀每1 s發(fā)送一次,周期的時間精度受主節(jié)點本地時鐘影響(1 s誤差接近100 μs,精度10-7),在工程應(yīng)用中可以采用高精度時鐘源,從而提高網(wǎng)絡(luò)時間精度。

圖8 同步幀傳輸截圖

圖9為3個從節(jié)點在時間觸發(fā)控制下傳輸數(shù)據(jù)的情況。在主節(jié)點時間同步控制下,按照分配時隙,3個從節(jié)點的數(shù)據(jù)包在相對于同步幀分別偏移約1 ms、1.5 ms、2 ms的時隙完成數(shù)據(jù)傳輸,而在其他非規(guī)劃時隙內(nèi)則不發(fā)送數(shù)據(jù)包(從圖中第一列的時間關(guān)系可以看出,受時間同步精度的影響,傳輸時間存在亞微秒級的誤差),符合分配的節(jié)點傳輸時隙,驗證了時間觸發(fā)傳輸功能的正確性和可行性。

圖9 時間觸發(fā)傳輸測試截圖

3 結(jié) 論

普通FC總線采用事件觸發(fā)傳輸,存在數(shù)據(jù)傳輸時間確定性差的問題。時間觸發(fā)傳輸能夠有效避免鏈路爭用導(dǎo)致的數(shù)據(jù)阻塞,保證了網(wǎng)絡(luò)數(shù)據(jù)傳輸?shù)拇_定性。本文提出了時間觸發(fā)傳輸?shù)腇PGA邏輯設(shè)計與實現(xiàn)方案,并將實現(xiàn)的協(xié)議在樣機平臺上進行了實物測試驗證,經(jīng)測試滿足設(shè)計要求。本文設(shè)計實現(xiàn)的光纖通道總線協(xié)議支持時間觸發(fā)傳輸,且僅需要對節(jié)點協(xié)議進行修改,而交換機可以使用普通FC交換機,系統(tǒng)改造和升級的代價較低,實現(xiàn)的節(jié)點可以兼容普通的事件觸發(fā)傳輸,在工程實際中具有一定的參考和實用價值。