基于SysML&SystemC的GPU任務調度單元事務級建模

張少鋒,田 澤,3,吳曉成,張 駿,3,陳 佳

(1.航空工業西安航空計算技術研究所,陜西 西安 710068;2.西安翔騰微電子科技有限公司,陜西 西安 710068;3.集成電路與微系統設計航空科技重點實驗室,陜西 西安 710068)

0 引言

在人工智能技術和各種并行計算應用蓬勃發展的今天,GPU作為高性能計算平臺扮演著極其重要的角色,隨著GPU芯片規模的日益復雜和龐大,其設計難度也日益增高。傳統的“瀑布”式芯片設計及驗證方法存在架構、軟件和RTL之間缺乏有效的協同設計驗證手段,導致算法、硬件結構、軟硬件交互和軟件實現的問題直到RTL仿真階段才集中暴露出來,再加上無法避免的RTL邏輯實現缺陷,芯片設計各環節之間的迭代周期和難度大幅增加,傳統的芯片設計及驗證方法已不能滿足架構復雜的GPU的設計開發要求。綜合運用SysML和SystemC軟硬件設計語言的基于事務級模型的芯片設計驗證方法應運而生,給架構、軟件和RTL設計提供了統一的協同設計驗證載體,縮短了芯片設計驗證的迭代環,逐漸成為主要方法[1-3]。

GPU是涉及計算機學、圖形學和微電子學等多學科交叉的高復雜度集成電路,模塊化設計是必由之路,其中任務調度單元是GPU的關鍵子模塊,是連接用戶著色任務和GPU染色內核的紐帶。本文采用SysML和SystemC構建了任務調度單元的視圖模型和事務級建模(Transaction-Level Modeling,TLM)模型,通過軟硬件協同仿真,驗證和優化了任務調度單元架構和算法設計,為軟件開發提供了虛擬原型,并為RTL設計驗證提供了先驗依據和參考模型[4-8],有效降低了GPU設計驗證迭代的復雜度,加速了GPU的設計驗證進度。

1 基于SysML&SystemC的GPU設計開發方法

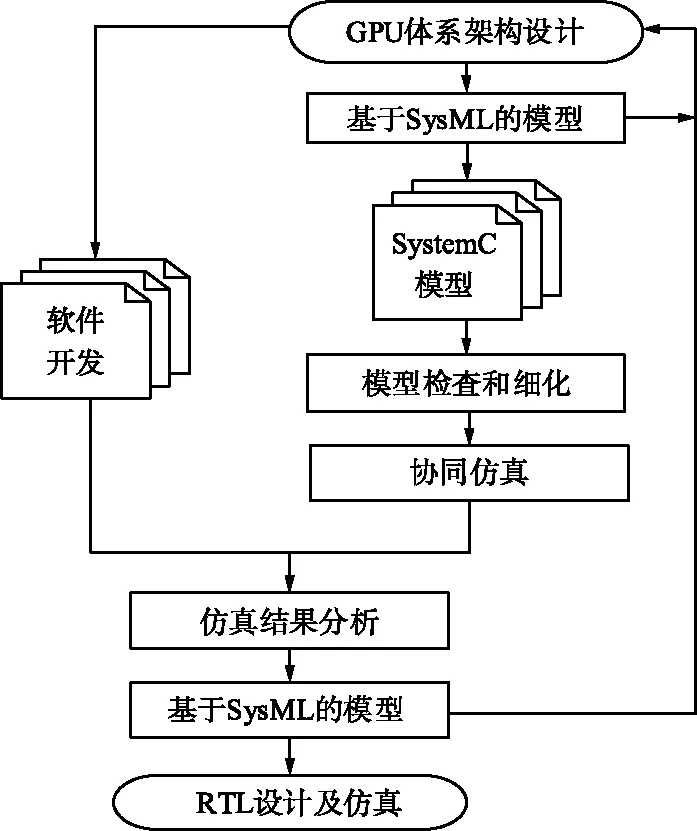

基于SysML&SystemC的復雜芯片設計開發方法是在傳統的開發流程中加入了TLM模型,TLM模型提供了架構、軟件、RTL三者交互的媒介,降低了三者之間的耦合度,有效降低了GPU設計驗證迭代的復雜度,加速了GPU的設計驗證進度。基于SysML&SystemC的復雜芯片設計開發流程如圖1所示。

圖1 基于SysML&SystemC的GPU設計開發流程Fig.1 GPU design and development process based on SysML&SystemC

在這種設計模式中,SysML用于系統架構的分析與設計,描述系統的需求、結構、功能及相應的行為,SystemC利用軟硬件協同的思想建立事務級模型。首先根據體系架構設計建立SysML視圖模型,然后將SysML視圖模型映射為SystemC模型,SystemC模型經過檢查和細化后形成TLM模型,然后聯合軟件進行軟硬件協同仿真,最后對仿真結果進行分析以達到盡可能早的驗證和優化架構以及算法的目的,并為RTL提供了參考設計。

1.1 SysML模型

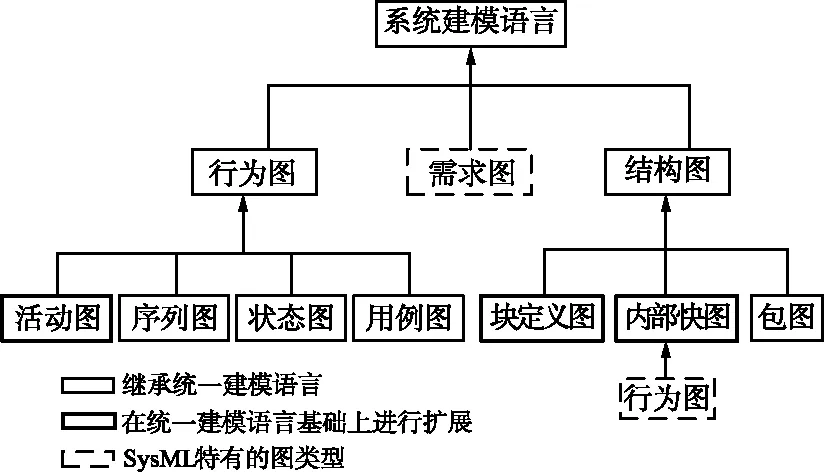

SysML是由統一建模語言(Unified Modeling Language,UML)繼承發展而來的能夠表達豐富內容的可視化系統建模語言,能夠支持各種復雜系統的詳細分析、設計、驗證和說明,可以把系統的結構、行為、需求和參數可視化,然后與其他人溝通這些信息。SysML定義了9種基本圖形如2所示,包含模塊定義圖(Block Definition Diagram,BDD)、內部模塊圖(Internal Block Diagram,IBD)、包圖、用例圖、活動圖、序列圖、狀態機圖、參數圖和需求圖,可以使用它們說明系統的所有設計信息。每種圖都針對特定的目的,并說明系統一個方面的特定信息[9-12]。

圖2 SysML視圖元素Fig.2 SysML view elements

1.2 基于SystemC的TLM模型

TLM模型是比RTL更高的抽象級別,是一種高級的數字系統模型化方法,它將模型間的通信細節與函數單元或通信架構的細節分離開來。由于TLM模型具有更高的抽象層次,它具備開發周期短和仿真速度快的特點,可以在項目早期驗證算法和架構的正確性,為軟件開發提供虛擬原型平臺,還可以為RTL開發提供參考設計。

SystemC本質上是在C++的基礎上添加了硬件擴展庫和仿真內核,利用類的繼承性來擴展C++在硬件開發驗證領域的能力,所以它具備TLM的優勢[9]。SystemC提供了必要的硬件時序、并發等概念,支持線程同步和通信細化,并提供了一個專門的擴展驗證庫,使得利用它可以建模不同抽象級別的復雜系統,既可以描述純功能模型和系統體系結構,也可以描述軟硬件的具體實現[13]。

如果迅速完成高層次系統行為的TLM描述,便可以確定最佳系統架構,進而逐步細化模型,并在模型基礎上同時開展軟件和硬件設計和驗證,從而在保證設計優化的情況下減少仿真時間以加速設計收斂。TLM2.0中,事務級模型可以細分為非定時、松散定時、近似定時和周期精確模型,每個層次的模型應用場景有所不同,非定時模型可以提供虛擬原型,更快地驗證架構和算法的正確性,松散定時模型主要用于體系結構分析、軟件開發和軟件性能評估,近似定時模型主要用于體系結構優化分析和硬件驗證,周期精確模型更適合硬件RTL驗證[14-15]。

本文采用SystemC TLM2.0進行松散時間的事務級建模,能在保證較快仿真速度的基礎上快速建立硬件的可執行事務級模型,又能最大限度地精確描述硬件行為以評估優化體系架構。

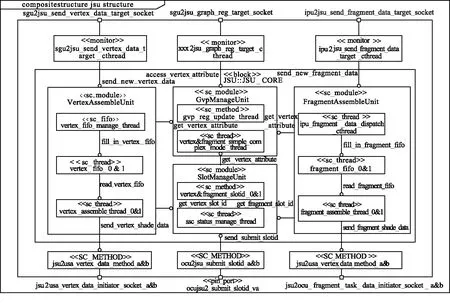

圖3 GPU任務調度單元內部模塊Fig.3 Internal block diagram of GPU task scheduling unit

2 SysML建模

SysML是UML在系統工程應用領域的延續和擴展,從視圖模型的不同描述角度SysML視圖可劃分為需求圖、參數圖、結構圖和行為圖四大類。需求圖和參數圖是SysML語言針對復雜系統而設計的特有的圖類,需求圖用于識別、描述和管理芯片設計的需求,參數圖用于說明系統的約束。SysML針對復雜系統在UML基礎上對結構圖和行為圖進行了擴展。

本文采用Sparx Systems公司的Enterprise Architect建模工具構建SysML視圖,通過梳理GPU架構和算法構建GPU任務調度單元的結構圖和行為圖。結構圖和行為圖的構建是逐步細化并且準確的過程,構建過程本身就達到了初步驗證架構和算法的目的。SysML視圖模型可以為架構、軟件和RTL提供一個相對準確無歧義的信息交互媒介。

2.1 結構圖

結構圖中描述子模塊結構的圖是IBD,通過組件、端口和連接器來用于描述系統模塊的內部結構和交互,組件包括SC_THREAD、SC_METHOD、sc_fifo和monitor,端口和連接器包括pin-port、 socket和API,socket是TLM2.0的核心內容。

GPU任務調度單元IBD如圖3所示。

圖3主要包括2個block:接口適配(JSU_Adapter)和內核(JSU_CORE)。接口適配一方面通過monitor監控和解析其他模塊發送的控制信息和數據交給本單元的處理進程,另一方面通過SC_METHOD驅動本單元的輸出信息到其他單元。與其他模塊交互的通道是pin-port和socket,socket將在TLM建模中詳細描述。任務調度單元內核包括頂點組裝單元、片段組裝單元、染色陣列管理單元和組裝控制寄存器組管理單元。每個子單元都包含了若干個用于描述行為的組件。

通過JSU_Adapter和JSU_CORE的互聯通信,完成GPU染色任務的調度工作包括:① 頂點組裝單元按照組裝控制寄存器組的控制信息將用戶下發的符合OpenGL和GLSL標準的頂點著色任務進行組裝并下發至分配的染色陣列單元;② 片段組裝單元按照組裝控制寄存器組的控制信息將圖像處理單元或幾何引擎單元下發的片段著色任務進行組裝并下發至分配的統一染色陣列單元;③ 染色內核管理負責染色陣列資源分配映射和任務管理;④ 組裝控制寄存器組管理單元用于接收和管理用戶的組裝控制信息。

2.2 行為圖

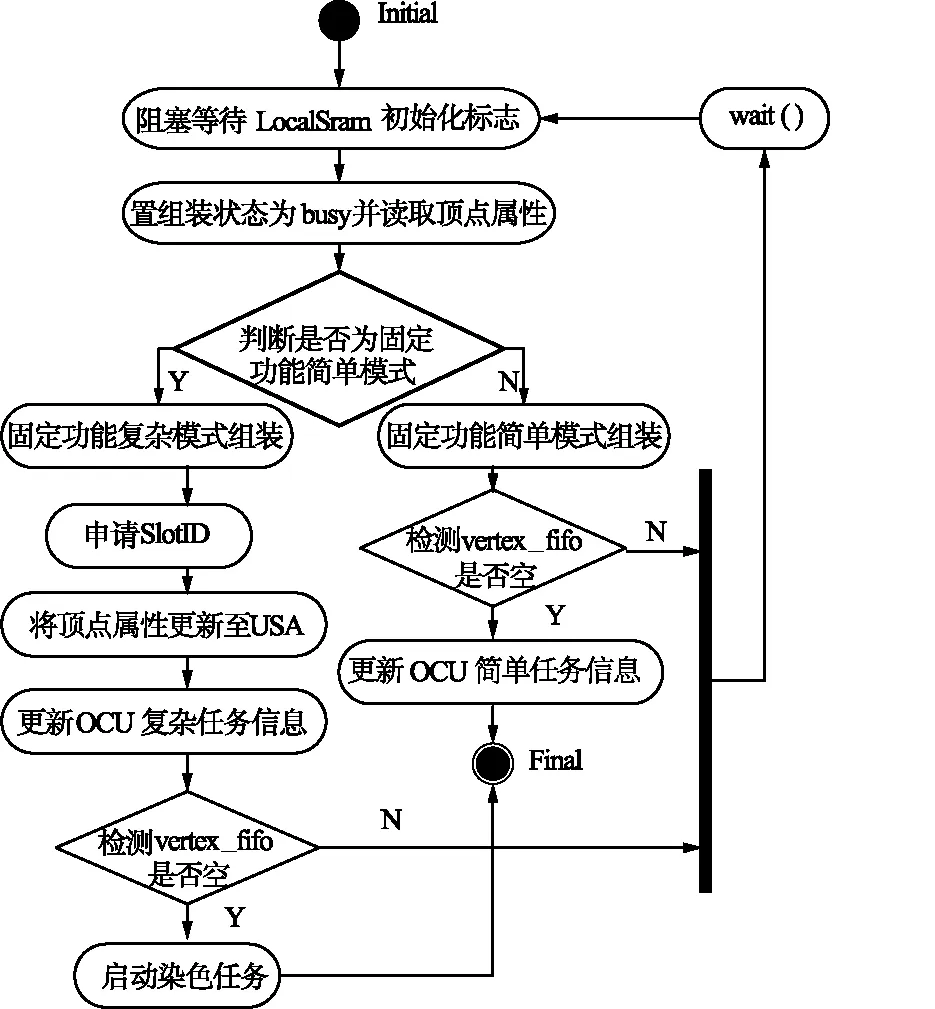

行為圖主要關注控制流程和模塊內部狀態變化,描述在事件觸發下的不同狀態間的轉換和輸入轉化為輸出的過程。在描述GPU任務調度單元時,行為圖是對內部塊圖的一種細化,描述了線程或對象的關鍵成員函數的處理流程,展現一個線程基于事件反應的動態行為,顯示了該線程如何根據當前所處的狀態對不同事件做出不同的反應。

GPU任務調度單元是GPU的調度中樞,功能比較復雜,由于篇幅有限,只描述頂點組裝單元的行為圖。根據著色任務的復雜性,組裝過程分為簡單模式和復雜模式2種。不同的工作模式下,頂點組裝單元的行為也不同,如圖4所示。工作模式由組裝控制寄存器組管理單元根據包括紋理開關、光照開關、霧開關等一系列開關計算形成的。頂點組裝單元的fifo管理進程將來自狀態參數與圖形處理管理單元(SGU)的多個頂點的屬性存入vertex_fifo,頂點屬性包括坐標屬性、顏色屬性、紋理屬性和光照屬性等;然后由頂點組裝進程組裝為一個統一染色陣列(USA)上能夠運行的vertex WARP,WARP是USA處理的最小單元;最后WARP被調度到對應的USA內核進行頂點著色處理。

圖4 頂點組裝線程行為圖Fig.4 Vertex assembling thread behavior diagram

3 基于SystemC的事務級建模及仿真

SysML視圖模型經過多次迭代和梳理驗證后,能較精準地描述芯片體系架構和算法流程,這時可以自然且直觀地將視圖模型以某種方式映射為事務級模型。本文采用SystemC&TLM2.0將SysML視圖“翻譯”為松散時間的事務級模型。結構圖可以映射為模塊定義,行為圖可以映射為線程定義。

3.1 模塊定義

與Verilog類似,模塊是SystemC設計中完成特定功能的最基本單元,主要包含用于模塊間通信的端口或信道,用于實現內部行為的方法、線程和存儲模型。任務調度單元定義了2個module,分別是G3D_JSU_ADAPTER和G3D_JSU_CORE,G3D_JSU_ADAPTER繼承于G3D_JSU_CORE,G3D_JSU_CORE繼承于sc_module。

TLM2.0中,用pin-port來實現功能簡單的信號并傳遞信息;完成同一類較復雜事務的多組信號可以封裝為socket,利用TLM2.0對socket通信的支持來完成事務通信。發起事務的模塊稱為發起者(initiator),而接收該事務并作出響應的模塊稱為目標(target),發起者和目標之間通過套接字(socket)連接。發起者和目標模塊必須遵守在TLM2.0中稱為事務處理核心接口的接口標準才能互聯互通。

TLM2.0提供了豐富的socket方法來建模功能行為,包括雙向的非阻塞接口方法、阻塞接口方法、雙向的DMI(Direct Memory Interface)接口方法、調試接口方法。這些方法用于解析模塊間傳遞的控制信息和數據。

任務調度單元的G3D_JSU_ADAPTER包含了pin-ports、soket、socket function、api、thread的聲明,實現的功能包括:① 將其他模塊輸入的信息或數據在socket function或thread 中進行解析,并調用api觸發內核的相關處理操作;② 將內核要傳輸的信息在socket function中組包為payload通過socket發送,或者在thread中驅動pin-port端口通信。

G3D_JSU_CORE包含了api、method和thread的聲明,實現的功能主要接收G3D_JSU_ADAPTER下發的信息交由method或thread進行處理,將處理結果通過純虛函數API(該API在G3D_JSU_CORE 中聲明,在G3D_JSU_ADAPTER實現)傳送給G3D_JSU_ADAPTER再發送出去。2個module具體的實現如下:

classG3D_JSU_CORE:public

sc_core::sc_module

{protected: ∥ api functions

virtual void api1_send_vertex_shade_

data_to_usa_a () = 0;

private: ∥ process functions

∥頂點組裝線程進程

void vertex_assemble_cthread_0();

∥片段組裝線程進程

void fragment_assemble_cthread_0 ();

∥頂點FIFO管理進程

void vertex_fifo_manage_cthread();};

class G3D_JSU_ADAPTER: public G3D_JSU_CORE

{public: ∥ pin-ports

sc_core::sc_in

sc_core::sc_in

∥簡單復雜模式,

sc_core::sc_out

JSU2SGU_VERTEX_SIMPLE_COMPLEX_MODE;

sc_core::sc_out

JSU2SGU_FRAGMENT_SIMPLE_COMPLEX_MODE;

public: ∥ socket

tlm::tlm_initiator_socket<>

jsu2usa_vertex_data_initiator_socket_a;

tlm::tlm_target_socket<>

sgu2jsu_send_vertex_data_target_socket;

public: ∥ constructior and destructor

G3D_JSU_CORE

( sc_core::sc_module_name _name );

virtual ~G3D_JSU_CORE();

private: ∥ socket function

void b_transport(

tlm::tlm_generic_payload &payload

,sc_core::sc_time &delay_time );∥阻塞

tlm::tlm_sync_enum

b_transport_fw(tlm::tlm_generic_payload &gp

, tlm::tlm_phase &phase, sc_core::sc_time

&delay_time );∥非阻塞-前向

tlm::tlm_sync_enum

nb_transport_bw(tlm::tlm_generic_payload

&payload,tlm::tlm_phase phase,sc_core::sc_time

&delta ); ∥非阻塞-后向

protected: ∥ api functions

void

api1_send_vertex_shade_data_to_usa_a ();

void api0_send_new_vertex_data();

private: ∥ process function

∥用于監控和解析SGU發送的頂點數據

voidsgu2jsu_send_vertex_data_target_cthread();};

3.2 進程定義

SystemC進程是任務調度單元處理事務的載體,包括方法進程SC_METHOD、線程進程SC_THREAD和鐘控線程進程SC_CTHREAD,它們被調用來仿真目標系統的行為,實現模塊的算法和控制細節。最常用的是線程進程,特點是它能夠被掛起和重新激活:線程進程使用wait()掛起,當敏感表中有事件發生,線程進程被重新激活運行到遇到新的wait()語句再重新掛起。

定義了大量的進程來協同完成GPU的任務調度,下面以頂點組裝線程進程為例來說明進程的實現,包括進程的注冊和定義:

SC_THREAD(Vertex_Assemble_Cthread_0);∥啟動進程

sensitive_pos << clock;∥注冊敏感事件為時鐘

void G3D_JSU_VAU:: Vertex_Assemble_Cthread_0 ()∥進程的定義

{ while(true)

{ wait();

jsuVertexBusy.write(1);∥

∥ read sgu2jsu_fifo

do{ wait();

} while(sguVertexFifoEmpty == ds_basic::EMPTY);

sgu2jsu_fifo->read()

∥ update GVP Reg

Update_Gvp_Vertex_Attribute(graphDrawData);

∥ check workMode is simple or complex

if(vdauGetServicePort->Get_Vertex_Simple_Complex_Mode() == ds_basic::SIMPLE) ∥ simple mode{Update_Ocu_Simple_Vertex_Task(ds_func_jsu::VERTEX_TYPE);}

else ∥ complex mode

{ Get_Vertex_Slot_Id(gotSlotId);

Update_Usa_Vertex_Attrib_From_Gvp(ds_func_jsu::VERTEX_TYPE,gotSlotId,updateMask,graphDrawData.type);}

jsuVertexBusy.write(0);

return;}}

3.3 仿真驗證

任務調度單元的TLM模型開發完成后與其他模塊的TLM模型進行互聯構成整個GPU的TLM模型,TLM模型之間依靠時鐘和動態事件同步,通過pin-port、socket進行事務通信。接下來的工作就是基于SystemC simulation kernel的仿真驗證,該kernel的主要任務是控制仿真、響應event、對不同線程進行切換等。本文采用的SystemC庫版本為2.3.3,參考平臺采用Mesa,Mesa是以開源軟件形式實現的OpenGL標準應用程序接口模型,不依賴任何硬件。

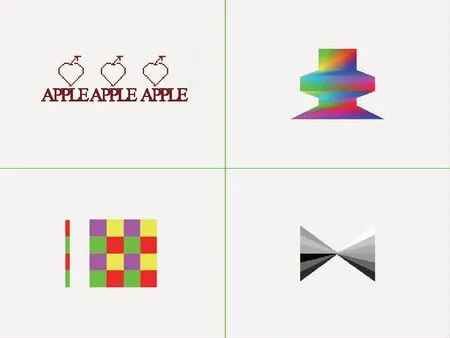

采用OpenGL2.0,構造如下的測試場景:利用glViewPort將屏幕劃分為4個子窗口,第1個窗口中使用一維紋理和二維紋理貼圖功能,第2個窗口中使用了壓縮紋理功能,第3個窗口中使用了位圖(glBitmap)功能,第4個窗口中繪制了平滑著色的多邊形帶。驗證場景涵蓋了頂點著色和片段著色的典型功能,能觸發任務調度單元的關鍵控制通路。圖5顯示了TLM模型輸出了跟MESA相同的正確結果圖,并且該驗證項在TLM仿真平臺僅耗時10 min,相同的驗證項在RTL虛擬仿真平臺將耗時數小時,由此可見TLM模型功能正確并且仿真速度得到了巨大提升。

圖5 TLM模型結果和MESA參考Fig.5 TLM model result figure and MESA reference figure

4 結束語

采用基于TLM模型的GPU設計驗證方法,能盡早驗證優化算法、架構和電路功能,并為RTL設計提供了參考模型,加速了GPU的軟硬件協同設計。TLM模型采用SysML和SystemC聯合開發,首先構建任務調度單元的SysML視圖模型,然后將其映射為事務級模型,最后進行仿真驗證。本文主要研究松散定時的功能性建模,后續將建立近似定時TLM模型和時鐘周期精確TLM模型,以此進行體系結構的性能分析向模塊設計提供性能指標依據,以及硬件RTL和TLM模型的混合仿真驗證。