基于FPGA的有限狀態機計時器設計

楊秀蘭 楊玉

摘要:當前FPGA應用很廣,可以用來設計很多自身需求的程序以達到一定的便利。本文使用FPGA設計一個計時器,該計時器用到有限狀態機的機制來實現控制,計時器可實現時分秒的精確計數,并可顯示出去再液晶屏或者顯示屏。最后進行功能仿真以校驗時序和控制的準確性。

關鍵詞: FPGA;計時器;控制;狀態機

1.前言

當前FPGA的應用非常廣,用它進行編程的人也越來越多。應用FPGA進行自身所需求的產品的設計是非常合適的,用有限狀態機的機制去控制計時器,讓計時器可以重置、報時等。有限狀態機常常被用在自動售貨機、排號機、ATM、銀行業務自助機等上面。該計時器可顯示時分秒,最大計時為59時59分59秒,可以清零和每隔10分鐘進行報時。

2.設計與實現

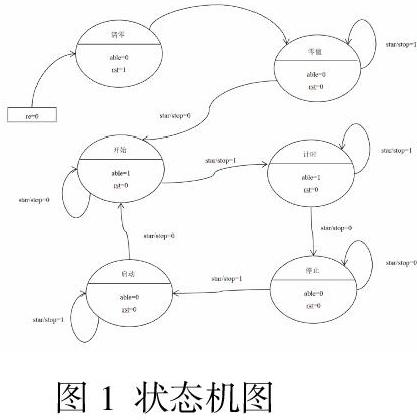

該計時器由三個部分組成,這三個部分分別是控制部分、計時部分、顯示和發聲部分。控制部分主要由一個有限狀態機完成控制,有清零和啟動/暫停等按鍵。該有限狀態機設置六個狀態,分別是清零狀態、零值狀態、開始狀態、計時狀態、停止狀態、啟動狀態。該狀態機兩個輸入分別是清零按鍵(re)、啟停按鍵(star/stop),兩個輸出分別是計時許可(able)、計時清零(rst),其狀態機圖如下圖1所示:

其中,當清零按鍵re按下時,狀態機進入清除狀態,其計時許可控制輸出信號able為低電平,計時清零輸出信號rst為高電平,則進行清零,計時器就會清除當前所有計時,并從清零狀態進入到零值的狀態;而在零值狀態下,當按下啟停按鍵(star/stop)時,就會進入開始狀態,則計時器開始計時;而在開始狀態下時,當star/stop按鍵由0變成1時,則會進入自動計時狀態,計時許可控制信號able為高電平,允許計數器計數;在計時狀態下,當按下啟停按鍵時即star/stop按鍵由1變成0時,則停止計時,會進入停止狀態;在停止狀態下,當star/stop按鍵由0變成1時,就會進入啟動狀態;在啟動狀態下,當按下啟停按鍵時即star/stop按鍵由1變成0時,則又進入開始狀態;當star/stop按鍵由0變成1時,進入計時狀態,這時計數器會在原來已經計有的數字的基礎上繼續計時。如果想重新開始計時,則按下清零按鈕(re)。

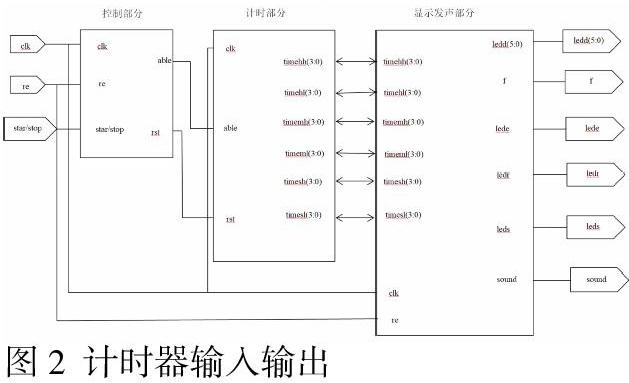

整個計時器的三個部分的輸入輸出模塊圖如圖2所示,

其中,clk為FPGA開發板的時鐘。時間部分為:timehh(小時高位)、timehl(小時低位)、timemh(分鐘高位)、timeml(分鐘低位)、timesh(秒高位)、timesl(秒低位)。顯示發聲部分為:ledd為輸出的數據即時間,leds為寄存器選擇控制輸出信號,當其為低電平時,表示數據總線傳輸的是命令控制信號,當其為高電平時,表示數據總線傳輸的是數據信號;ledr為讀/寫控制輸出信號,當其為低電平時,表示向顯示屏控制芯片寫數據;lede為讀/寫操作允許控制脈沖輸出信號,高電平有效;sound為發聲信號,用于統計每十分鐘進行一次報時;f為使能控制信號,低電平有效,高電平時不允許占用數據總線。

3.總結

該設計制作了一個有限狀態機控制的計時器,其特點是可長時間計時并報時,是一個很實用的計時器。本文以設計一個實用的計時器去了解和探索FPGA的開發,以便以后能做出更多更好更有用的設計。

參考文獻

1.曾一凡, 吳思琪. 基于FPGA和有限狀態機的守時系統設計[J]. 計算機測量與控制, 2014, 022(005):1565-1567.

2.孫兆偉, 劉源, 徐國棟,等. 基于FPGA內置RAM的抗輻射有限狀態機設計[J]. 航空學報, 2010(05):118-124.

作者簡介:楊玉(1977-),女,廣西玉林人,學士,助教,研究方向:流動力學,為本文通訊作者。

資助基金:二本院校離散數學MOOC改革與應用(2020XJJGZC10)