具有GPS時間同步功能的高精度數字鐘的設計

呂念芝,肖志雄

(福州理工學院 工學院,福建 福州 350001)

GPS(global position system)是美國研制的導航、授時和定位系統。GPS時鐘已成為世界上傳授范圍最廣、精度最高的時間發布系統之一,GPS接收機接收到的GPS時鐘與國際標準時間(UCT-universal co-ordinated time)保持高度同步[1-2]。

時間同步技術對于電力系統的正常運行和故障診斷都起著至關重要的作用。特別是在故障測距和繼電保護等領域,時間和同步的精度將直接影響最后的分析結果[3]。

當前的數字鐘普遍采用晶振時鐘計數顯示北京時間,存在較大的累計誤差。時鐘誤差過大很難在對時鐘精度高和穩定性要求高的電力系統中得到應用。為了解決普通時鐘存在的低精度問題,采用FPGA技術,設計了具有高精度的數字鐘,該方法可以消除晶振的累計誤差,得到和GPS同步的時鐘信息和高精度的秒脈沖。同時,該方法在一個芯片內完成,具有簡單實用、體積小、功耗低的優點,具有較強的抗干擾性。該設計方案在以Altera的EP4CE6F17C8為核心器件的硬件平臺上得到驗證。

1 基于FPGA的整體實現方案

實現高精度的數字鐘,需要提取出來GPS接收機發送出來的IRIG-B(DC)碼中包含的時間信息,主要包含小時、分鐘和秒信息,同時提取出高精度的秒脈沖信號。提取出來的時間信息再通過顯示模塊輸出到對應的數碼管。顯示控制模塊包含三部分:控制模塊、掃描模塊和譯碼模塊。硬件中數碼管采用共陽接法,動態顯示數據。整體硬件功能示意圖如圖1所示。

圖1 整體硬件功能示意圖Fig.1 Overall hardware function diagram

2 FPGA的內部電路設計

在設計FPGA內部電路時,采用QuartusII12.0軟件進行開發,使用超高速硬件描述語言(Verilog HDL)和原理圖相結合的模塊化設計。這種模塊話設計不僅可讀性強,也易于修改,提高了程序的設計效率[4]。

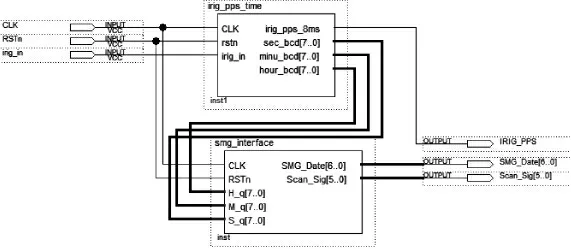

現場可編程邏輯器件FPGA芯片[5]內部的頂層電路如圖2所示。頂層電路由irig_pps_time解碼電路和smg_interface顯示控制模塊電路組成。圖2中解碼模塊電路對輸入的B(DC)碼進行解碼,識別和提取出時間信息和解調秒脈沖信號。解調出的秒脈沖信號直接作為輸出信號。時間信號以BCD碼的形式輸出給控制顯示模塊使之當前時間能正確的顯示在7段數碼管上[6]。

圖2 FPGA內部的頂層電路Fig.2 Top-level circuit in FPGA

2.1 解碼模塊

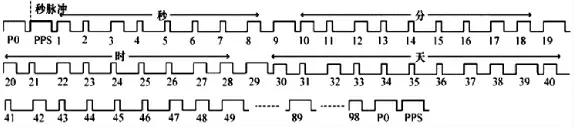

IRIG_B碼(DC)共有3種碼元,每一個碼元占用10 ms的時間,邏輯“0”和邏輯“1”所對應碼元的高電平分別為2和5 ms,P碼元是位置碼元,對應的高電平為8 ms的時間。B碼為1 s傳送1幀,每1幀所包含的時間信息如果3所示。在圖3中,連續2個P碼元為1幀的開始[7-8]。

圖3 IRIG_B(DC)碼每幀的信息Fig.3 Information per frame of IRIG_B(DC)

2.1.1 PPS秒脈沖提取

IRIG-B碼的時幀周期是1 s,包含100個碼元,每個碼元周期為10 ms,因此需要生成1個脈沖clk_1k。此外還需要1個采集數據的脈沖(data_bit_clk),此脈沖周期也是1 ms。

data_bit_clk這個信號主要用在解碼程序里面,一個時鐘采集1個數據位(1 ms里面只采集1個數據)。

幀頭的意義:irig_code是一個數據寄存器,每1 ms的時間里面存放1個采集到的數據,這樣irig_code寄存器就會每個1個ms數據就會改變1次,當里面的數據是20’hFF3FC,表示幀頭已經檢測到了。

當第1次檢測到幀頭并配合解碼脈沖(irig_code=20’hFF3FC&data_bit_clk),產生1個低989 ms高11 ms的脈沖(mask)。mask與irig_data_in與運算,產生的信號就是秒脈沖irig_pps。

2.1.2 時間解碼

B碼秒脈沖輸入信號:irig_data_in,解碼時間時鐘:data_bit_clk。因為B碼編碼中0、1,P碼即:每個碼元寬度為10 ms,因此用irig_bit_cnt記錄位的次數,周期是10。10個irig_bit_cnt構成1個碼元,irig_slot_cnt記錄碼元個數。又因為每10個碼元有1個位置識別標志,構成1個時隙,因此用irig_frame_cnt記錄時隙的次數,周期是10,10個irig_frame_cnt構成1幀。

用sec_spl寄存器保存暫時的秒信息,這個寄存器是一個8位寄存器。高四位保存秒的個位信息,低四位保存秒的個位信息(都是BCD碼表示)。秒信息是在第2個10 ms脈沖之后的第3、4、5、6和8、9、10個10 ms(碼元)。

用minu_spl寄存器暫時保存分信息,這個寄存器是8位的。分的十位信息用高四位保存,分的個位信息用低四位保存。分的信息是B碼的第11個碼元開始,這個時候irig_frame_cnt=4'h1,即第2個100 ms時隙,在這個時隙里面,分的個位和十位信息包含在第2、3、4、5和7、8、9個10 ms(碼元)。

用hour_spl這個寄存器暫時保存時信息,這也是一個8位的寄存器。時信息的個位信息是其低四位,高四位保存時的十位信息。時的低信息是在22、23、24、25和27、28個10 ms(碼元)。

2.2 控制顯示模塊

控制顯示模塊包含3個子模塊:數碼管數據控制模塊、數碼管掃描模塊、數碼管顯示譯碼模塊,具體的FPGA電路如圖4所示。

開發板上安裝了6個共陽數碼管,可以顯示6個數字(從左往右依次顯示小時、分鐘、秒)。6個數碼管的7段驅動信號是SMG_Date[6..0],分別對應數碼管的g..a段。驅動信號是“低電平有效”。6個數碼管的列掃描信號是Scan_Sig[5..0]。Scan_Sig[5]選擇的是小時的十位,Scan_Sig[4]選擇的是小時的個位,Scan_Sig[3]選擇的是分鐘的十位,Scan_Sig[2]選擇的是分鐘的個位,Scan_Sig[1]選擇的是秒的十位,Scan_Sig[0]是秒的個位。分別對應的是來選擇哪個數碼管。

圖4 FPGA控制顯示模塊Fig 4 .Control and display module of FPGA

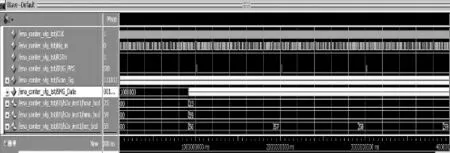

3 設計仿真

仿真測試平臺是與quartusII 12.0[9]軟件匹配的Modelsim,為加速仿真,在仿真過程中系統晶振頻率設置為1 MHz(實際硬件平臺頻率為50 MHz)。irig_in設定為365 d,23 h,59 min,56、57、58、59 s。仿真長度為4 s,整體仿真結果如圖5和圖6。在圖5中可以看到IRIG_PPS秒脈沖輸出,同時解出對應時間分別為23:59:56、23:59:57、23:59:58和23:59:59。把圖形放大可以看到SMG_Date[6..0]和Scan_Sig[5..0]對應的數值。圖6是放大后的SMG_Date[6..0]和Scan_Sig[5..0]具體數值,此時解碼時間為23:59:57。通過SMG_Date[6..0]和Scan_Sig[5..0]的數值此時數碼管顯示的正好是23:59:57。例如秒數值57,1 ms掃描信號Scan_Sig[1]=0(選擇秒的十位數碼管),SMG_Date[6..0]=0010010(數碼管的驅動信號),1 ms掃描信號Scan_Sig[0]=0(選擇秒的個位數碼管),SMG_Date[6..0]=1111000(數碼管的驅動信號)。仿真表明:解碼電路設計正確且達到解碼精度要求。

圖5 FPGA整體仿真結果(1)Fig.5 The overall simulation results of FPGA(1)

圖6 FPGA整體仿真結果(2)Fig.6 The overall simulation results of FPGA(2)

4 結論

通過IRIG_B(DC)碼的解碼和數據控制顯示兩方面詳細介紹了基于FPGA技術的高精度數字鐘的設計方案。該方案因為采用的是數碼管顯示,所以顯示內容有限。后期可以通過液晶顯示模塊顯示IRIG_B碼中包含的跟多信息。比如:年、天數、是否閏年等信息。

仿真平臺采用1 MHz時鐘信號誤差稍微高些,實際采用50 MHz的時鐘信號,設計方案的總體延時小于300 ns。同時,該方案還輸出高精度的秒脈沖信號,可以為其他設備提供需求。

隨著數字同步網的建設,用戶設備對標準時間信號的性能要求越來越高,本方案可以通過采用更高頻率的主時鐘信號和工作頻率更高的FPGA芯片來滿足用戶設備不斷提高的要求。