基于AD9361的雷達(dá)干擾信號模擬器設(shè)計(jì)

羅勇江,楊騰飛

(西安電子科技大學(xué) 電子工程學(xué)院,陜西 西安 710071)

在現(xiàn)代戰(zhàn)爭中,電子對抗已經(jīng)成為一種重要的作戰(zhàn)方式,雷達(dá)對抗又是電子對抗的主要組成部分之一,在現(xiàn)代電子對抗中有著不可替代的地位。雷達(dá)對抗是偵察、壓制敵方電磁頻譜的使用并增強(qiáng)我方電磁頻譜使用有效性的作戰(zhàn)行為,主要包括雷達(dá)偵察、雷達(dá)干擾、雷達(dá)防護(hù)等[1]。其中,雷達(dá)干擾以破壞或擾亂敵方雷達(dá)檢測目標(biāo)為目的,包括無源干擾和有源干擾。有源干擾是干擾機(jī)根據(jù)雷達(dá)的參數(shù)和具體目的產(chǎn)生特定類型干擾,具有很強(qiáng)的針對性和靈活性,是一種非常有效的干擾方式,也是現(xiàn)代雷達(dá)受到的主要干擾方式。有源干擾按照干擾信號的作用原理分為欺騙式干擾和遮蓋式干擾。欺騙性干擾是根據(jù)真實(shí)目標(biāo)的特性,加上一定的調(diào)制方式模擬形成假目標(biāo),將假目標(biāo)作用于雷達(dá)的工作過程中,使得敵方雷達(dá)對真、假目標(biāo)難以區(qū)分,造成敵方雷達(dá)獲取我方目標(biāo)參數(shù)信息的難度增大,從而達(dá)到迷惑或擾亂敵方雷達(dá)對我方真實(shí)目標(biāo)進(jìn)行跟蹤或檢測的目的[2]。根據(jù)欺騙式干擾所利用的距離、速度和假目標(biāo)數(shù)目的不同,可以將欺騙式干擾分為距離拖引干擾、速度拖引干擾、距離速度同步拖引干擾、假目標(biāo)密集復(fù)制干擾和音頻掃頻干擾五類。遮蓋性干擾又稱壓制式干擾,主要實(shí)現(xiàn)方式是通過干擾機(jī)發(fā)射干擾信號來遮蓋或淹沒目標(biāo)回波,阻止雷達(dá)正常檢測和跟蹤目標(biāo)[3]。遮蓋性干擾主要通過發(fā)射大功率噪聲實(shí)現(xiàn),強(qiáng)功率的噪聲干擾信號進(jìn)入雷達(dá)接收機(jī),使目標(biāo)回波信號的信噪比明顯下降,從而使雷達(dá)對目標(biāo)難以進(jìn)行檢測和跟蹤。典型的遮蓋性干擾有射頻噪聲干擾、噪聲調(diào)幅干擾、噪聲調(diào)頻干擾、噪聲調(diào)相干擾、噪聲脈沖干擾等。本文利用Xilinx公司的Spartan-6系列SP605評估板和AD9361評估板AD- FMCOMMS3-EBZ進(jìn)行聯(lián)合設(shè)計(jì),實(shí)現(xiàn)低成本的雷達(dá)干擾信號模擬器。

1 方案設(shè)計(jì)

本文選擇目前較成熟的零中頻軟件無線電方案,使用AD9361和FPGA設(shè)計(jì)雷達(dá)干擾信號模擬器。根據(jù)功能需求,本模擬器的核心包含兩大模塊,即射頻信號收發(fā)模塊和基帶數(shù)據(jù)處理模塊。射頻信號收發(fā)模塊由AD9361及其外圍電路構(gòu)成,完成基帶數(shù)字信號到射頻模擬信號的數(shù)模轉(zhuǎn)換、變頻、濾波、增益控制以及最終的發(fā)射工作。基帶數(shù)據(jù)處理模塊的核心是FPGA,用來實(shí)現(xiàn)基帶數(shù)字干擾信號的產(chǎn)生以及對AD9361芯片的控制。

1.1 AD9361介紹

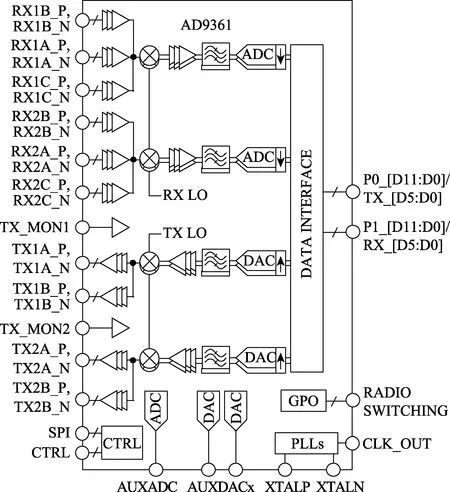

AD9361是ADI公司推出的一款高性能、高集成度的零中頻結(jié)構(gòu)的射頻收發(fā)芯片,工作頻段為70 MHz~6 GHz,支持通道帶寬為 200 kHz~56 MHz。該器件內(nèi)部集成了大量模塊,包括射頻放大器、發(fā)射和接收通道的頻率合成器、混頻器、模擬濾波器、數(shù)據(jù)轉(zhuǎn)換器等,可以完成信號在射頻前端與基帶數(shù)據(jù)流之間的轉(zhuǎn)換工作[4]。并行數(shù)據(jù)端口 P0和 P1作為AD9361與各種基帶處理器(BBP)之間的數(shù)據(jù)傳輸接口。圖1為AD9361的功能框圖。

圖1 AD9361功能框圖

AD9361的信號接收和發(fā)送鏈路分別有兩個相同的、獨(dú)立控制的通道。每個發(fā)送通道包含兩個射頻輸出端口,接收通道則有三個射頻輸入端口。在信號接收通道中,射頻信號從輸入端口進(jìn)入芯片,經(jīng)過正交混頻器被分成 I、Q兩路基帶模擬信號,每一條接收通路上集成的模數(shù)轉(zhuǎn)換器能對 I、Q兩路信號同時進(jìn)行采樣,采樣后的數(shù)字信號通過內(nèi)部可配置的抽取濾波器和 128階有限脈沖響應(yīng)(FIR)濾波器處理后生成 12位基帶數(shù)字信號,這些數(shù)字信號通過數(shù)據(jù)接口P0發(fā)送給BBP[4-6]。發(fā)送通道與接收通道類似。AD9361通過P1接口從BBP接收基帶數(shù)據(jù),然后數(shù)據(jù)通過一個不帶插值選項(xiàng)的完全可編程128抽頭的FIR濾波器和一系列插值濾波器,進(jìn)行濾波和數(shù)據(jù)速率插值處理。隨后由數(shù)模轉(zhuǎn)換器將基帶數(shù)字信號轉(zhuǎn)換為基帶模擬信號。I/Q兩路模擬信號經(jīng)過濾波后在混頻器中被組合起來形成已調(diào)制信號。已調(diào)制信號再經(jīng)過處理后輸出到天線發(fā)射。AD9361的收發(fā)通道可以同時工作,支持時分雙工(TDD)和頻分雙工(FDD)兩種工作模式。

1.2 系統(tǒng)框圖及硬件平臺

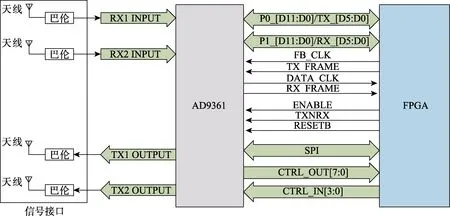

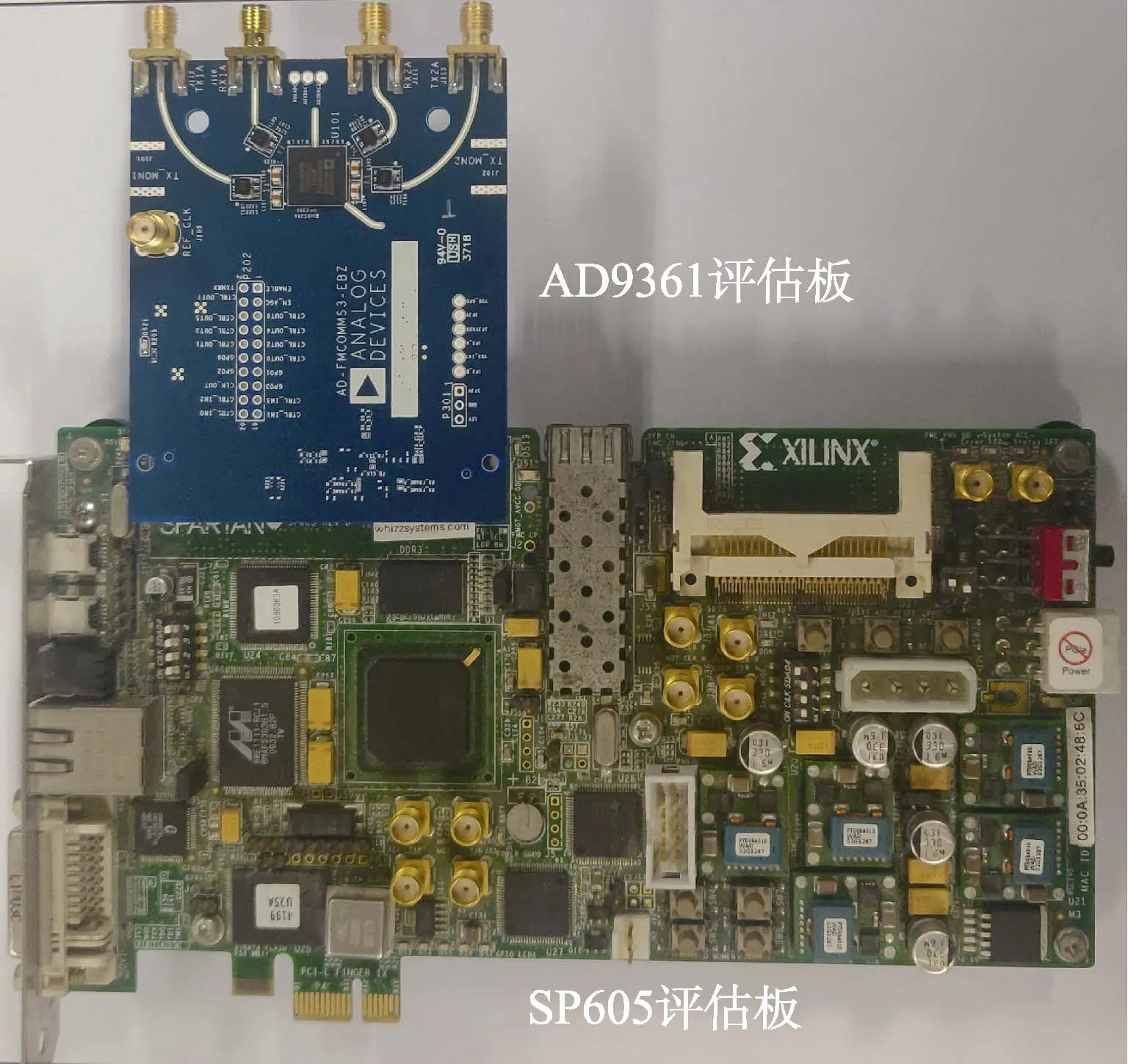

雷達(dá)干擾信號模擬器由AD9361和FPGA相互配合實(shí)現(xiàn),原理如圖2所示。信號接口模塊主要由天線

圖2 基于AD9361的雷達(dá)干擾信號模擬器原理圖

和巴倫組成,用來實(shí)現(xiàn)射頻信號的接收與發(fā)送、單端信號與差分信號的轉(zhuǎn)換。射頻模擬信號與基帶數(shù)字信號之間的轉(zhuǎn)換由 AD9361完成。AD9361的數(shù)據(jù)輸入輸出引腳和控制引腳通過FPGA夾層卡(FMC)接口與FPGA的可配置IO引腳相連,實(shí)現(xiàn)兩者之間的數(shù)據(jù)傳輸以及FPGA對AD9361的控制。硬件平臺實(shí)物連接如圖3所示。

圖3 硬件平臺實(shí)物連接圖

1.3 系統(tǒng)中的主要接口

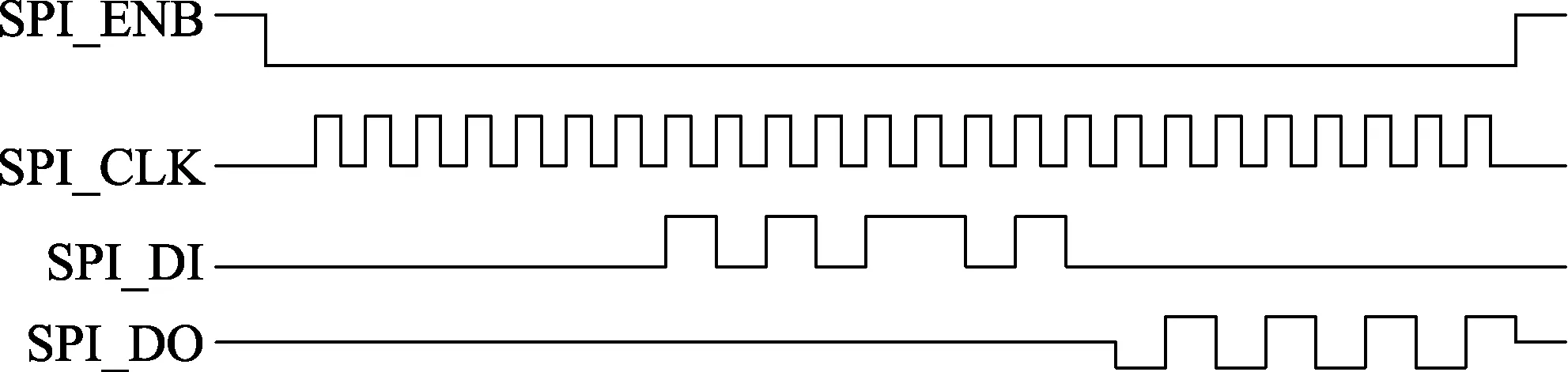

1.3.1 串行外設(shè)接口

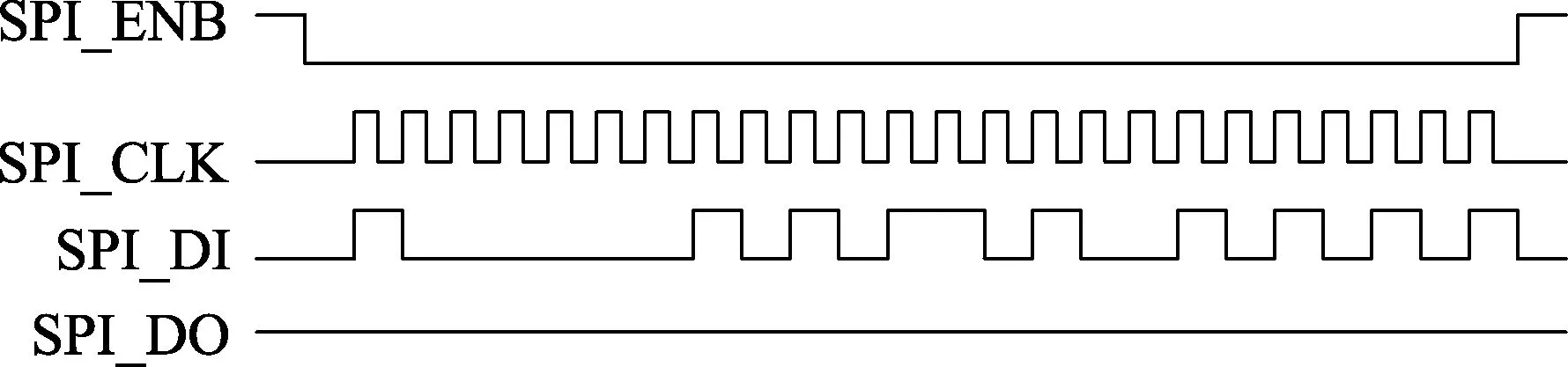

BBP對AD9361芯片的控制通常通過串行外設(shè)接口(SPI)實(shí)現(xiàn)。AD9361內(nèi)部有大量的8位寄存器,BBP可以通過SPI總線對這些寄存器進(jìn)行讀或者寫操作,來判斷或者設(shè)置AD9361當(dāng)前工作狀態(tài)。AD9361的SPI端口可以配置成3線或者4線標(biāo)準(zhǔn)SPI接口[7]。

SPI的寫命令遵循24位格式:前6位設(shè)置總線方向和需要傳輸?shù)淖止?jié)數(shù),接下來的10位是需要寫入數(shù)據(jù)的寄存器的地址,最后8位是將被傳輸至指定寄存器地址的數(shù)據(jù)。讀命令遵循相似的格式,區(qū)別在于最后8位數(shù)據(jù)從AD9361中讀取,如果是4線模式則在SPI_DO引腳傳輸這8位數(shù)據(jù),如果是3線模式則在SPI_DI引腳傳輸這8位數(shù)據(jù)。

圖4和5分別詳細(xì)展示了單寄存器寫操作和讀操作的4線SPI總線波形。在圖4中,0x55被寫入寄存器0x15A,在圖5中,讀取寄存器0x15A,并且AD9361返回0x55。如果使用3線SPI總線執(zhí)行相同操作,則圖4中沒有SPI_DO線,圖5中的SPI_DI和SPI_DO線上數(shù)據(jù)合并到SPI_DI線上。

圖4 SPI寫數(shù)據(jù)時序

圖5 SPI讀數(shù)據(jù)時序

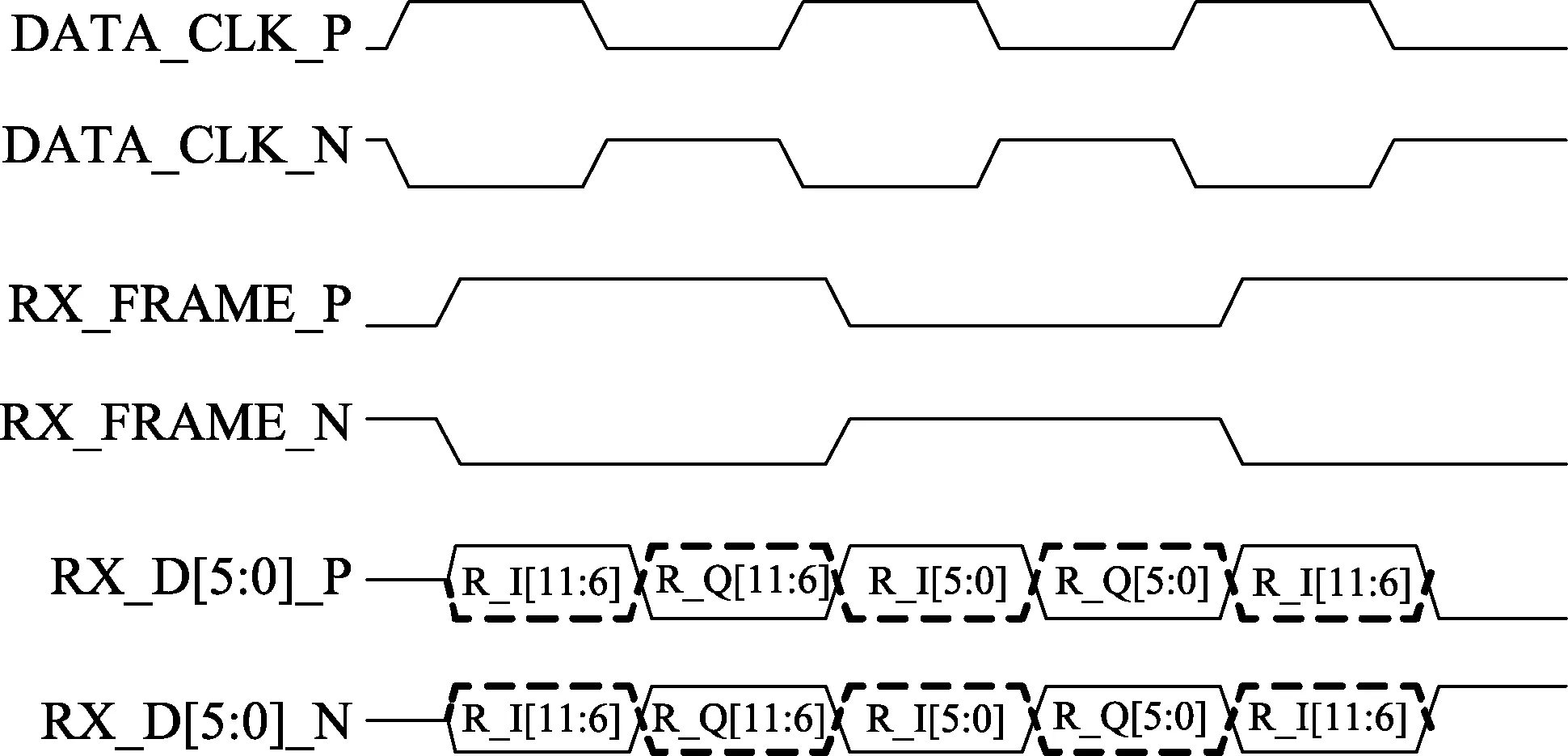

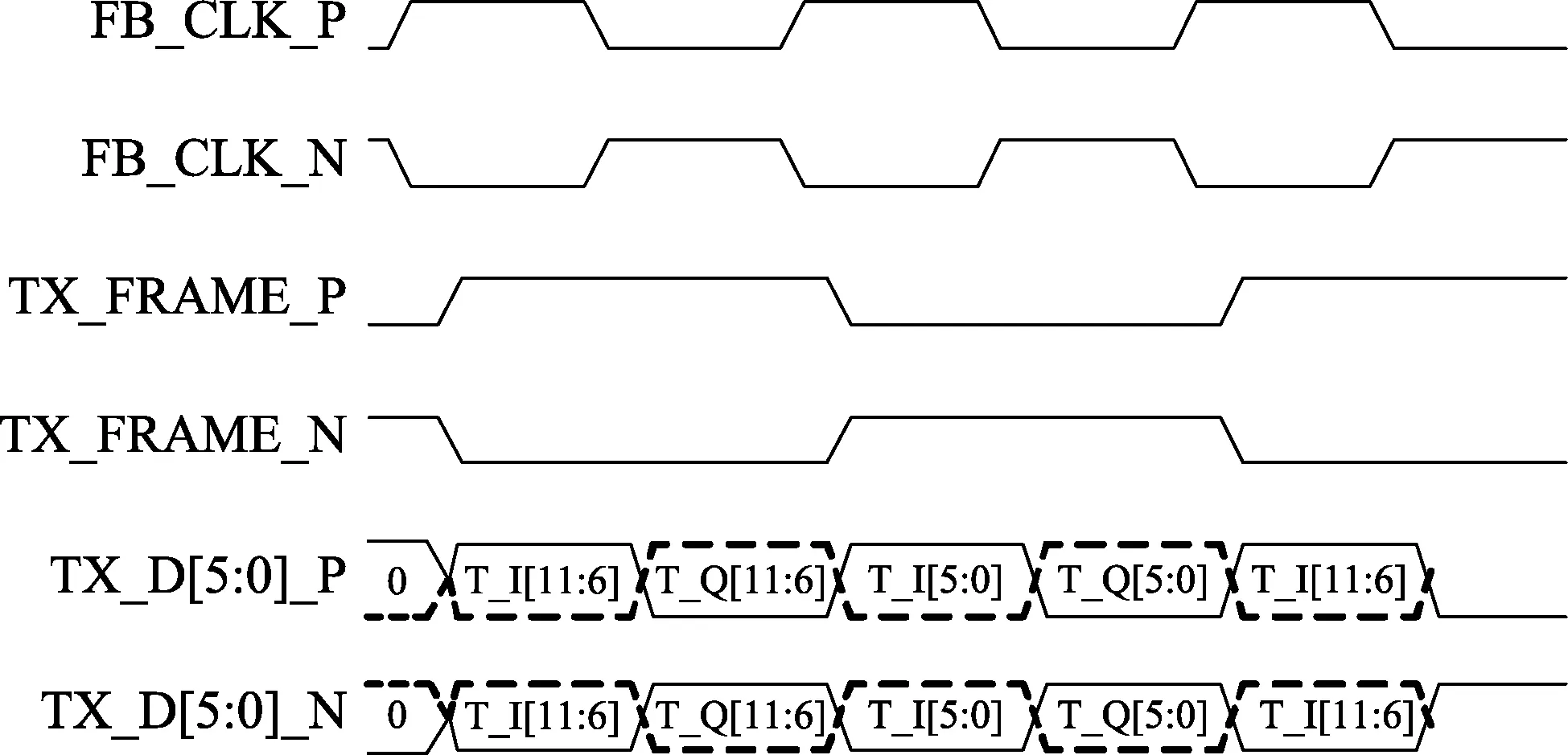

1.3.2 并行數(shù)據(jù)端口

并行數(shù)據(jù)接口用于在AD9361和BBP之間傳輸數(shù)據(jù),該接口的工作模式分為兩種:標(biāo)準(zhǔn)CMOS兼容模式和低壓差分信號(LVDS)兼容模式[8]。相比CMOS,LVDS具有低電壓、低功耗、抗干擾能力強(qiáng)和有利于高速傳輸?shù)忍攸c(diǎn),在需要更穩(wěn)定性能和更高數(shù)據(jù)速率的寬帶高速系統(tǒng)設(shè)計(jì)中,常常采用LVDS兼容模式。當(dāng)AD9361使用雙總線全雙工LVDS兼容模式時,主要的數(shù)據(jù)傳輸端口為 Tx_D[5:0]和 Rx_D[5:0]。Tx_D[5:0]和Rx_D [5:0]均是由六個差分對組成的LVDS數(shù)據(jù)總線,數(shù)據(jù)以成對的數(shù)據(jù)字在總線上傳輸。要發(fā)射的數(shù)據(jù)在 Tx_D[5:0]數(shù)據(jù)總線上從 BBP傳輸?shù)紸D9361;接收到的數(shù)據(jù)在 Rx_D[5:0]數(shù)據(jù)總線上從AD9361傳輸?shù)紹BP。這兩組總線可以同時工作,從而保證BBP和AD9361之間的數(shù)據(jù)發(fā)送和接收為全雙工。

兩組總線上的數(shù)據(jù)傳輸格式會根據(jù)接收通道數(shù)和發(fā)送通道數(shù)的不同而改變。對于具有1個接收通道和1個發(fā)送通道(1R1T)的系統(tǒng),I和Q兩路的數(shù)據(jù)以4路交錯方式傳送:IMSB, QMSB, ILSB, QLSB,…。圖6和7中的時序圖說明了 1R1T系統(tǒng)在 DDR、FDD、LVDS模式下總線信號之間的關(guān)系。

圖6 接收數(shù)據(jù)路徑時序圖

圖7 發(fā)送數(shù)據(jù)路徑時序圖

2 雷達(dá)干擾信號的FPGA實(shí)現(xiàn)

對雷達(dá)的干擾方式有多種,本文實(shí)現(xiàn)較為常用的干擾信號。干擾信號發(fā)射的主要流程為:對于壓制干擾,先使用FPGA產(chǎn)生基帶干擾數(shù)字信號,然后將該數(shù)字信號發(fā)送給 AD9361,再由 AD9361完成基帶數(shù)字信號到射頻模擬信號的轉(zhuǎn)換,并將其通過天線發(fā)射出去;對于欺騙干擾,先通過天線接收雷達(dá)信號,在FPGA中對收到的雷達(dá)信號進(jìn)行處理,再由 AD9361及外部天線完成發(fā)射。

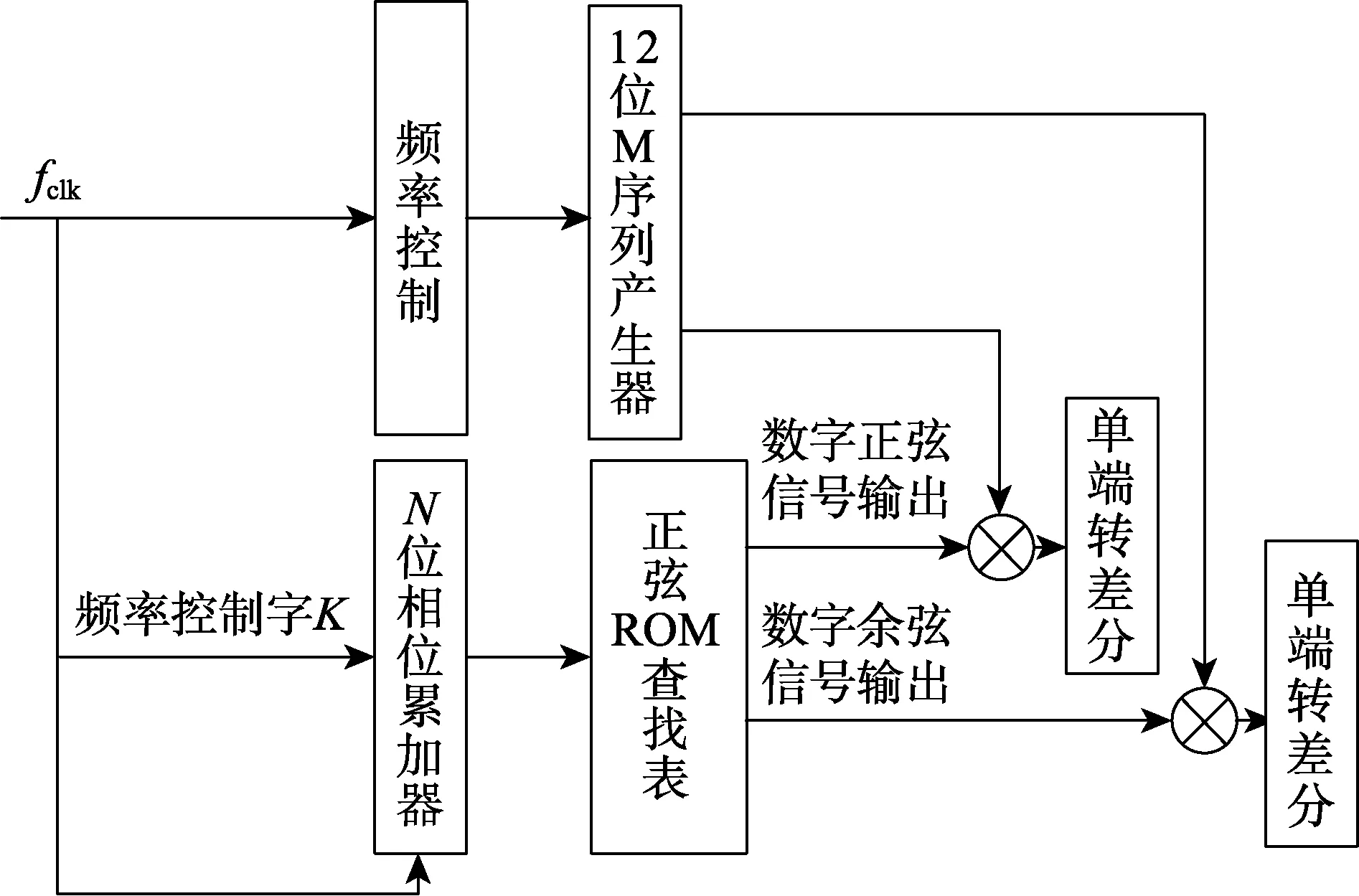

2.1 噪聲調(diào)幅干擾信號產(chǎn)生原理

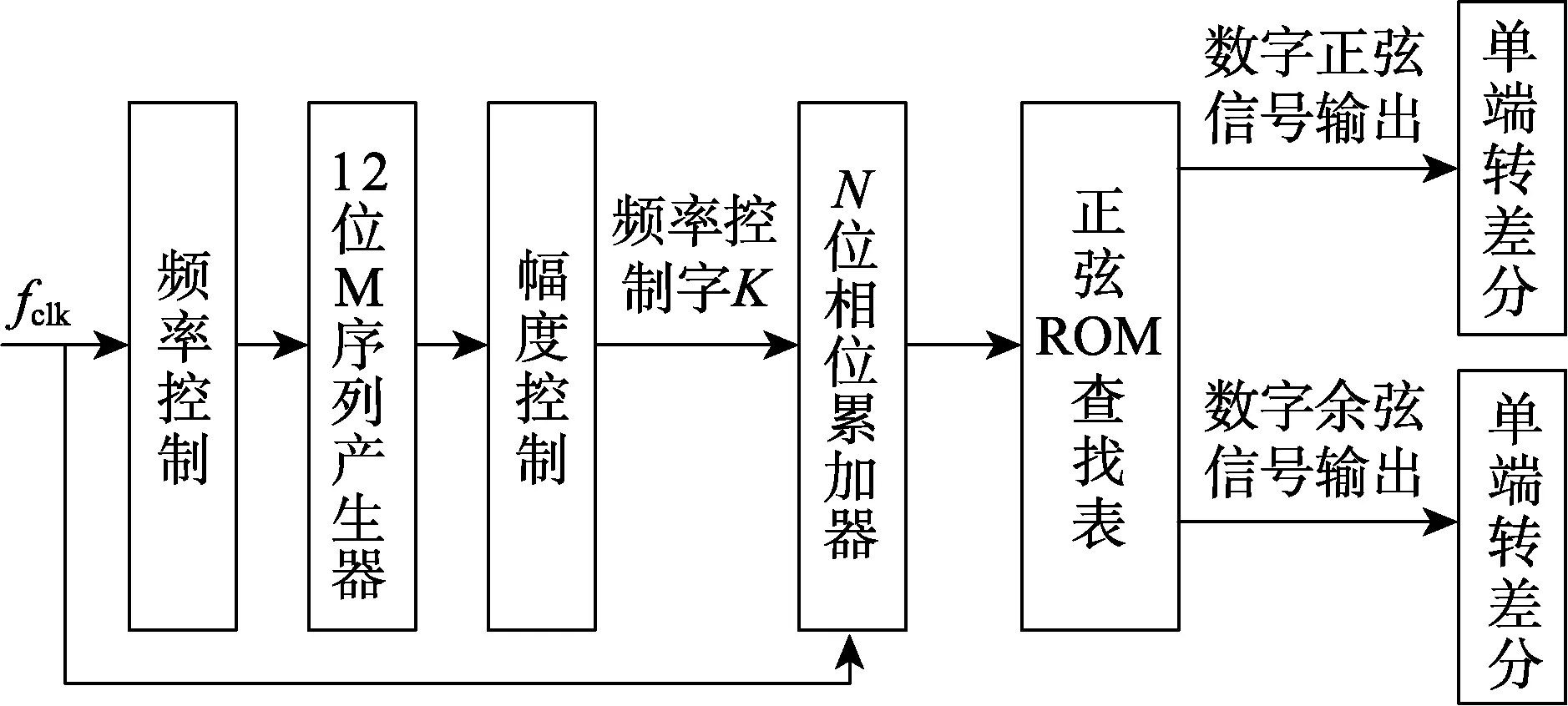

基帶噪聲調(diào)幅干擾數(shù)字信號的產(chǎn)生結(jié)合了 M 序列產(chǎn)生器[9]和DDS技術(shù)[10],具體的實(shí)現(xiàn)框圖如圖8所示。12位 M序列產(chǎn)生器的輸出是性質(zhì)類似于白噪聲的偽隨機(jī)序列,將其分別與數(shù)字正弦信號和數(shù)字余弦信號相乘,對應(yīng)得到噪聲調(diào)幅正弦信號和噪聲調(diào)幅余弦信號。

圖8 基帶噪聲調(diào)幅干擾數(shù)字信號的產(chǎn)生流程框圖

2.2 噪聲調(diào)頻干擾信號產(chǎn)生原理

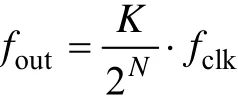

基帶噪聲調(diào)頻干擾數(shù)字信號的產(chǎn)生主要參考DDS技術(shù)。FPGA實(shí)現(xiàn)基帶噪聲調(diào)頻干擾數(shù)字信號的流程如圖9所示。

圖9 基帶噪聲調(diào)頻干擾數(shù)字信號的產(chǎn)生流程框圖

正弦信號和余弦信號的頻率的計(jì)算公式為

其中,K是頻率控制字,N是相位累加器的數(shù)據(jù)位寬,fclk是基準(zhǔn)時鐘頻率。12位M序列產(chǎn)生器的輸出是性質(zhì)類似于白噪聲的偽隨機(jī)序列,這些序列值被用作頻率控制字K。由于N和fclk為固定值,當(dāng)K呈噪聲變化時,輸出信號的頻率fout也呈噪聲變化,即為基帶噪聲調(diào)頻信號[11]。

2.3 噪聲調(diào)相干擾信號產(chǎn)生原理

噪聲調(diào)相干擾信號的具體實(shí)現(xiàn)框圖如圖10所示。將12位M序列產(chǎn)生器的輸出與N位相位累加器的輸出相加,兩者之和用作正弦 ROM查找表的輸入,從而實(shí)現(xiàn)干擾信號的調(diào)相。

圖10 基帶噪聲調(diào)相干擾數(shù)字信號的產(chǎn)生流程框圖

2.4 距離拖引干擾信號產(chǎn)生原理

距離拖引干擾主要是通過對收到的雷達(dá)照射信號進(jìn)行延時實(shí)現(xiàn)。具體的,雷達(dá)信號通過天線進(jìn)入干擾機(jī),由AD9361處理并傳輸給FPGA。FPGA對該信號進(jìn)行存儲、延遲,再通過AD9361和天線進(jìn)行發(fā)射作為假目標(biāo)信號回波。在該過程中,可以通過控制延遲時間移動假目標(biāo)的位置。信號的延遲在FPGA中可以用FIFO結(jié)構(gòu)實(shí)現(xiàn)[12]。FIFO的深度表示信號的延遲,假設(shè)FIFO的深度為D,系統(tǒng)時鐘頻率為fclk,則延時為D/fclk,對應(yīng)的距離為c·D/(2fclk),c是電磁波在真空中的傳播速度。距離拖引干擾信號的產(chǎn)生流程如圖11所示。

圖11 距離拖引干擾信號的產(chǎn)生流程框圖

3 實(shí)驗(yàn)測試

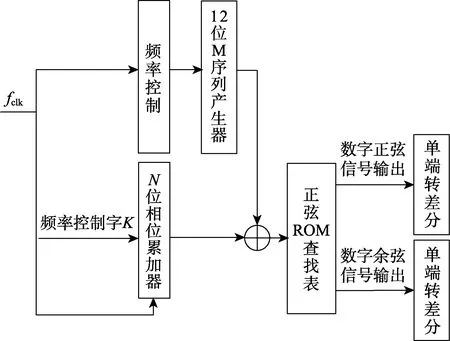

本文設(shè)計(jì)的模擬器可以根據(jù)實(shí)際需求產(chǎn)生多種雷達(dá)干擾信號,信號中心頻率最高可達(dá)6 GHz,信號帶寬最大可達(dá) 56 MHz。本次實(shí)驗(yàn)選擇四種典型干擾信號進(jìn)行實(shí)現(xiàn),分別為:噪聲調(diào)幅干擾信號,中心頻率1 GHz,帶寬10 MHz;噪聲調(diào)頻干擾信號,中心頻率1 GHz,帶寬50 MHz;噪聲調(diào)相干擾信號,中心頻率1 GHz,帶寬50 MHz;距離拖引干擾信號,接收的雷達(dá)信號為線性調(diào)頻信號,中心頻率1 GHz,帶寬5 MHz。

將 AD9361評估板插接到 SP605評估板,并將AD9361評估板連接至頻譜分析儀,觀察四種信號的頻譜,實(shí)驗(yàn)結(jié)果如圖12所示。

圖12 四種干擾信號的頻譜圖

4 結(jié)語

本文基于射頻收發(fā)芯片AD9361設(shè)計(jì)了一種雷達(dá)干擾信號模擬器,利用FPGA配合AD9361通過軟件無線電技術(shù)實(shí)現(xiàn)各種雷達(dá)干擾信號的模擬產(chǎn)生,給出了模擬器設(shè)計(jì)思路和程序設(shè)計(jì)流程。測試結(jié)果表明該模擬器的雷達(dá)干擾信號具有較好的性能。該模擬器可作為雷達(dá)、雷達(dá)對抗及相關(guān)專業(yè)學(xué)生的實(shí)驗(yàn)教學(xué)輔助設(shè)備,有助于學(xué)生掌握雷達(dá)、雷達(dá)干擾系統(tǒng)和信號的相關(guān)知識。

- 實(shí)驗(yàn)技術(shù)與管理的其它文章

- 探索分子量對界面結(jié)晶影響的實(shí)驗(yàn)設(shè)計(jì)

- 高校實(shí)驗(yàn)技術(shù)人員績效綜合測評體系的構(gòu)建

- 美國依托大學(xué)建設(shè)的世界級實(shí)驗(yàn)室管理運(yùn)行機(jī)制研究

——以國家實(shí)驗(yàn)室為例 - 高校分析化學(xué)實(shí)驗(yàn)室建設(shè)探索與實(shí)踐

- 以能力提升為導(dǎo)向的企業(yè)實(shí)訓(xùn)課程考核方法研究

- 基于桌面云實(shí)驗(yàn)室的攝影測量實(shí)驗(yàn)教學(xué)模式與實(shí)踐