CTCS3-300T車載設備測速測距單元硬件改進方案研究

賈云光

(1.北京全路通信信號研究設計院集團有限公司,北京 100070;2.北京市高速鐵路運行控制系統工程技術研究中心,北京 100070)

1 概述

1.1 CTCS3-300T簡介

CTCS3-300T 的 測 速 測 距 單 元(SDU)是CTCS3-300T 列控車載設備對列車速度進行監測的重要前端環節,其可靠性和準確性直接影響了整個系統性能指標。

伴隨著CTCS3-300T 列控車載設備的大量裝備以及長時間運行,列控車載設備在運行過程中出現了許多無法解決的偶發性故障,其中最具代表性的是SDU 表現出的偶發性故障。在我國,高鐵運行的可靠性和安全性要求在世界上居于前列,即使故障率較低的偶發性故障,也逐漸成為了人們出行關注的焦點,本著對高鐵運輸高品質的更高追求,偶發性故障解決也成了技術人員勢必攻克的難點。

眾所周知,定義為偶發性故障就說明該故障解決難度較高,因其偶發性、不容易復現,故障解決就無從入手。本文介紹了如何解決和查找該問題并提出優化方案,以便為后續解決類似問題提供可借鑒的思路和方法。

1.2 測速測距單元偶發性故障情況

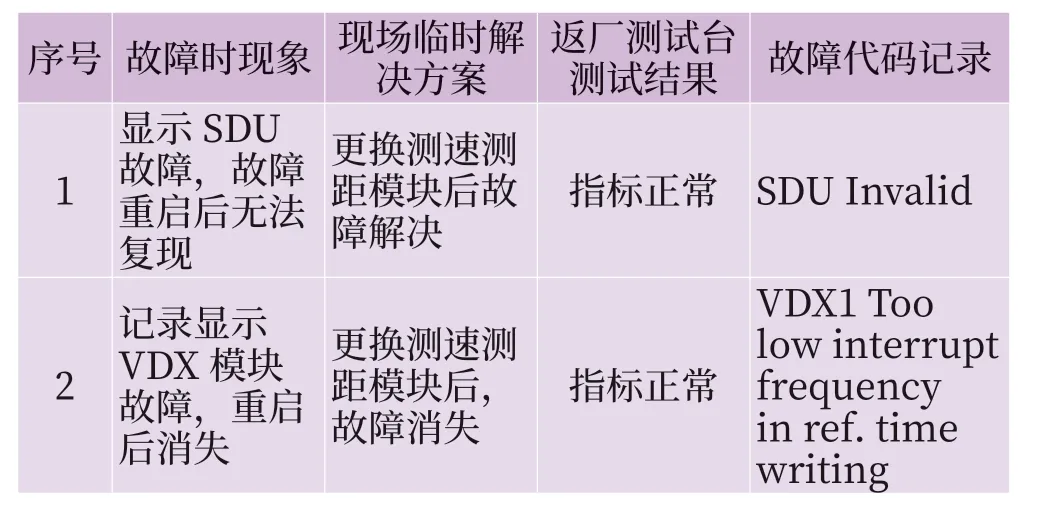

經過運營統計及技術人員初步分析,CTCS3-300T SDU 的偶發故障現象及記錄主要如表1 所示。

表1 測速測距單元偶發性故障現象Tab 1 SDU accidental fault phenomenon

表1 中所述兩種故障,在設備更換SDU 模塊后,故障不再出現。但是設備返廠后,各項測試指標正常,即生產人員和技術人員均無法確定該模塊的故障點,判定為偶發性故障或總線干擾所致。

2 存在問題及分析

2.1 問題查找及分析

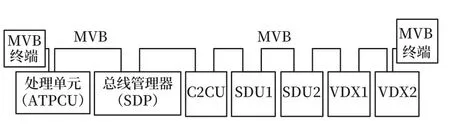

偶發性故障在現場很難復現,通過對現場故障長時間統計,鎖定偶發故障率相對較高的車載設備單元,在室內測試環境中進行長時間拷機測試以及施加各種技術手段,個別模塊故障最終得以復現,主要出現以下3 類故障,且涵蓋現場故障記錄,如表2 所示。

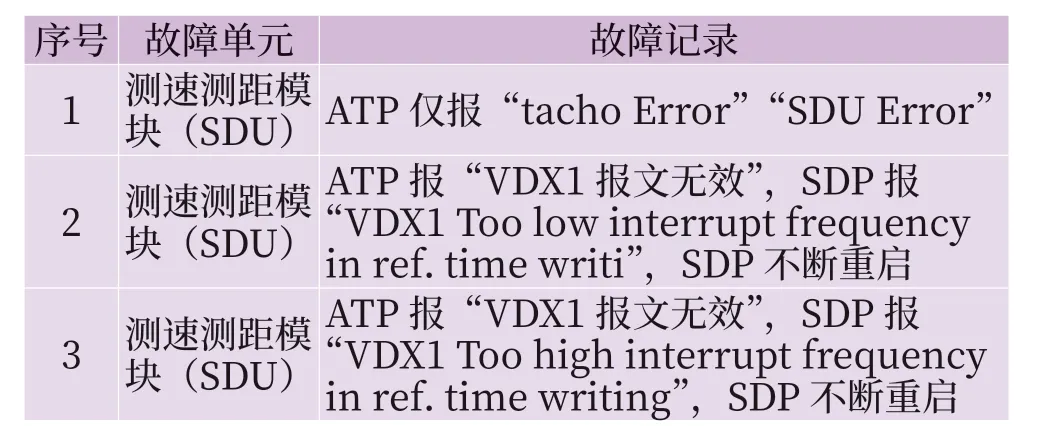

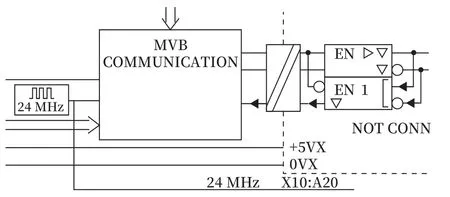

CTCS3-300T 系統中,ATP 通過總線管理單元(SDP)管理各個模塊,總線結構如圖1 所示,SDU通過MVB 總線與CTCS3-300T 車載設備中的各個單元進行連接。當SDU 需要在總線中發送或者接收數據時,會將自己的MVB 管理芯片MVBC01 設置為不同的電平狀態,從而獲得總線發送數據的相應權限。

表2 測試測距單元室內測試故障記錄Tab 2 Fault record of SDU indoor test

圖1 CTCS3-300T MVB總線拓撲圖Fig.1 Topology of CTCS 3-300T MVB

上述3 種故障,均由SDU 單元引起,卻體現為其他單元的故障記錄,因此判定:SDU 的MVBC01 在讀取或寫入總線時存在異常。在確定問題初步原因時,就需要對SDU 的相關電路進行分析和研究,確定故障根源,找到優化方案。

2.2 原理圖分析

SDU 單元主要由兩塊電路板組成:IOCPU 板和擴展板,IOCPU 負責MVB 通信及相關邏輯,擴展板用于速度信息的采集。MVB 芯片周邊電路如圖2 所示, MVBC01 芯片通過FPGA 芯片連接到485 芯片向總線收發數據。

詳細電路如圖3 所示。

MVBC01 芯片為MVB 控制芯片。有3 根引腳控制信號輸入,輸出和輸出允許。通過示波器連接3 個引腳觀察在發現相關故障時其引腳與故障現象對應的關系,經過測試和分析發現存在如表3 所示的對應關系。

圖2 測速測距單元MVB電路結構圖Fig.2 Circuit diagram of SDU MVB

圖3 MVB周邊纖細電路圖Fig.3 MVB peripheral thin circuit diagram

表3 MVB控制信號與故障現象的對應關系Tab 3 Correspondence between MVB control signal and fault phenomena

由表3 可知在相關故障發生時,其原因是相應管腳運行時電平出現異常導致某一管腳固定在高電平或低電平。為了進一步分析導致高低電平的原因,對電路原理圖進行分析,基本確定了如下部分電路可能存在問題:

1)LTC485 存在問題;

2)FPGA 存在問題;

3)MVBC01 存在問題;

4)其他問題。

為排除器件本身存在批次問題,測試采用替換方法,經過反復試驗,最終排除了器件批次質量問題。

2.3 問題發現

在排除了各種因此器件質量問題導致的因素之外,重新對MVBC01 控制LTC485 的引腳進行監測分析,發現在一定時間內存在輸出不穩定。而造成這種不穩定因素主要可能來自干擾。

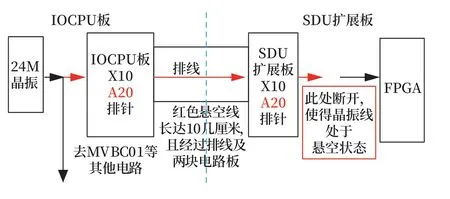

經過對電路板電路及PCB 仔細分析發現,SDU的CPU 板上的24M 晶振除了給MVBC01 使用以外,還通過長的PCB 線引到X10 排線,再經排線引到IO 板。VDX 的IO 板這條線是直接接到芯片的。但SDU 的IO 板這條線是懸空的,如圖4 所示。

如此長的懸空線,會因PCB 布線及各部分阻抗的不同,導致作為天線將空間電磁干擾引入電路從而導致設備出現問題。

圖4 晶振懸空線示意圖Fig.4 Schematic diagram of crystal suspension line

為驗證對干擾來源的分析,進行如下測試。如圖4 所示,在晶振懸空線上,人為加入短暫干擾,然后恢復,出現如表4 所示的3 種結果。

從表4 中,可以看出,短時的干擾確實能夠造成設備的死機,并能夠復現現場故障,從而驗證邏輯分析的正確性。

3 改進方案

3.1 優化方案

根據電路及測試驗證,晶振延長線是導致MVC01 偶發死機的根本原因,其引入干擾會出現現場偶發的3 種故障現象。為解決引入干擾的問題,需要切斷引入干擾的輻射源,根據電路改造及優化的可行方案,提出如下3 種優化方案。

1)取消晶振延長線設計,從設計源頭防止該問題的發生。

2)在晶振延長線末端,加入高阻抗電阻。

3)優化PCB 版布局,改變晶振延長阻抗。

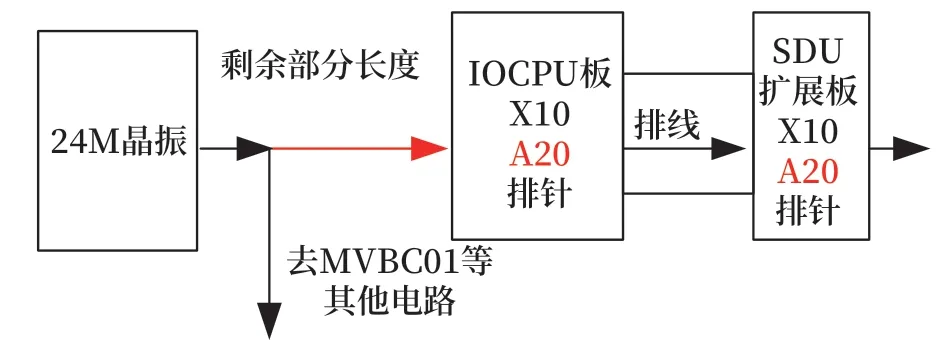

方案1:設計優化

晶振延長線設計原本是用于VDX 單元的電路設計,在SDU 中由于沒有相關電路設計,因此該懸空線應該從設計上去掉,如圖5 紅色虛線部分。

圖5 方案一 設計優化原理圖Fig.5 Scheme 1 Schematic diagram of design optimization

方案2:在晶振延長線中串入電阻

天線設計中,改變天線阻抗可以降低天線接受外界電磁波的能力,因此在晶振中串入高阻抗的電阻,可以有效降低外界串入晶振延長導致的干擾問題,如圖6 所示。

圖6 方案二 優化電路示意圖Fig.6 Scheme 2 Schematic diagram of optimized circuit

方案3:縮短晶振延長

如圖7 中紅色部分所示,是將IOCPU 板上的A20 針拔除。這樣,24 MHz 晶振線上懸空只有3 cm 左右,大大縮短了晶振延長線,從而能從很大程度上降低干擾。

圖7 方案三 優化原理圖Fig.7 Scheme 3 Schematic diagram of optimization

3.2 方案比較及優選

3.1 節中的3 種方案都可以解決測速測距單元存在問題,對比3 種方案,綜合考慮工程實施難度,選擇方案3,原因如下。

方案3 中晶振延長線原本懸空,拔除CPU 板上的X10-A20 后,原理上對整個電路圖沒有任何改動,對電路的功能沒有任何影響,如圖8 所示。

圖8 方案實施的A20針腳位置圖Fig.8 A20 pin location map in scheme implementation

對于中長期考慮,應從設計上根本解決電路設計問題,方案一無疑是最佳的解決方案。

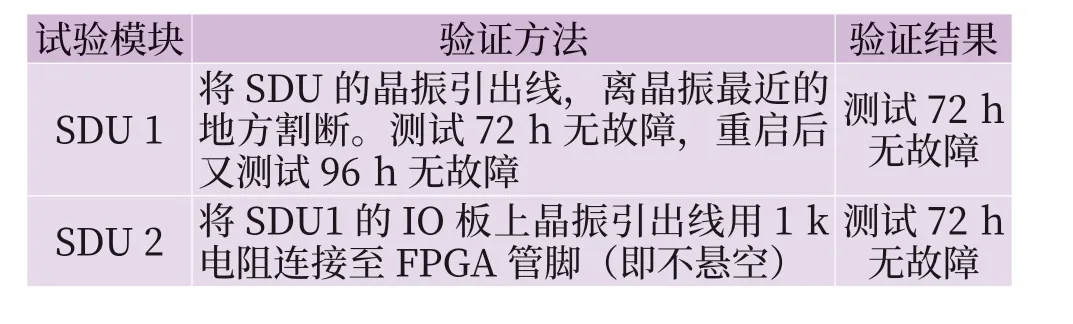

3.3 測試及驗證

使用兩個SDU 測試,這兩個SDU 原來均能在24 h 內復現故障。針對兩個SDU 采取不同的措施進行驗證,如表5 所示。

表5 測試驗證結果Tab 5 Test verification results

后恢復兩個模塊,故障在24 h 內復現,綜上,晶振延長線的懸空是導致問題出現的原因。

4 總結

本次改進方案已經在全路2000 套CTCS3-300T 級列控車載設備上進行了應用,經過近一年多的觀察,該偶發性故障未再發生,效果良好,測速測距相關類故障下降50%。