基于邊界掃描的可測試性硬件電路設計

陳建

【摘?要】本文對基于邊界掃描的電路板硬件設計給出參考準則,通過介紹設計過程中的關鍵點達到提升可測試性的目的。

【關鍵詞】邊界掃描;硬件設計;可測試性

1、研究背景

隨著邊界掃描技術的成熟,國際上很多IC生產廠商制造的IC芯片都遵循該標準,如Xilinx、ARM、Altera、Intel等在其公司的產品中已大量的采用邊界掃描標準。在板級測試中使用該標準需要一定的設計準則以提高可測試性。

2、可測試性設計

2.1器件選型

電子元器件選型時應考慮是否有同等功能的邊界掃描器件可以替代,如果有應優先選用邊界掃描器件。當前復雜的大規模集成電路通常都為邊界掃描器件。

2.2 JTAG接口設計

a)電路板上所有的邊界掃描器件都應該將TMS、TCK、TDI、TDO、TRST信號引出到JTAG插座上;

b)所選邊界掃描器件的JTAG端口如果具有雙功能引腳,應保留JTAG測試的功能性;

c)所選邊界掃描器件的JTAG功能如果具有使能端,應該預留測試控制點;

d)對芯片JTAG的五個引腳禁止與電源或地直接相連;

e)對可編程器件的JTAG測試口以及其它多功能器件的JTAG測試口,在設計時,原則上只作測試用,不要復用為一般的I/O,不得已采用的特殊情況下應保留測試的功能。

2.3掃描鏈路設計

掃描鏈路配置是邊界掃描測試的基礎,電路板中所選用的邊界掃描器件應按照串行方式或者獨立多路徑方式連接,且所有的邊界掃描器件都應可控。

在連接掃描鏈路時,應注意電壓兼容問題。對于不同工作電壓系列的芯片,不能將芯片的JTAG信號直接相連,應進行電壓轉換以使電壓兼容。

JTAG信號線在設計時應優先考慮穩定性和各自功能的實現。TCK和TMS信號作為公用信號,在進行測試時典型扇出不要多于8個,為保證電路的可靠性,一般在扇出大于4個時應該進行緩沖驅動處理。

2.4非邊界掃描器件的可測試性設計

非邊界掃描器件的測試的基本原則是盡量使非邊界掃描器件被邊界掃描單元完全包圍,可以是直接包圍也可以是間接包圍,連接示意圖如圖1和圖2所示。

3、測試系統實例硬件設計

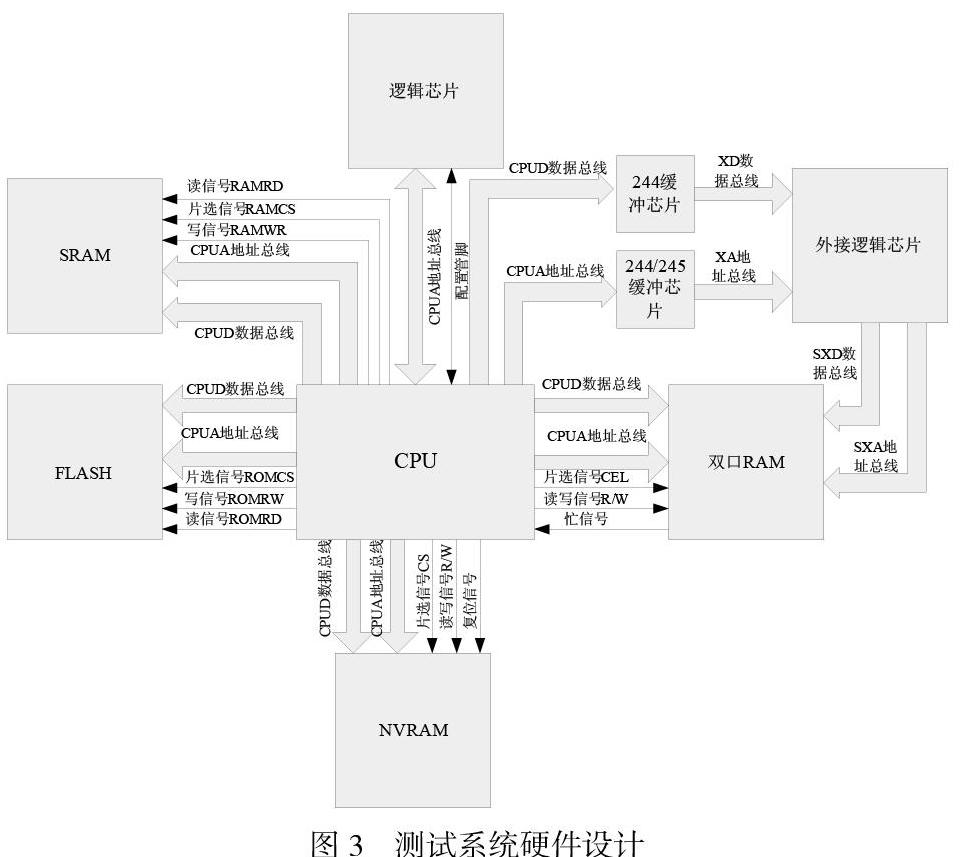

以下基于某型電路板構建了一套完整的邊界掃描測試系統,系統的總體結構如圖所示。

利用CPU芯片、板上邏輯芯片和1片外接的邏輯芯片完成整板的覆蓋及測試。主要測試內容包括:

a)CPU芯片與板內邏輯器件之間收和發數據線以及相應配置管腳的互聯測試;

b)CPU芯片與外接邏輯之間通過244/245等驅動的地址線、數據線、控制線的互聯測試;

c)CPU芯片與SRAM之間的地址、數據和控制線的功能性測試;

d)CPU芯片與FLASH之間的地址、數據和控制線的功能性測試;

e)CPU芯片與NVRAM之間的地址、數據和控制線的功能性測試;

f)CPU芯片與雙口RAM之間的地址、數據和控制線的功能性測試;

g)外接邏輯芯片與雙口RAM之間的地址、數據和控制線的功能性測試。

在電路設計過程中對使用到的非邊界掃描器件應盡量將信號線都接入邊界掃描器件中,對于通過板上連接器上去往板外的信號,在底板母板上設計一塊接插板,將連接器上的信號引進底板的邏輯器件上,從而可對該部分信號進行互聯測試。

4、結論

本文基于邊界掃描測試技術,介紹了硬件電路設計時需符合邊界掃描測試的準則,包括了器件選型、JTAG接口設計、掃描鏈路設計以及關于非邊界掃描器件的設計,并通過具體實例闡述了具體的設計方法,從而達到提升硬件電路板可測試性的目的。

(作者單位:中國航空工業集團公司洛陽電光設備研究所)