一種基于FPGA的模擬潛艇噪聲信號產生模塊的設計

漆萬鵬,劉天華,晏生劍

(1.海裝駐武漢地區軍事代表局,湖北 武漢 430000;2.海裝駐宜昌地區軍事代表室,湖北 宜昌 443003;3.中國船舶重工集團有限公司 海聲科技有限公司,湖北 宜昌 443005)

0 引言

隱蔽性在潛艇作戰效能中起著決定性作用。水聲支援干擾系統,其使命是通過逼真模擬潛艇目標聲譜特征及行為特性,形成對敵反潛預警系統和人員心理的干擾及欺騙,提升潛艇作戰效能。

通常情況下,水聲支援干擾系統是由信號處理機完成聲特征譜信號的算法實現,信號產生模塊實現信號的數模轉換,功放模塊實現信號的功率放大,換能器實現信號的電聲轉換。為了靈活適配各類平臺,方便系統前期方案驗證和效能評估,必須降低系統復雜度。功放模塊和換能器是發射系統不可缺少的2個環節,所以將信號處理機與信號產生模塊合二為一是比較理想的解決方案。本文介紹了一種基于FPGA的模擬潛艇噪聲信號產生模塊,綜合了信號處理機與信號產生模塊二者的功能,既能實現聲特征譜信號生成算法,又能實現數字信號的數模轉換。

該信號產生模塊根據上位機下發的參數命令可以實時產生線譜、調制譜和寬帶噪聲信號,信號經過合成運算、匹配濾波后,再通過高頻、中頻、低頻3路D/A通道輸出,控制發射系統產生模擬潛艇噪聲信號。

1 組成及工作原理

1.1 硬件組成

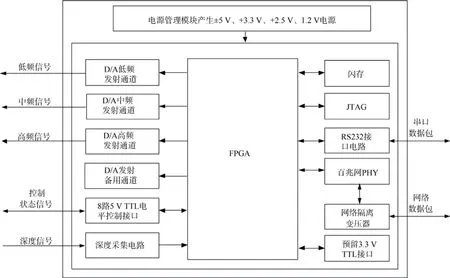

信號產生模塊硬件電路主要由供電電路、FPGA主控電路、串口通信電路、以太網通信電路、深度采集電路、D/A輸出電路、TTL信號控制電路組成,如圖1所示。

圖1 硬件組成框圖Fig.1 Hardware composition block diagram

1.2 工作原理

信號產生模塊需要根據上位機下發的命令參數實時產生相應的模擬潛艇噪聲信號。模擬潛艇噪聲信號的特征需要通過信號發射系統(功放發射模塊和換能器)實際工作的頻率特性來進行調整,信號產生模塊根據反復測試后確定的參數產生模擬潛艇噪聲電信號,再經發射系統發射出逼真的模擬潛艇噪聲水聲信號。

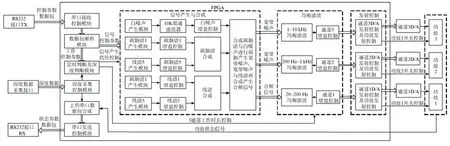

FPGA系統接收到命令參數數據包后,將命令參數數據解析為信號控制參數和工作控制參數。

信號控制參數包含的信息有白噪聲的增益控制、開關控制;每根線譜的起始頻率、截止頻率、調頻時間、增益控制、開關控制;每根調制譜的起始頻率、截止頻率、調頻時間、增益控制、開關控制;各發射通道的增益控制、開關控制。通過信號控制參數可以確定白噪聲的增益特性,線譜數量、線譜頻率特性、線譜增益特性,調制譜數量、調制譜頻率特性、調制譜增益特性。然后將白噪聲、線譜、調制譜進行合成生成寬帶噪聲和合頻信號。此時的寬帶信號和合頻信號與發射系統不匹配,需根據各發射通道實測的頻率特性進行均衡濾波,最后經發射控制模塊輸出給功放,以達到模擬潛艇噪聲信號的真實性。

工作控制參數包含的信息有系統啟動總延時,深度開關設定值、深度開關啟停、達到指定深度后延時、各發射通道工作時長、任務編號。如果深度開關停止,則系統根據系統啟動總延時定時,定時完成后啟動信號產生與合成模塊。如果深度開關開啟,則系統啟動總延時、定深啟動、達到指定深度后延時同時工作,深度后延時定時器在達到指定深度后才會開啟,與系統啟動總延時定時器并行工作,以2個定時后定時完成的控制信號作為信號產生與合成模塊啟動標識。各發射通道工作時長定時器在信號產生與合成模塊開啟后開始工作,定時完成后關閉均衡濾波模塊停止信號輸出。該系統可以同時設置3組參數存儲在FPGA的RAM中,每組參數的編號通過參數編號選項區分,參數的工作順序為編號1、編號2、編號3。信號產生模塊工作原理如圖2所示。

圖2 工作原理框圖Fig.2 Working principle block diagram

2 硬件電路設計

FPGA是本電路中的核心控制器件,串口協議解析,各種信號實時產生,信號合成,濾波器實現等均由其實現。電路中選擇 ALTERA公司颶風 3系列EP3C40F324I7作為控制器件[1]。

網絡傳輸功能是本設計中預留的功能,為后期信號處理機控制信號產生模塊做準備。該電路主要實現百兆以太網全雙工網絡通訊。百兆網絡物理層采用以太網芯片 DP83640實現,與 FPGA內部MAC控制器通過MII接口連接。

D/A芯片選用TI公司的16位分辨率的D/A芯片DAC8830ICD,輸出信號先經過1級電壓跟隨電路增加驅動能力,然后經過電容隔直流電壓[2],接著通過1階RC低通濾波器進行平滑慮波,最后通過差分運放THS4130放大輸出[3]。

RS232通信選擇MAXIM公司的低功耗收發器MAX3227。選用表壓型深度傳感器,由 ADS8320采樣得到深度數據。控制輸出、狀態輸入接口使用電平轉換芯片SN74LVC2T45實現3.3 V與5 V TTL電平轉換系統輸入電壓為±8 V,需要產生±5 V,+3.3 V,+2.5 V,+1.2 V共5路穩定電源。+5 V和+3.3 V電源選用LINEAR公司的DCDC芯片LT3991產生。+2.5 V和+1.2 V電源電流需求較小,選用LINEAR公司的VLDO芯片LT3022產生。-5 V電源選用TI公司的負輸入電壓LDO芯片tps7a3001產生。

3 FPGA片內邏輯設計

3.1 白噪聲的實現

偽隨機序列是人為構成的數字序列,只包含高低2種電平,它是離散的,不具有真正的正態分布特性,但當序列的長度逼近無限大時,它趨于正態分布[4]。

本設計中數字白噪聲是使用63位移位寄存器產生的m序列偽隨機碼實現。移位寄存器noise的初始值為63位2進制數63'h491290201840B084(16進制表示方法),移位寄存器每個時鐘周期右移一位,將移位寄存器第 0位 noise[0]與第 1位noise[1]進行異或運算,運算結果賦值給第 62位noise[62],此運算方法作為m序列特征多項式。

因為使用D/A芯片為16位分辨率,所以M序列輸出也定義為16位寄存器。將移位寄存器noise的低16位noise[15:0]作為M序列輸出,即得到16位白噪聲數據。

3.2 線譜的實現

線譜信號為單頻或者調頻的正弦信號,可以使用Altera官方提供的NCO IP Core來實現。NCO IP Core即數字壓控振蕩器知識產權核可以通過多種算法實現一個離散的正弦波信號輸出[5]。正弦波信號時域方程如下:

式中:T為該模塊的工作時鐘周期;f0為輸入頻率控制字φINC設置的未調制的輸出信號頻率;fFM是調制頻率控制字φPM決定的調制頻率;φPM為該輸出正弦波的調制相位,,由輸入控制字p的比特位數pwidth決定它的精度;φDITH為模塊內部自身的不穩定而引起的相位雜散(噪聲);幅值 A=2N-1,其中N為幅值精度,取值在4~32之間。

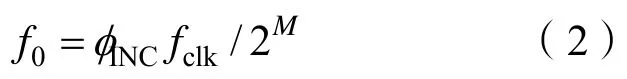

f0與頻率控制字φINC滿足以下關系:

式中:M為相位累加器精度;fclk為模塊工作時鐘頻率。

輸出信號頻率精度:

通過Altera公司的FPGA編譯軟件 QuartusII 12.0 中的MegaWizard Plug-In Manager 功能調用NCO V12.0 軟核,配置軟核中相應參數,根據式(1)-(3)來實現所需要的頻率輸出功能。NCO軟核的實現選擇 CORDIC算法,相位累加器精度設為24位,輸出幅值精度為16位,輸入時鐘頻率為340 kHz。CORDIC算法實施方案選擇串行模式,目標器件選擇Cyclone III,1路NCO通道,1路頻率預置分支,單路正弦信號輸出。

NCO模塊信號輸出是連續變化的,不隨φINC設置值發生改變而間斷。為了實現NCO模塊的線性調頻信號輸出,需要等時等量的改變φINC設置值。

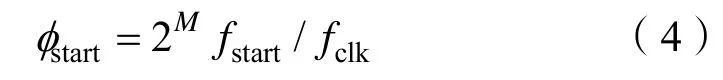

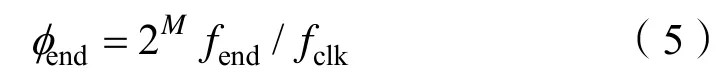

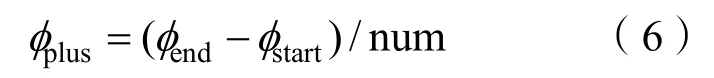

信號頻率從fstart到fend線性變化,信號輸出時間寬度為φwidtht,每1 s改變INCφ設置值,則INCφ變化次數為 n um =twidth/1s 。根據關系式(2)得,起始頻率fstart對應的φINC設置值為

截止頻率fend對應的φINC設置值為

每1 s后φINC設置值步進量為

收到信號控制參數后,首先根據式(4)-(6)分別計算出線譜產生的起始頻率、截止頻率和每秒頻率增量,然后將 NCO模塊的復位信號nco_reset_n拉低,對NCO模塊進行初始化,使能NCO模塊時鐘使能信號nco_clken。然后將φstart賦值給NCO模塊的相位累加寄存器nco_pfi_inc_i,輸出起始頻率正弦信號,等待1 s將φstart與φplus相加值賦給 nco_pfi_inc_i,輸出下一個頻率遞增的信號,像這樣連續輸出(num-1)個頻率遞增的正弦信號就實現了調頻線譜信號輸出。如果設置的調頻信號的起始頻率與截止頻率一致,則輸出為固定線譜。

3.3 信號合成與寬帶噪聲的實現

寬帶噪聲是多根調制譜信號(單頻或者調頻的正弦信號,與線譜實現方式一致)相加與白噪聲調制出來的寬帶譜信號,是白噪聲信號與調制譜信號運算的結果。合頻信號是多根線譜信號與寬帶譜信號相加的結果。

因為單根線譜、調制譜信號均為16位有符號數,5根線譜、調制譜信號相加有溢出的可能,為了避免數據溢出,將16位有符號數轉換為19位有符號數,然后將 5根線譜、調制譜分別相加得到線譜合信號s_sum,調制譜合信號 t_sum。根據有符號數移位方法,正數溢出取最大值,負數溢出取最小值,將調制譜合頻信號轉換為16位有符號數t_sum_buf[6]。

將(t_sum_buf+16’h8000)的16位無符號數調制譜合頻信號與16位有符號數白噪聲noise_buf相乘,根據有符號乘法運算方法,根據noise_buf的符號位來分別進行無符號數乘法運算,結果為32位有符號數t1_noise。然后換算為16位有符號數,得到用于中頻、高頻通道輸出的寬帶噪聲信號t_noise,然后將線譜s_sum與t_noise相加,并轉換為16位有符號數便得到用于低頻通道輸出的合頻信號。

3.4 均衡濾波的實現

均衡濾波的目的是為了彌補發射系統不同頻帶發射響應的不一致性,盡量使發射系統發射響應一致,逼近真實的潛艇噪聲情況。均衡濾波的實現即在 FPGA內部實現與發射系統相匹配的數字濾波器。根據單位沖激響應函數的時域特性,數字濾波器可分為IIR濾波器和FIR濾波器,這里使用具有線性相位的FIR濾波[7]。

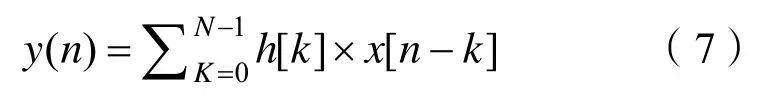

FIR有限脈沖響應濾波器的特點是單位脈沖響應是一個有限長序列,其數學表達式為

式中:N表示FIR濾波器的抽頭數;y(n) 表示第n時刻的輸出樣本;h(k) 表示FIR濾波器的第k級抽頭系數;x [n-k]表示延時k個抽頭的輸入信號。用加法器和乘法器不難實現這種結構的FIR濾波器,傳給每個乘法器的操作數就是一個FIR系數。所需乘法次數是N,加法次數是N-1。

數字濾波設計中最關鍵的部分為 FIR濾波器的實現和濾波器系數的設計。FIR Megacore 是ALTERA公司針對其主流 FPGA推出的一款商業化的數字濾波器IP核,可直接生成HDL代碼,同時其結構針對ALTERA自己的FPGA做了各種優化。FIR Megacore提供了濾波器系數導入功能,可以使用第三方工具生成的系數,這使得我們能夠通過FIR Megacore調用計算出來的濾波器系數快速實現均衡濾波。

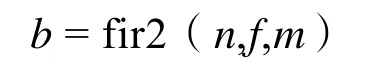

濾波器系數需要根據發射系統實際的發射響應來設計、調整。根據系統發射相應數據我們可以使用Matlab fir2函數來快速設計濾波器系數:

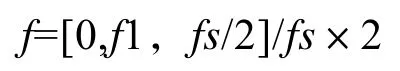

式中:n代表生產的濾波器階數;f為歸一化的頻率向量;m為與f對應的歸一化幅度向量;b即為根據頻率向量、幅度向量對應的幅頻特性所生成的n階濾波器系數[8]。假設濾波器采樣頻率定義為fs,實測數據的頻率向量為 f1,與之對應的幅度向量為m1(dB),那么歸一化的頻率向量為

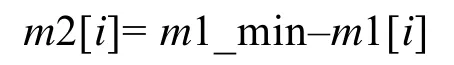

歸一化的幅度向量的轉換應先找到最小幅度值m1_min,計算各頻點將到最低幅度值的衰減量:

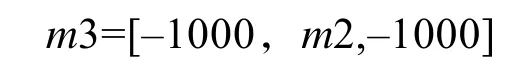

按頻率向量長度補齊幅度衰減量向量:

最后將幅度衰減量向量值換算為增益倍數值,即得到歸一化的幅度向量

濾波器階數 n的確定與均衡濾波的性能直接相關。濾波器頻率分辨率為fs/n,濾波器階數越高,頻率分辨率越小,但濾波器系數數據量也越大,占用更多FPGA資源。所以濾波器階數需要根據實際應用情況來決定,既要保證均衡濾波效果,又不浪費過多FPGA邏輯資源。本設計中,采樣頻率fs=20 kHz,濾波器階數n=1 023,濾波器頻率分辨率接近20 Hz,可以滿足均衡濾波需求。

4 試驗結果

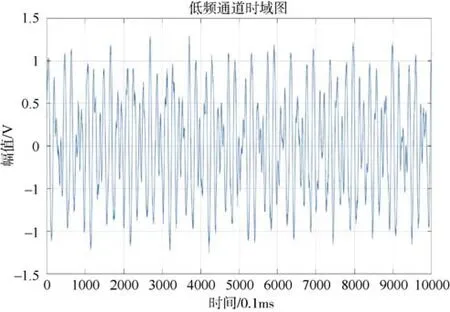

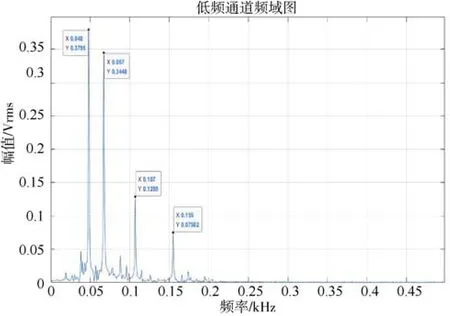

上位機軟件參數設置為:通道 1開啟、增益-6 dB;白噪聲開啟、增益-6 dB;線譜1開啟、頻率48 Hz、增益-3 dB;線譜2開啟、頻率67 Hz、增益-6 dB;線譜3開啟、頻率107 Hz、增益-9 dB;線譜4開啟、頻率155 Hz、增益-12 dB。使用示波器測量低頻輸出通道,設置示波器采樣率為10 kHz,信號穩定后抓取1 s的數據通過網口上傳到上位機,使用MATLAB對數據解析,信號時域波形如圖3所示。

對采樣數據做FFT分析,將低頻段展開后如圖4所示(縱坐標為有效值)。線譜的頻率分別為48 Hz、67 Hz、107 Hz、155 Hz與設置參數值吻合,并且信號幅度依次變小,與增益設置值相符,由于信號經過匹配濾波,所以幅度與設置增益值有一定差別。

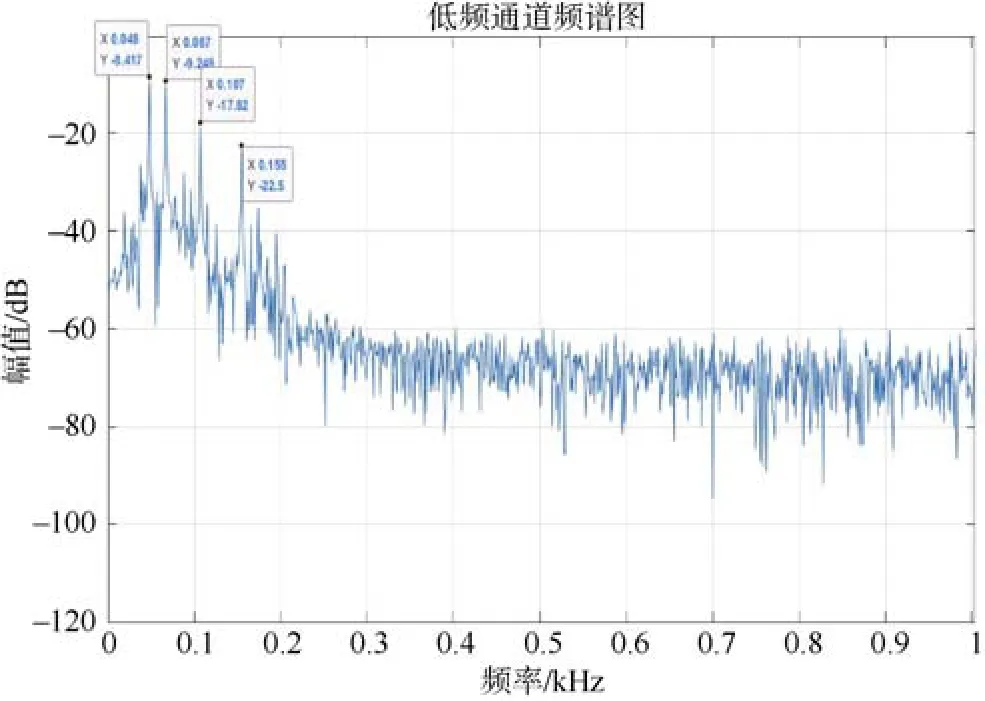

信號頻譜圖如圖5所示(縱坐標為dB),可以看到設置的4個線譜,20~200 Hz的帶通濾波器及帶內均衡濾波造成的頻譜起伏。

圖3 時域波形Fig.3 Time domain waveform

圖4 低頻段頻譜圖Fig.4 Low frequency spectrum

5 結束語

該信號產生模塊實現了聲特征譜信號生成算法,降低了水聲支援干擾系統的復雜度,縮短了項目周期,提高了水聲支援干擾系統的適裝性,已成功應用到多個預研課題,并順利完成湖上試驗。應用該信號產生模塊,能為項目前期方案驗證和效能評估提供便捷,同時該模塊預留網絡接口,可以與信號處理機連接,實現更復雜的模擬目標聲特征譜信號產生。

圖5 全頻段頻譜圖Fig.5 Full-band spectrogram