晶圓廠轉移過程中CMOS工藝可靠性研究

劉 旸

(中國電子科技集團公司第四十七研究所,沈陽110032)

1 引言

CMOS工藝是在PMOS工藝和NMOS工藝的基礎上發展起來的,是目前集成電路產品設計最常選用的工藝。CMOS電路在加工上是將NMOS器件和CMOS器件同時制作在同一襯底上,具有功耗低、速度快、抗干擾能力強、集成度高等優點[1]。由于降低制造成本、產能增加和供應商多樣性要求等因素,在CMOS的生產過程中,晶圓廠轉移是半導體行業的常見現象[2]。不同晶圓廠的工藝參數存在差異,在進行晶圓廠轉移時,需先評估晶圓廠間的工藝流程、工藝參數、原材料等的差異,才能做到在不影響用戶使用的前提下進行晶圓廠轉移[3]。

2 工藝線差異對比

某型待轉移產品原采用4英寸3μm雙層金屬P阱硅柵CMOS工藝進行加工,工藝流程如下:

備片→一氧→形成N阱→形成P阱→阱推進→預氧化→Si3N4淀積→形成有源區→場區注入→場氧化→去除Si3N4→一柵氧化→溝道調整注入→柵氧化→Poly淀積→Poly摻磷→形成多晶硅柵→PSD注入→NSD注入→ILD→形成孔→金屬淀積→金屬布線→鈍化淀積→形成PAD窗口→合金

晶圓廠轉移后,擬采用5英寸2μm雙層金屬P阱硅柵CMOS工藝生產線進行產品加工。綜合對比兩條生產線的加工工藝,涉及工藝變更的內容主要包括以下幾個方面:

1)襯底片電阻率由 4~6Ω·cm改為2.5~3.5 Ω·cm;

2)P管場區閾值調整方式由注入后阱推進改為場區形成后進行表層注入;

3)P管溝道調整注入由柵氧化前調整為柵氧化后;

4)NSD注入調整至PSD注入之前;

5)柵氧厚度由50nm改為40nm;

6)ILD由TEOS 900nm改為TEOS 200nm+BP TEOS 600nm;

7)金屬布線層厚度由1.2μm改為1.1μm。

3 差異評估

3.1 襯底電阻率

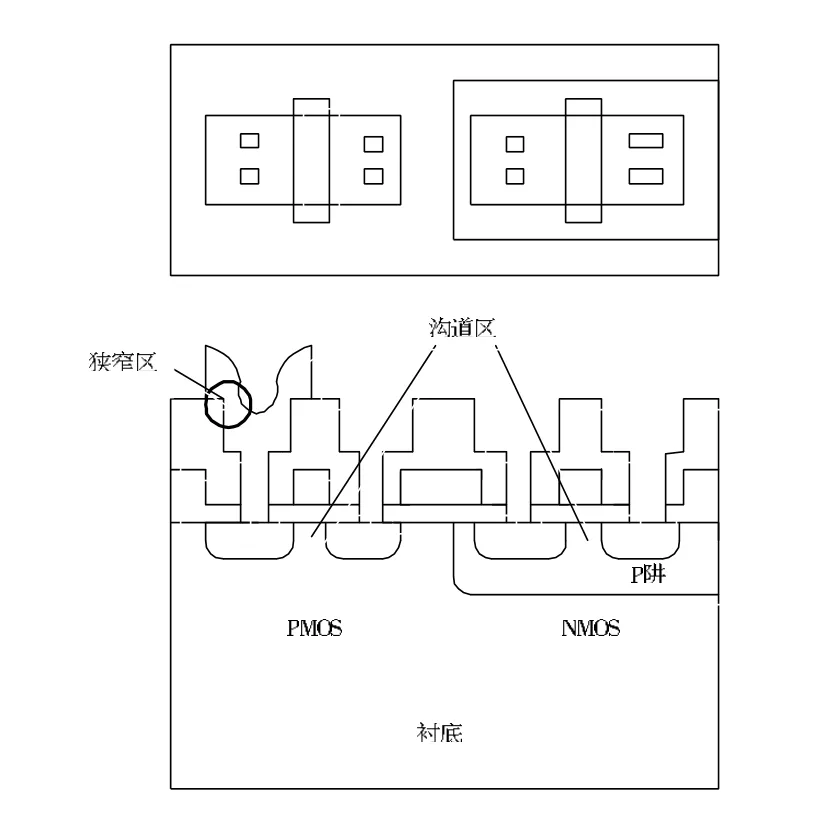

待轉移產品設計電路中包括NMOS晶體管和PMOS晶體管,縱向結構如圖1所示。

圖1 N、P管縱剖結構圖

其中,NMOS晶體管在襯底上通過注入、退火形成P阱,實際晶體管結構在P阱內加工。P阱電阻形成過程中,已改變原溝道區電阻率,通過監控P阱電阻,可確定工藝變更是否對器件造成影響。

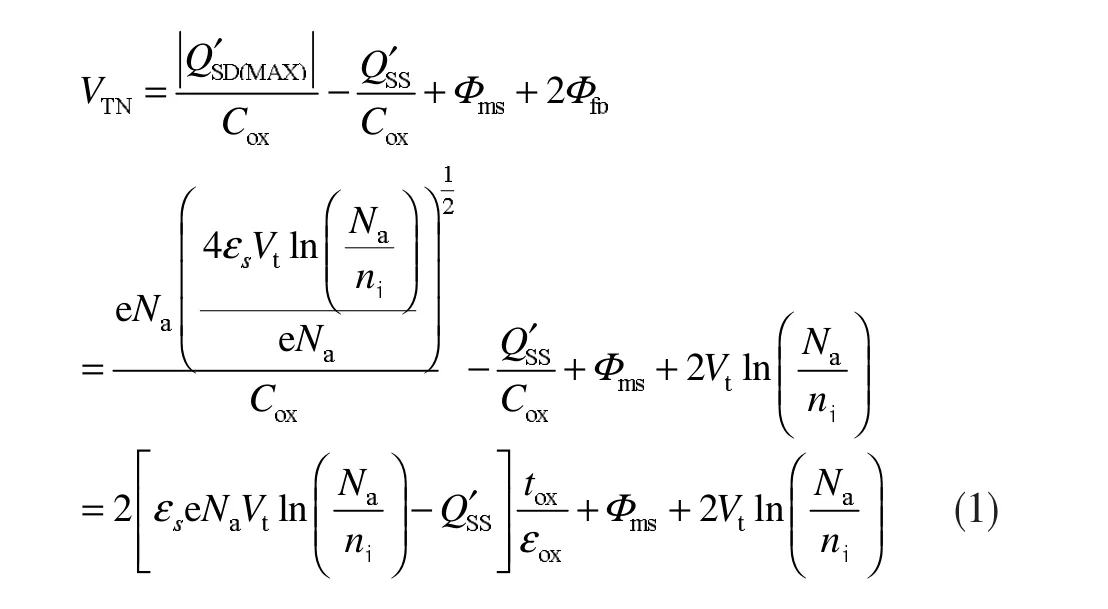

原工藝中,第26工步為PMOS晶體管溝道調整注入,通過注入來調整P管溝道區電阻率。閾值電壓與柵氧厚度、柵氧質量和溝道摻雜濃度有如下關系式:

其中,εs為半導體介電常數,e為電子電荷,Vt為熱電壓,ni為本征載流子濃度,均為固定值;εox為氧化層介電常數,QQ'SS′SS為單位面積氧化層等價陷阱電荷,隨柵氧化層的厚度和質量變化;Φφmmss為金屬半導體功函數,隨溝道摻雜濃度變化。

由式(1)可知,柵氧厚度、柵氧質量和溝道摻雜濃度為影響閾值電壓的主要工藝參數。亦可利用閾值電壓來監控相關電參數。

經PCM測試,工藝變更后P阱電阻值、PMOS晶體管閾值電壓及NMOS晶體管閾值電壓均在原PCM設計值允許范圍內,襯底片電阻率變更對產品電參數影響不大。

3.2 P管場區閾值調整

“場區”為兩個獨立晶體管間的區域,作用是防止不等電位晶體管間因漏電導致電路失效。其工作原理與常規MOS晶體管相同,僅表層向下1μm以內區域參與工作。即“場區”表層向下1μm以內區域的摻雜濃度滿足工藝設計要求,滿足電路工作需要。

PMOS管的場區注入用于提高寄生場管的開啟電壓,使其不會在電路正常工作時誤開啟。移線產品的工作電壓為5V,根據該產品的工作特點,寄生場管開啟電壓在7.5V以上,滿足產品需求,不會對產品造成影響。可通過監控場區閾值電壓確認工藝更改是否對產品造成影響。經樣管測試,產品場區開啟電壓為13V,滿足產品設計要求,對產品無影響。

3.3 P管溝道調整注入

原工藝中P管溝道調整注入是在一柵氧化后進行。溝道注入是隔著50nm的一柵氧化層進行的。在移線后的工藝中,此步注入調整至柵氧化后,注入是隔著40nm柵氧化層進行的。注入工藝有兩個工藝參數,即能量和劑量。原工藝離子注入能量為35keV,決定離子注入的深度;離子注入劑量為1.8×1012cm-2,決定摻雜區域的離子數量。根據注入原理,離子注入深度遵循如圖2所示的高斯分布示意圖。

圖2 高斯分布示意圖

P溝調整注入的離子濃度峰值應接近Si-SiO2表面,該峰值位置可通過調整注入能量來改變。即工藝變更后,可通過調整注入能量使離子濃度峰值達到工藝設計要求。P溝調整注入可通過P管閾值進行監控,經對樣管的測試,產品P管閾值電壓為1.0V,滿足產品設計要求,對產品影響較小。

3.4 NSD注入

NSD和PSD注入工步分別通過光刻打開N+區域或P+區域的窗口,進行離子注入。未打開窗口的區域由光刻膠覆蓋保護,離子無法透過光刻膠注入到硅片中,該工藝調整對產品性能無影響。

3.5 柵氧厚度

由式(1)可知,柵氧厚度、柵氧質量和溝道摻雜濃度為影響閾值電壓的主要工藝參數[4]。此三項工藝參數相輔相成,共同決定產品閾值電壓。CMOS集成電路中,對柵氧質量的要求為柵源擊穿電壓達到1nm/V以上[5]。經實際測試對比,移線后加工的樣片NMOS及PMOS晶體管的柵源擊穿電壓均在1nm/V以上,與原工藝參數差異不大,滿足工藝要求。

3μm P阱硅柵CMOS工藝采用50nm熱氧化SiO2作為柵氧化層,2μm P阱硅柵CMOS工藝采用40nm熱氧化SiO2作為柵氧化層,柵氧化層厚度有所改變。在柵氧質量相近的情況下,可調整溝道摻雜濃度使產品閾值電壓達到產品設計要求值。通過對樣片的測試,產品閾值電壓為1.0V,在產品PCM參數范圍內,柵氧層厚度改變對產品質量影響較小。

3.6 ILD工藝

ILD為金屬布線與電路間的隔離保護層,金屬布線平鋪在ILD層之上。ILD層下方還有多晶硅柵和場氧兩層介質層,形成高低不平的臺階。金屬布線采用濺射方式淀積在ILD層上,用于各晶體管之間的連接。濺射過程中,金屬原子為垂直下落,臺階處覆蓋的金屬層厚度較薄,在電路工作過程中易由于熱集中而熔斷[6]。圖1中圓圈標識處即臺階處。

BP TEOS工藝為TEOS工藝的下一代工藝,具有回流特性,可通過加溫增密的方式實現回流,減緩臺階處的陡直度,減少臺階對金屬布線的影響,降低金屬布線熱集中情況,有助于產品質量提升。

3.7 金屬布線厚度

根據GJB597A規定,頂層金屬化層厚度至少為800nm,有鈍化層保護的情況下最大電流密度為5×105A/cm2。兩條工藝線采用的摻雜鋁的成份和摻雜比例均相同,均勻性、致密性和附著性差異不大[7]。金屬化層厚度降低后,各項條件均滿足GJB要求。樣管加工完成后,經測試,延遲時間無明顯差異,兩種工藝對比延遲時間差異不大。

4 實測評估與對比

1)PCM測試評估

兩種工藝所采用的原材料接近、工藝類似,樣管加工完成后測試考核差異不大。由表1中的對比參數可以看出,兩個工藝平臺的PCM設計值相似度極高。樣品加工完成后,PCM測試結果均滿足產品PCM設計要求。

表1PCM設計值對比

2)成品率評估

對所有晶圓片進行原片級測試,中測成品率達到85%,原工藝線加工產品的中測成品率平均為72%,晶圓廠轉移后成品率明顯提升。

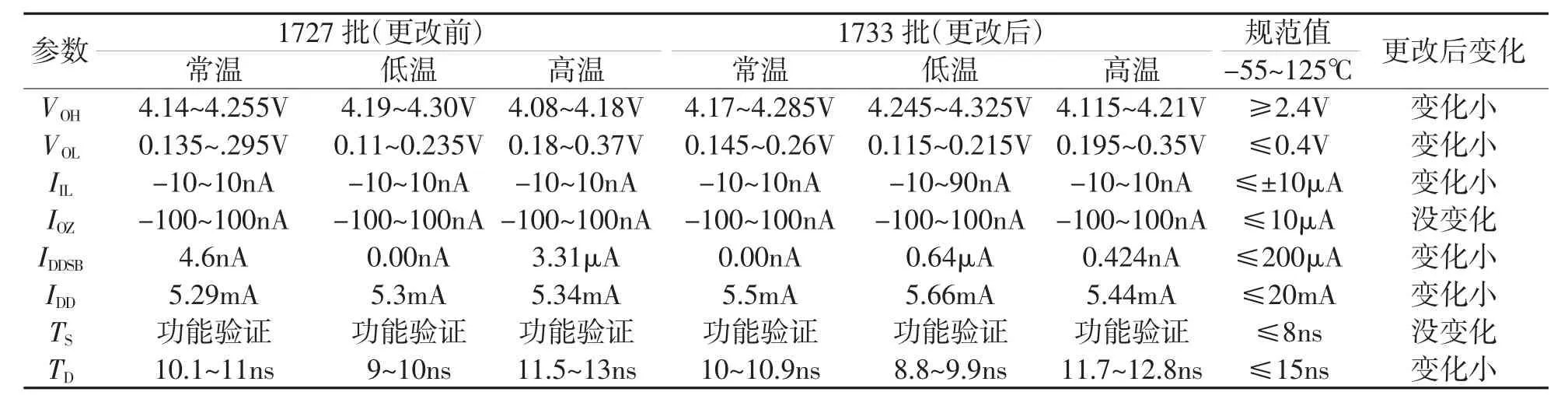

3)電參數測試評估

取晶圓廠轉移前后的兩批電路,對電參數進行對比驗證,各個電參數特性無明顯差異,且都滿足詳細規范要求。

各參數對比驗證結果見表2。

由表2數據可得出以下結論:

輸出高電平(VOH)對比:

端口的輸出電壓越高,說明端口的高電平驅動能力越強。通過以上參數對比,更改后的輸出高電平與更改前相差很小。

輸出低電平(VOL)對比:

端口的輸出電壓越低,說明端口的低電平驅動能力越強。通過以上參數對比,更改后的輸出低電平與更改前相差很小。

表2 晶圓廠轉移前后電參數對比

輸入漏電流(IIL)對比:

輸入漏電流是端口在輸入狀態下的漏電流。輸入漏電流越小,說明端口的輸入狀態越好。通過以上參數對比,更改后的輸入漏電流與更改前基本沒有變化。

輸出三態漏電流(IOZ)對比:

輸出三態漏電流是端口在輸出三態狀態下的漏電流。輸出三態漏電流越小,說明端口的輸出三態狀態越好。通過以上參數對比,更改后的輸出三態漏電流與更改前沒有變化。

靜態電源電流(IDDSB)對比:

靜態電源電流是電路在靜態條件下,電源端口的電流值[8]。靜態電源電流越小,說明電路的靜態功耗越小。通過以上參數對比,更改后的靜態電源電流與更改前變化很小。

工作電源電流(IDD)對比:

工作電源電流是電路在動態條件下,電源端口的電流值。工作電源電流越小,說明電路的動態態功耗越小。通過以上參數對比,更改后的工作電源電流與更改前變化很小。

數據最小建立時間(TS)對比:

數據最小建立時間是觸發器時鐘信號上升沿到來以前,數據穩定不變的時間。通過以上參數對比,數據最小建立時間更改前后都通過了功能驗證。

BYTE最大延遲時間(TD)對比:

BYTE最大延遲時間是A/D的高低選擇,通過以上參數對比,更改后的BYTE最大延遲時間與更改前變化很小。

綜合以上評估對比結論,晶圓廠轉移前后產品測試數據對比無明顯差異,各項指標均滿足規范要求。晶圓廠轉移不影響產品技術指標,并滿足詳細規范中的各項試驗要求,對產品使用、質量無影響。

5 結束語

通過逐一對比4英寸3μm雙層金屬P阱硅柵CMOS工藝與 5英寸 2μm雙層金屬 P阱硅柵CMOS工藝,確定7處工藝差異。經由理論分析和實際測試驗證,確認兩種工藝的工藝參數差異不大,晶圓廠轉移后,產品各項指標均滿足規范要求,且不影響原有用戶使用,此結論可為類似產品的轉移提供參考。