數字電路虛擬仿真實驗教學改革研究

馬學條, 程知群, 陳 龍

(杭州電子科技大學 電子信息技術國家級虛擬仿真實驗教學中心, 浙江 杭州 310018)

數字電子技術、計算機技術、工業控制等信息技術蓬勃發展,為高校電子信息人才的培養帶來了強大的推動力,但是也為高層次電子信息人才的培養帶來了嚴峻的挑戰:

(1) 芯片設計與流片費用高,遠遠超出高校所能承受范圍;

(2) 在規模達數十萬邏輯門的數字系統設計中,已不可能采用分立元器件搭建完成;

(3) 受地域環境、儀器設備和安全性等因素的限制,學生不能深入生產一線進行實踐鍛煉。

因此,統籌虛擬技術、網絡技術、實驗室硬件資源,全面改革傳統的實驗教學模式與教學手段,構建虛實結合的實驗教學體系,是實驗教學改革的重點內容。我校數字電路虛擬仿真實驗教學依托國家級虛擬仿真實驗教學中心和國家級教學團隊,從學生的需求出發,通過在線教學管理平臺,遠程調用云端服務器上的工程仿真軟件,完成數字電路虛擬仿真實驗教學[1-2]。

1 數字電路虛擬仿真實驗內容

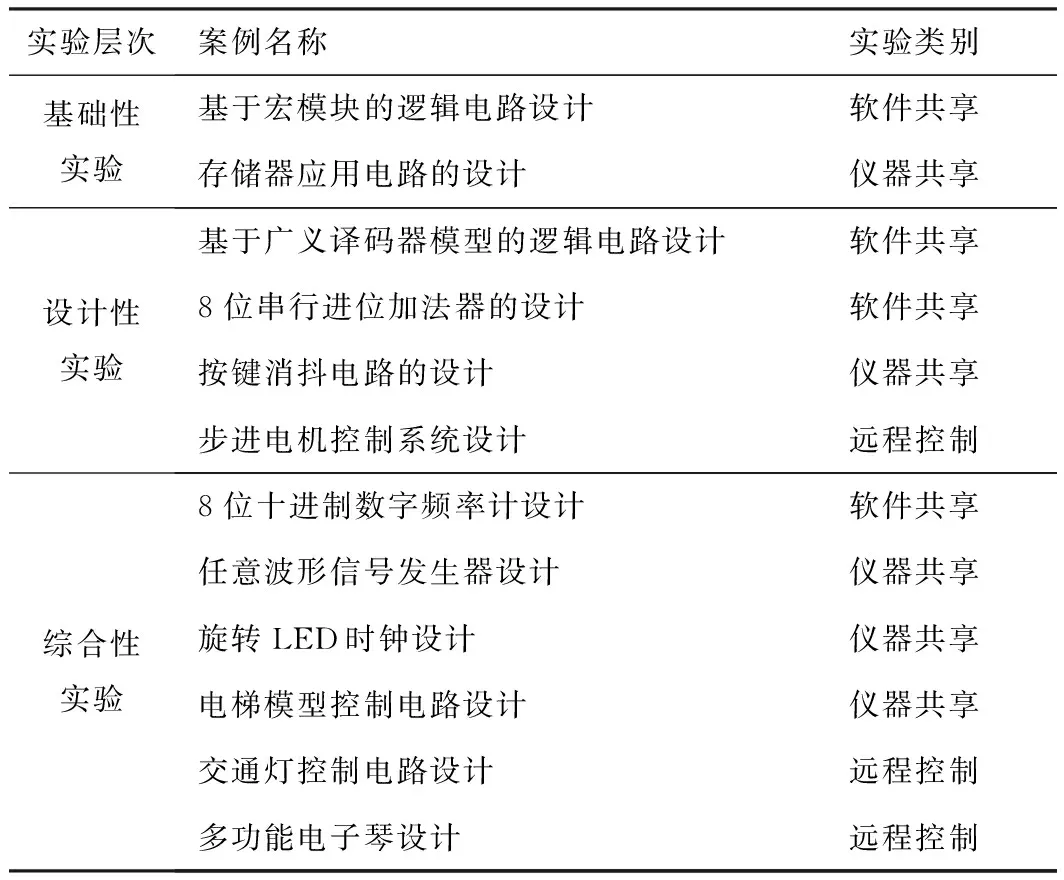

如表1所示,數字電路虛擬仿真實驗由基礎性實驗、設計性實驗和綜合性實驗3個層次,并且包含軟件共享、儀器共享和遠程控制3大類共12個實驗案例組成。

表1 數字電路虛擬仿真實驗案例

基礎性虛擬仿真實驗注重軟件參數的設置和電路參數的優化設計,注重基本實驗知識、方法和技能的教學與訓練,注重工程、分析和實踐等基礎能力的培養。

設計性虛擬仿真實驗是通過介紹典型實驗案例的設計思路和設計方法,給出實驗要求,讓學生去探索設計性實驗的方法。

綜合性虛擬仿真實驗是通過大量有創意的項目訓練,激勵學生參加較為復雜的數字電子技術課題,通過實驗培養學生的創新意識和創新能力[4]。

實驗內容先易后難、由淺入深,逐步提升實驗設計的廣度和深度。通過基礎性實驗—設計性實驗—綜合性實驗3階段遞進式實驗教學,激發學生的學習興趣、增強學生的創新創造能力[3]。

2 任意波形信號發生器設計

信號發生器是提供各種頻率、波形和輸出各類電測試信號的設備。在有限的教學課時內和采用傳統的分立元件,很難完成信號發生器的設計實驗,即使勉強完成,其精度和穩定性也難以保證。使用DDS(direct digital synthesizer)技術和FPGA(field-programmable gate array)實驗教學平臺,可以比較容易地設計出任意波形的信號發生器,且頻率穩定、精度高,解決了將復雜數字系統應用到實際教學中所面臨的難題[5]。

2.1 實驗任務

(1) 設計一個簡易正弦信號發生器,輸出頻率為時鐘頻率的1/256;

(2) 設計一個包含正弦波、三角波、方波等任意波形信號發生器,輸出頻率可調;

(3) 設計一個李薩如圖信號發生器,并觀察不同頻率和相位成簡單整數比的李薩如圖形。

2.2 實驗原理

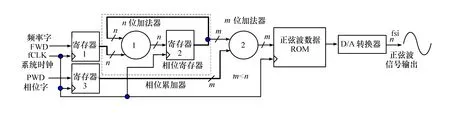

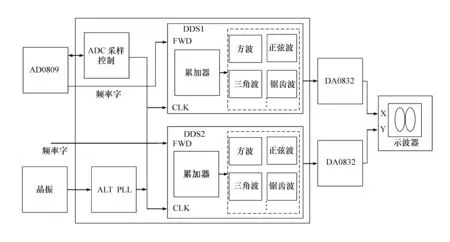

DDS信號發生器由加法器、寄存器、正弦波形數據存儲器和DAC轉換器4個模塊構成。在電路仿真設計過程中可以采用多種不同的方法實現,其原理如圖1所示。

圖1 DDS信號發生器原理圖

對于加法器,既可以調用門電路設計,也可以采用宏模塊設計。寄存器模塊主要用來存放數據,既可以使用宏模塊LPM_FF,也可以使用D觸發器相連而成。寄存器模塊與加法器組成一個相位累加器。波形數據存儲器可由LPM的ROM:1-PORT構成[6]。

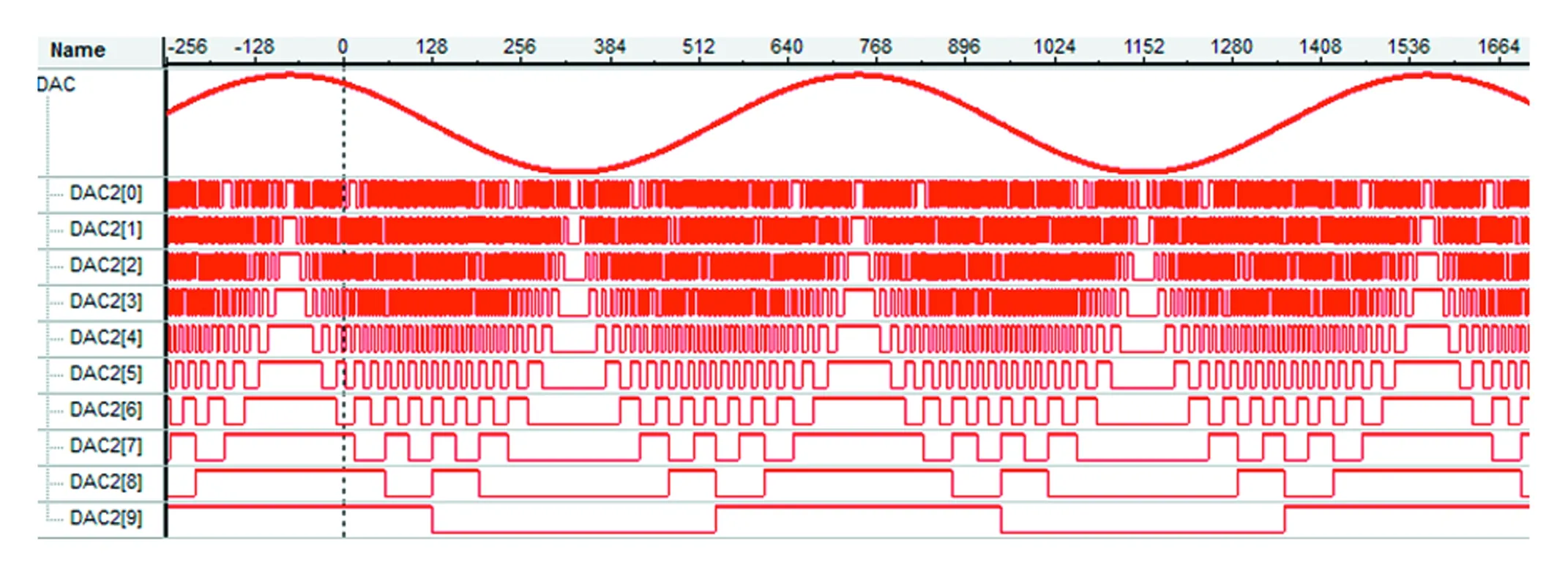

完成DDS信號發生器設計,設置其為頂層電路,并進行全局編譯;結合FPGA實驗教學平臺進行波形觀察。如圖2所示,通過嵌入式邏輯分析儀文件,對DDS輸出波形的數據進行采樣和監控。

采樣控制狀態機電路由狀態譯碼器、控制譯碼器、狀態寄存器和鎖存器構成。狀態譯碼器根據現態編碼和來自ADC的轉換狀態信息決定狀態的走向;控制譯碼器負責向ADC輸出控制信號;狀態寄存器由D觸發器組成[7]。如圖3所示,基于DDS信號發生器、采樣控制模塊和鎖相環模塊進一步實現李薩如圖信號發生器設計。

結合FPGA實驗教學平臺,將數據下載燒錄到FPGA芯片。通過示波器,觀察分析不同頻率和相位成簡單整數比的李薩如圖形,體會和理解李薩如信號的意義和應用。

圖2 嵌入式邏輯分析儀測試波形截屏圖

圖3 李薩如圖信號發生器系統框圖

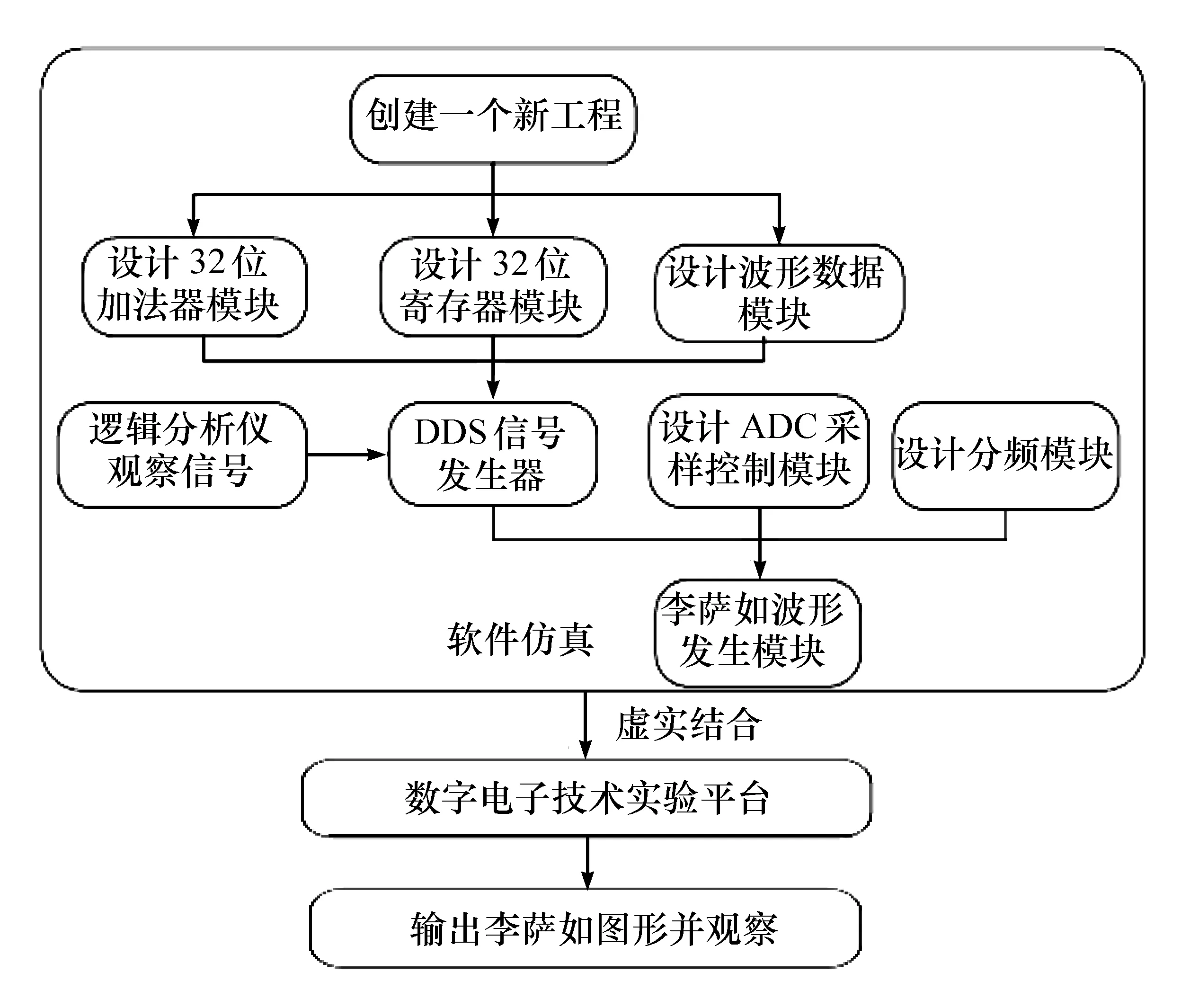

2.3 實驗步驟

任意波形信號發生器設計實驗教學為10課時,分為12個操作步驟,實驗操作流程如圖4所示。

圖4 任意波形信號發生器實驗操作流程圖

實驗采用工程仿真軟件Quartus Ⅱ,首先完成簡易正弦信號發生器設計;再完成包含正弦波、三角波、方波、鋸齒波等任意波形信號發生器的設計;最后完成一個各種頻率和相位成簡單整數比的李薩如圖形設計。實驗設計由淺到深,在有限的實驗教學課時內完成復雜數字系統的設計[8]。在電路功能設計中,設計方法具有多樣性,可用原理圖、硬件描述語言、宏模塊等多種方法完成實驗設計。在此基礎上,學生可以根據學習興趣進行實驗功能拓展:擴展設計輸出的信號波形具有調幅功能,用VGA顯示觀察輸出的各類信號波形,用液晶顯示輸出頻率的大小等。

2.4 實驗要求

數字電路虛擬仿真實驗教學通過教師的啟迪,要求學生自尋實驗設計技術及其創新的途徑[9],并按照實驗原理和實驗步驟進行實驗設計,完成實驗后在線提交實驗報告。報告內容包含摘要、引言、系統總體設計、電路原理設計及分析、時序仿真波形、電路優化方案、實驗總結等。

3 實驗教學方法及考核要求

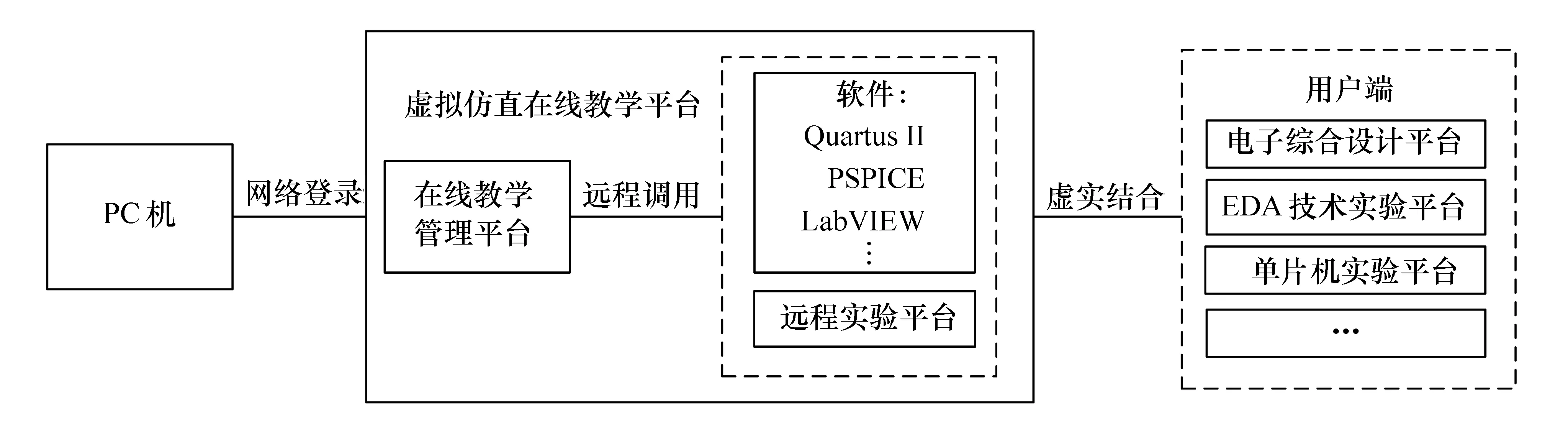

數字電路實驗課程借助國家級虛擬仿真實驗教學中心在線教學平臺,只需使用具有上網功能的電腦,即可通過網絡遠程共享實驗資源,進行虛擬仿真實驗設計和在線提交實驗結果。虛擬仿真實驗在提高實驗的靈活性的同時,大大節省了實驗成本。虛擬仿真實驗在線教學流程如圖5所示。

圖5 虛擬仿真實驗在線教學流程圖

教學方法的改革旨在調動學生對科學實驗的興趣,培養學生科學、嚴謹的實驗習慣,提高實驗教學效果。數字電路虛擬仿真實驗教學充分利用既有的“互聯網+”和教育信息技術,采用線上線下、課內課外、理論與實驗融合的混合教學方式。線上線下相結合,突破實驗的時空限制,增加師生、生生互動[10];理論與實驗相融合,將有針對性地提高學生學以致用的能力。

實驗教學考核注重實驗的過程,不但注重學生撰寫實驗報告的質量,也注重學生在實驗中的積極性、團隊合作意識和工程創新能力。在過程性考核方面,基礎性實驗、設計性實驗和綜合性實驗考核方式不同。基礎性實驗、設計性實驗主要通過課前預習、課堂操作、實驗報告等方面進行考核;綜合性實驗需要經過開題審核、階段性檢查、項目驗收答辯等環節,根據學生的表現、團隊配合以及學生提交的仿真結果、實物、報告及答辯的情況進行考核。在整個項目實施過程中,引導學生充分關注實驗成本、制作工藝、操作行為規范、實驗安全和環境、職業倫理等問題。如果學生在某方面表現突出,可以獲得額外加分;而如有不合理、不規范的操作,則會被及時警示、誡勉談話或單獨扣分。

數字電路虛擬仿真實驗教學評分比例如下:

(1) 基礎性實驗和設計性實驗成績占30%,綜合性實驗成績占70%;

(2) 基礎性實驗和設計性實驗=20%視頻觀看+20%預習測試+40%課堂操作+20%實驗報告;

(3) 綜合性實驗成績=40%驗收+15%提問+30%報告+10%創新性得分+5%實驗行為規范。

4 結語

本實驗教學項目已成功應用于我校數字電路虛擬仿真實驗教學,并表現出以下優點:

(1) 借助虛擬仿真中心在線教學平臺,突破了時間和空間的限制,達到“處處能學,時時可學”的泛在學習,切實提升了實驗教學效果[11];

(2) 通過數字電路虛擬仿真實驗設計復雜數字系統,培養了學生科學研究、系統設計、工程實踐的綜合能力;采用工程通用仿真軟件進行電路仿真設計,無縫對接行業需求;

(3) 發揮科研的支撐與引領作用,將教師和研究生的科研成果、教研課題、學生科技創新成果引入實驗教學,從科研項目和解決工程問題出發,豐富實驗教學內容,拓展了實驗項目的深度和廣度[12]。