基于FPGA的立方星可重構星載處理系統研究

, ,

(西北工業大學 精確制導與控制研究所,西安 710072)

0 引言

立方星(CubeSat)的概念最早由加州理工大學San Luis Obispo教授和斯坦福大學Bob Twiggs教授共同提出并制定了立方星的相關標準[1]。該標準以一個邊長為10 cm的正方體作為一個標準單元,稱之為“1U”立方星。在此基礎上,立方星以該標準單元進行擴展,可增大衛星的體積和功能。其理念是通過標準化設計,減少衛星的研發制造成本。

但立方星屬于微納衛星的范疇,相比于大衛星,其體積、功耗與成本均存在限制。如何在有限的體積、功耗與成本下,提高立方星星載處理系統的可靠性是國內外學者近期研究的熱點[2-3]。與此同時,大容量可重構FPGA (Field Programmable Gate Array) 的出現,使得可重構計算機成為了可能。可重構星載計算機能夠在立方星部分部件出現故障時,自主地改變自身的功能,使立方星能夠按原定性能指標或比原性能指標略低 (但可接受) 的情況下安全地完成任務。這樣就避免了固定硬件結構的立方星系統一旦發生硬件損傷,將導致任務失敗的結局,從而提高了立方星的可靠性。

文獻[4]介紹了2007年德國斯圖加特大學小衛星計劃的第一顆微小衛星——Flying Laptop,該衛星采用了基于FPGA的可重構計算技術來設計星載計算機。為了解決系統容錯以及抗輻射問題,系統設計了4個相同且相互獨立的節點。但考慮到功耗與體積等因素,該體系很難應用于立方星上。文獻[5]給出了用于立方星上的低成本高可靠性星載計算機的方案,文獻使用ATmega128作為星務處理器,而使用Spartan-6的FPGA作為載荷處理器。但該文僅僅只對使用FPGA的方案進行了討論,并未對FPGA如何進行具體的在軌重構進行研究。文獻[6]采用Xilinx的FPGA開發板利用模糊理論進行姿態控制算法研究,并進行了硬件在回路仿真,但該設計并未進行在軌試驗。本文將綜合考慮立方星的質量、功耗與體積等限制因素,使得立方星具有一定的重構能力,從而提高立方星星載處理系統的可靠性,并最終通過實際在軌測試,驗證了設計的正確性和可行性。

本文首先針對立方星存在的質量、體積與功耗等限制因素,在充分吸收了國內外微小衛星星載計算的設計研制經驗基礎上,給出了基于FPGA的立方星可重構星載處理系統的基本架構。在此基礎上,針對可重構星載處理系統中的一些關鍵技術進行了詳細的設計。最后針對各關鍵技術逐一進行了測試與驗證,并給出了實際在軌測試的結果。

1 系統結構及原理

為了使得立方星星載處理系統具有可重構性,同時滿足立方星的設計標準,本文基于FPGA進行了立方星可重構星載處理系統的設計。該設計充分吸收了國內外立方星星載計算機的設計研制經驗[7-9],并對星載計算機的可重構策略、在線重構、系統同步等功能進行設計。這樣使得整個星載處理系統在具有在線重構功能的同時、也具有體積小、集成度高以及低功耗等特點,能夠滿足一般立方星的應用需要。

所設計的星載處理系統的硬件結構圖如圖1所示。由圖中可以看出,該硬件結構由一片基于SRAM架構的FPGA與一片基于Flash架構的FPGA組成。其中,基于SRAM架構的FPGA中集成了兩個軟核處理器CPU1與CPU2,基于Flash架構的FPGA負責系統的表決控制功能。兩個軟核處理器分別擁有獨立的F-RAM,但共享同一個Flash存儲器。CPU1與CPU2同時從表決控制電路獲取輸入數據,經過運算后回送至表決控制電路。最終,由表決控制電路對結果進行同步和表決,并對外部輸出的結果。下面對該系統中核心部件的硬件設計進行詳述。

圖1 星載處理平臺總體結構

2 系統硬件設計

2.1 處理器設計

其核心處理模塊采用Altera公司基于SRAM架構的Cyclone V系統。與前幾代產品相比,該系列FPGA總功耗降低了40%,并具有高效的邏輯集成功能。正常工作情況下,在一塊FPGA中設計雙核處理系統,并為每一個處理器分別單獨配置SD卡與F-RAM用于任務數據存儲與數據內存,而兩個處理器共用同一塊Flash以減小功耗。

另外,采用基于Flash架構的ProASIC3芯片作為核心的表決控制系統。該芯片對于空間復雜環境下高能粒子的影響具有很好的免疫能力。在系統上電時無需額外配置芯片,增加了系統的安全性和穩定性,是真正的單芯片解決方案。上電即運行的特點,使得器件可以迅速執行重要的系統初始化任務。

ProASIC3作為與外界的接口,主要功能包括從外界總線獲取數據、對FPGA的計算結果進行表決、將最終結果輸出至外部數據總線、根據FPGA的工作情況對其進行重構、控制電源模塊進行重新上電等。在Altera的FPGA中設計雙核處理器,在正常工作時,雙核CPU1與CPU2均處于工作狀態,并各自產生對應的心跳信號。

2.2 電源設計

電源模塊實現電壓轉換、過流保護以及輸出使能等功能。為了降低功耗并防止FPGA配置芯片中的配置代碼不被高能粒子打翻,ProASIC3通過使能引腳來控制Cyclone V系統的配置過程。當Cyclone V的配置過程結束后,ProASIC3拉低使能引腳,停止對配置芯片供電。當需要重新配置Cyclone V時,使能電源芯片,使其正常為配置芯片供電。

2.3 存儲設計

存儲單元由鐵電存儲器F-RAM、SD卡以及Flash存儲器組成。Flash存儲器主要存儲運行于FPGA上的軟件程序。F-RAM存儲器用于存儲程序運行過程中的程序和數據。SD卡用于存儲立方星飛行過程中的任務數據。其中,每一個處理器分別單獨使用各自的SD卡與F-RAM,而兩個處理器共用同一塊Flash以減小功耗。

3 軟件實現

用于立方星的可重構星載處理系統,受到體積、功耗的限制,既不能過于復雜,又必須保證一定的可靠性。因此,可重構星載處理系統選擇雙模冗余的方案。對于雙模冗余的硬件結構,經常采用的容錯控制策略有熱備份、冷備份、溫備份以及互備援這幾種形式,文獻[10]對這幾種備份形式的優缺點進行了分析。下面對該系統中所采用的關鍵技術進行詳細設計。

3.1 可重構策略設計

為了減輕ProASIC3在表決切換等功能上的負擔,選取溫備份的容錯控制策略,ProASIC3僅進行數據輸入與輸出管理。在Cyclone V FPGA中設計的雙核主機CPU1與從機CPU2,具有相同的功能。若CPU1作為主機執行全部的星載處理程序,則從機CPU2同樣也對輸入的數據進行運算,但不輸出。由于主機與從機具有同樣的數據輸入來源,則在正常情況下,兩者的計算結果應該是相同的。若主機出現故障,則ProASIC3按照圖 2所示的流程進行重構。

圖2 星載處理平臺可重構策略流程圖

當ProASIC3處理器判斷主機出現故障時,由于從機也在執行相同的任務,因此主機可以不與從機進行任何形式的通信,只需要ProASIC3選擇輸出從機的計算結果即可。這種方式減少了主機與從機額外的通信開銷,保障了主機在出現故障時,能夠在一個控制周期內實現故障機的切換。如果此后從機又出現故障,則ProASIC3控制Cyclone V FPGA進行在線重構。如果在線重構后系統仍不能正常運行,則ProASIC3控制電源模塊進行斷電重啟,以避免單粒子閂鎖所導致電路電流過大的問題。如果斷電重啟仍無法使系統正常運行,在多次出現此故障后,ProASIC3將控制電源模塊斷電,等待地面的控制指令。對于該流程中所涉及到的在線重構、數據同步等技術的具體實現方式闡述如下。

3.2 在線重構

在線重構技術主要解決由單粒子翻轉等輻射效應引起的瞬態故障,當Cyclone V FPGA處理系統出現故障時,ProASIC3發送重構指令,開始在線重構過程。

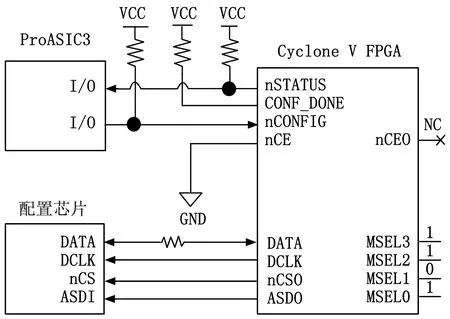

在線重構是對FPGA所有內置的邏輯單元LE(Logic Element)進行重配置的過程,FPGA的通用配置電路如圖3所示,重構過程可以通過拉低配置引腳nCONFIG實現。

圖3 在線重構配置電路

在需要進行在線重構時,ProASIC3必須使得nCONFIG管腳處于低電平至少500 ns以上。nCONFIG拉低時,FPGA器件被復位,同時也拉低nSTATUS和CONF_DONE引腳,此時FPGA所有的I/O管腳均處于三態狀態。當nCONFIG返回到邏輯高電平并且由FPGA器件釋放nSTATUS時,重構開始運行。當nCONFIG返回到邏輯高電平并且由FPGA器件釋放nSTATUS時,重構開始運行。如果在重構過程中出現錯誤,FPGA將使nSTATUS信號置為低電平,表明數據幀錯誤。同時CONF_DONE信號也會保持低電平。通過ProASIC3監控nSTATUS錯誤時的低電平,當三次重構后依然報錯,表明重構無法修復此故障,則需要斷電重啟。

3.3 系統同步

雖然通過重構策略提高了系統的可靠性,但是系統將面臨如何實現各個模塊之間協調工作的問題。在多機重構系統中,同步是整個系統的核心。數據的匹配或者表決都必須基于同步信號,否則匹配或表決就沒有意義。

本系統采用任務級同步的方法,任務級同步技術使各處理器執行相同的計算,計算完成時進行同步比較。本系統的同步主要由以ProASIC3為主芯片的處理系統作為管理器來進行。每一周期內的一次輸入和輸出過程可以定義為一個任務。在每次控制周期內,隨著系統的運行,ProASIC3按照如圖 4所示的流程圖進行數據的同步。

圖4 任務級同步的實現方法

在每一周期開始時,ProASIC3啟動定時器,接收各敏感器數據并發送給Cyclone V FPGA用于計算,隨后ProASIC3循環等待Cyclone V FPGA中的雙核處理器返回計算結果。如果在定時器定時結束之前,Cyclone V FPGA中的兩個處理器均能正常返回結果,則等待定時器計時結束后進入下一個控制周期。如果出現有處理器未返回計算結果的情況,則按照圖 2所示的策略進行相應的操作,并對系統狀態進行記錄。

4 系統測試驗證與分析

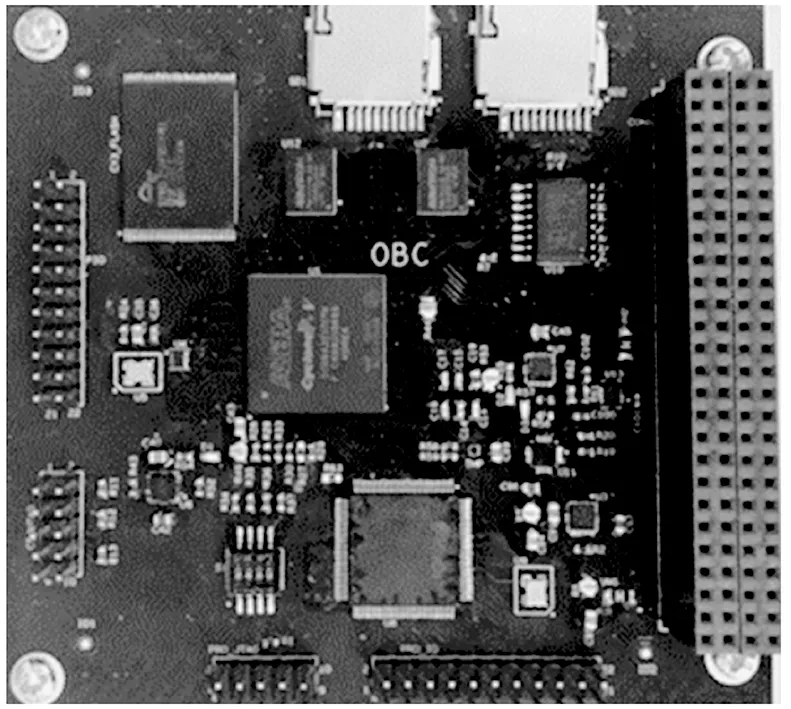

最終集成的星載處理系統實物如圖5所示。圖中,中間的芯片即為基于SRAM架構的Cyclone V FPGA,下部的芯片為基于Flash架構的ProASIC3 FPGA,左上部分的芯片為雙核處理器共享的Flash存儲器。基于該星載處理系統硬件平臺,針對各關鍵技術進行了實驗測試與驗證分析。

圖5 星載處理系統實物圖

4.1 在線重構技術測試

為了單純對在線重構技術進行驗證,設計了ProASIC3周期性地對Cyclone V FPGA進行重構的測試用例。在Cyclone V FPGA內部設計了時鐘鎖相環PLL,執行對輸入時鐘進行分頻,并將結果輸出至FPGA的外部接口上。通過示波器采集到的ProASIC3周期性地對Cyclone V FPGA進行重構的過程如圖6所示。

圖6 在線重構技術測試結果

圖中有四組曲線A、B、C、D,其中A曲線為nCONFIG重構控制信號;B曲線為Cyclone V FPGA中PLL的輸出信號;C曲線為配置芯片向Cyclone V FPGA傳輸重構數據的DATA信號;D曲線是表示重構完成的CONFIG_DONE信號。從圖中可以看出ProASIC3周期性地對Cyclone V FPGA進行重構。nCONFIG信號平時為高電平,一旦被ProASIC3設置為低電平,首先Cyclone V FPGA中正常的PLL任務停止輸出,同時CONFIG_DONE變低,表示開始進行在線重構。這里為了便于展示,低電平持續了約100 ms,而實際使用時低電平只需要大于500 ns即可。當nCONFIG信號又回到高電平后,配置芯片通過DATA引腳向Cyclone V FPGA傳輸重構數據,當配置數據傳輸完成后,Cyclone V FPGA的PLL繼續正常輸出時鐘信號,完成了一次在線重構。經過約100 ms的時間后,nCONFIG信號再次被ProASIC3置低,進行下一次的在線重構。經過測試,所設計的星載處理系統能夠正確地進行在線重構。

4.2 同步技術測試

本平臺采用任務級的同步方式,ProASIC在每一個控制周期給Cyclone V FPGA提供同步脈沖,用于其中運算模塊的同步運算。圖7顯示了ProASIC每隔固定周期給雙核發出的脈沖信號。

圖7 同步脈沖信號

在同步脈沖的協調下,Cyclone V FPGA通過串口返回的計算結果也基本上是同步的,如圖8所示。

圖8 同步輸出的結果

圖中,上下兩條曲線分別為CPU1與CPU2各自串口的輸出曲線。從圖中可以看出,兩者的計算結果輸出相位差小于50 μs。考慮到衛星上的控制周期在毫秒量級,因此這樣的相位差是完全可以被ProASIC所接受的。這說明所設計的同步機制是可行有效的。

4.3 在軌實際測試

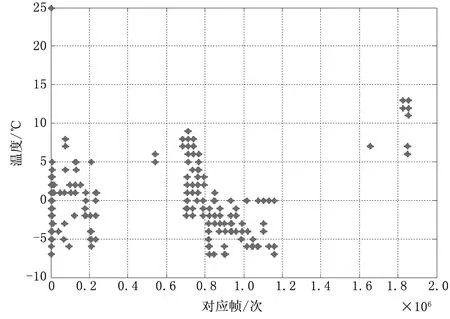

本文所設計的星載處理系統已經在世界首顆12 U立方星“翱翔之星”上得到了應用。該衛星于2016年6月25日發射,運行于距地面約300 km的軌道高度。在軌運行期間,該星載處理系統運行穩定。圖9顯示了“翱翔之星”星載處理系統FPGA的工作情況。

圖9 “翱翔之星”星載處理系統工作情況

由圖中可以看出,FPGA的狀態始終為0,表明FPGA在可測控弧段上均為正常,這說明在低軌的空間輻射對于FPGA的干擾影響較小。圖10顯示了星載處理系統的溫度變化情況。

圖10 “翱翔之星”星載處理系統溫度變化情況

由圖10可以看出,星載處理系統的溫度均處于-10~25 ℃之間,溫度比較適中。在整個衛星的生命周期內,星載處理系統運行穩定良好,證明了本設計方案的正確性和可行性。

5 結論

本文在對國內外微納衛星星載計算機設計特點進行分析的基礎上,提出了一種基于FPGA的立方星可重構星載處理系統。該系統采用基于SRAM型的FPGA作為核心處理模塊,利用較少功耗獲得較高的運算速度;同時采用基于Flash型的FPGA作為外部表決接口模塊,對基于SRAM型的FPGA進行表決和控制。當基于SRAM型FPGA出現問題時,基于Flash型的FPGA能夠對前者進行重構修復,從而提高了整個系統的可靠性。最終在硬件上的測試與在軌實測數據表明,本文所設計的立方星可重構星載處理系統是可靠和有效的,這對于今后設計適合于立方星使用的可重構處理系統提供了一些有益的參考。