基于EDA技術的汽車速度表設計

陳初俠 袁 濤 曾奧運 蔣光好

(巢湖學院機械與電子工程學院 安徽巢湖 238000)

近些年來,隨著我國國民經濟的不斷發展,人民的消費水平不斷提高,汽車數量也是逐年增長,隨之帶來的汽車安全問題也越受到人民的關注。速度作為汽車行駛過程中重要的指標參數,因此汽車速度表的設計也被要求更精確,更快速,更靈敏。

傳統的汽車速度表是利用變速器或分動器的輸出軸帶動儀表中指針顯示汽車速度,這種機械結構方式顯示出的速度會有較大的誤差。基于EDA技術設計的汽車速度表,以其價格便宜、安全可靠、使用方便等優點,而受到人們的普遍關注[1-3]。本文以現場可編程邏輯器件(FPGA)為設計載體,以硬件描述語言(VHDL)為主要表達方式,以QuartusⅡ開發軟件和ZY11EDA13BE開發系統為設計工具設計的汽車速度表[1-3],能夠實現速度的精確顯示和超速報警功能,完全滿足汽車速度表的設計要求。

一、汽車速度表的功能和整體結構

(一)汽車速度表的主要功能。這里所設計的汽車速度表具有以下功能:1.能顯示汽車的速度,單位是km/h;2.速度用數碼管顯示,且要精確到小數點后兩位;3.顯示的最高時速為360km/h,超過此速度會出現報警;4.速度采樣周期為10秒。

為了設計簡化,在設計過程中,假設車輪每轉一圈,有一傳感脈沖,每轉一圈代表1m的距離。

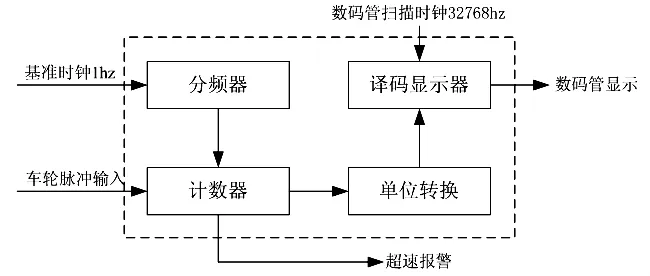

(二)汽車速度表的整體結構。汽車速度表的整體結構如圖1所示,其中虛線框內部是需要設計的部分,它包括分頻器模塊、計數器模塊、單位轉換模塊、譯碼顯示器模塊。

圖1 汽車速度表的整體結構圖

二、汽車速度表的設計

汽車速度表的設計是采用層次化的設計方法來進行,分底層各模塊電路的設計和頂層電路的設計。

(一)底層電路的設計。底層電路有四個電路模塊,分別是分頻器電路模塊、計數器電路模塊、單位轉換電路模塊和數碼管譯碼顯示電路模塊,他們都通過VHDL語言進行設計。

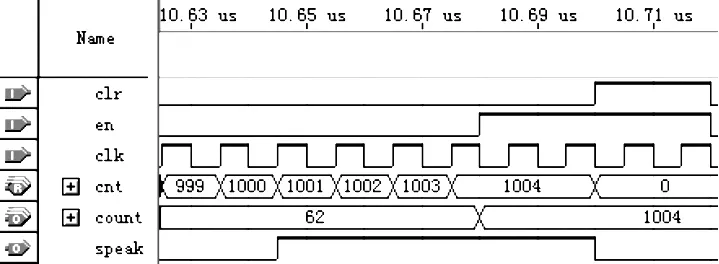

1.分頻器電路模塊。該模塊的功能是由基準時鐘分頻出兩個周期信號,其仿真波形如圖2所示。clk_1hz為頻率為1hz的基準時鐘,clr和en為被分頻出的周期為12秒的信號,他們的占空比不一致,都為后面的計數器電路模塊服務。

圖2 分頻器電路模塊仿真波形

2.計數器電路模塊。該模塊的功能是對輸入的車輪脈沖個數進行計數,其仿真波形如圖3所示。clk為傳感器感應的車輪脈沖信號;count為10秒鐘內對車輪脈沖個數的計數結果;speak為脈沖計數超過一定值時(比如1000)的報警信號,高電平有效。

圖3 計數器電路模塊仿真波形

當en=“0”時,計數器進行計數工作;當en為上升沿時,計數結束并把計數結果傳輸給輸出信號count。由圖2可知en的周期為12秒,處于“0”的時間剛好為10秒,所以計數是在10秒鐘內對車輪的脈沖個數進行計數。當clr=“1”時,對計數結果進行清零操作;當clr=“1”時,不對計數結果進行清零。

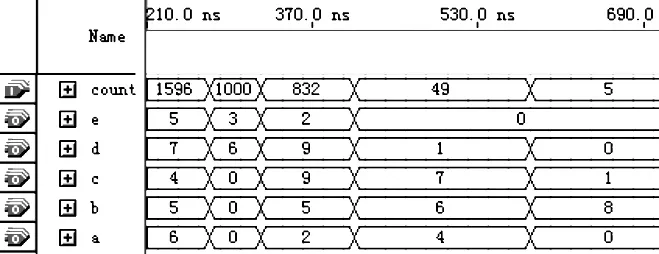

3.單位轉換電路模塊。該模塊的功能是進行單位轉換,把m/s轉換成km/h,其仿真波形如圖4所示。例如,當在10秒鐘內的計數結果為832時(一個脈沖為1m),即10秒鐘內車輪跑了832m,速度為83.2m/s。轉換為km/h后其數值應為83.2×3.6=299.52,從波形圖可以看出,理論值與實驗結果剛好吻合。

圖4 單位轉換電路模塊仿真波形

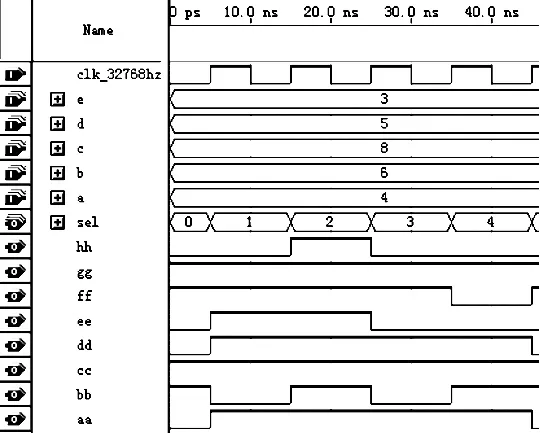

4.數碼管譯碼顯示電路模塊。該模塊的功能是把轉換為km/h的速度值通過數碼管顯示出來,其仿真波形如圖5所示。這里采用動態的方式進行顯示,數碼管是“共陰極”結構。

輸入信號clk_32768hz是頻率為32768hz的掃描信號,即每秒鐘數碼管依次亮滅32768次。由于掃描頻率過高,人的視覺有暫留現象,所以看上去所有的數碼管都是一直亮著的。信號 e、d、c、b、a為速度值,圖示值為 358.64km/h。

輸出信號sel為數碼管掃描片選信號,當sel=“0”時,最右邊的數碼管點亮,此時應顯示“4”,以此類推,當 sel=“4”時,最左邊的數碼管點亮,此時應顯示“3”。gg、ff、ee、dd、cc、bb、aa為數碼管的 7段,hh為小數點。例如,要顯示“8.”,則片選信號 sel應等于“2”,hh、gg、ff、ee、dd、cc、bb、aa全部為高電平,由圖5可以看出,與實驗結果剛好吻合。

圖5 數碼管譯碼顯示電路模塊仿真波形

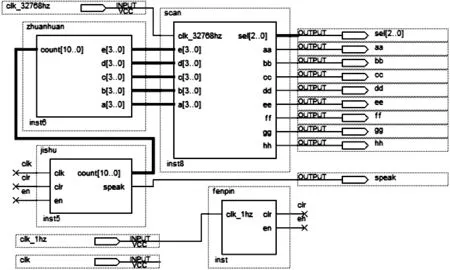

(二)頂層電路的設計。頂層電路設計采用原理圖輸入方式,通過調用生成的各底層電路模塊符號,并將他們做適當連接以實現頂層文件的設計[4],電路如圖6所示。

圖6 汽車速度

圖6中,clk_1hz為基準時鐘、clk為車輪脈沖信號、clk_32768hz為數碼管掃描時鐘信號;speak為超速報警信號,sel為數碼管掃描片選信號,aa、bb、cc、dd、ee、ff、gg、hh 為數碼管顯示輸出。

三、汽車速度表的硬件驗證

本設計選用湖北眾友科技實業股份有限公司生產的ZY11EDA13BE實驗箱作為硬件驗證平臺,同時選用Altera公司的EP1K30QC208-2作為主控芯片。該芯片是一種基于查找表結構的現場可編程邏輯器件,它的基本邏輯單元是可編程的查找表,能夠實現組合邏輯運算,并可用可編程寄存器實現時序邏輯運算[1-3]。因此,只要對汽車速度表頂層文件的輸入輸出引腳進行鎖定,然后重新編譯和下載,就可以進行汽車速度表的硬件驗證。

硬件驗證結果如圖 7 所示,圖(a)、(b)、(c)、(d)顯示的速度分別為 7.20km/h、57.60km/h、230.40km/h、460.80km/h,其中顯示速度為460.80km/h時,右下方出現一個紅色報警。實驗表明:所設計的汽車速度表精度到達小數點后兩位,并且當速度高于360km/h時會出現報警,基本實現了汽車速度表的全部功能。

圖7 汽車速度表的硬件實現

四、結語

本文采用EDA技術“自上而下”層次化設計方法設計汽車速度表,即從汽車速度表整體系統功能出發,將系統分解為各功能模塊,每個功能模塊分別由VHDL語言進行設計并通過仿真測試,生成元件符號以實現底層電路設計[4];頂層電路采用原理圖輸入方式進行,通過調用各底層電路模塊符號元件,并將他們做適當連接以實現頂層文件的設計。最終將設計好的頂層電路下載到EDA實驗箱上進行驗證,結果表明,本設計能夠實現所要求的全部功能。同時,底層電路采用VHDL語言進行設計,提高了系統可移植性,維護和升級也比較方便。另外核心芯片內部設計電路,減少器件使用數量縮減了系統體積,避免高密度復雜連線,提高了系統穩定性[4]。

參考文獻:

[1]劉凱,王紅航.出租車計費器的EDA設計與實現[J].電子元器件應用,2010(7):69-71.

[2]王紅航,張華斌.電子密碼鎖的EDA設計與實現[J].電子元器件應用,2009(6):35-37.

[3]劉凱,王紅航.電子搶答器的EDA設計與實現[J].電子元器件應用,2010(8):54-57.

[4]李響,何東鋼,李昕欣,等.出租車計價裝置分層次設計的優化研究[J].實驗室科學,2016,19(1):62-65.