基于ADF4350的鎖相環頻率合成器設計與實現*

夏江林,鄒傳云

0 引 言

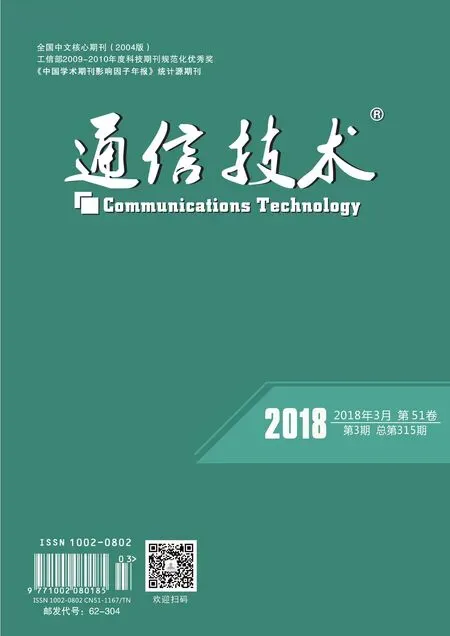

頻率合成技術是經過一系列處理后具有高穩定性和高準確度的標準參考頻率產生大量具有相同穩定性和準確性的離散信號,并且輸出信號的頻率可由數字信號控制[1]。鎖相環(PLL)是頻率合成器的核心組成部分,是許多電子產品的關鍵部件之一,可廣泛應用于工業、國防、軍事和民用等領域。鎖相環頻率合成器由PD(相位比較器)、LF(環路濾波器)和VCO(壓控振蕩器)組成[2],原理如圖1所示。

圖1 鎖相環頻率合成器的原理

圖1 中,fR為輸入信號的頻率,f0為輸出信號的頻率。PD用于比較兩個輸入信號fR和經N分頻的輸出信號f0。如果兩個輸入信號的頻率不一致,PD將產生一個低頻分量,使得VCO的輸出頻率通過LF變化[3]。LF的作用是產生誤差控制電壓來控制VCO的輸出頻率。由于負反饋的影響,這種變化會不斷使輸出信號f0經N分頻后的頻率和輸入信號的頻率fR一致。f0和fR的相位差保持在一個不變的范圍內。此時,PLL環路處于所謂的“鎖定”狀態[4]。最后,使輸出信號頻率為f0=N·fR。

本文設計了一種用單片機作為鎖相環芯片ADF4350的控制器,實現了輸出1 GHz的鎖相環頻率合成器。因為鎖相環芯片ADF4350集成了鑒相器、壓控振蕩器和N分頻器,所以本文的主要工作在于設計環路濾波器參數和調試ADF4350內部R0-R5寄存器的控制數值。鎖相環(PLL)頻率合成器。它的工作電壓一般選3.3 V,最大鑒相頻率為32 MHz,RF輸出功率為4~5 dBm。

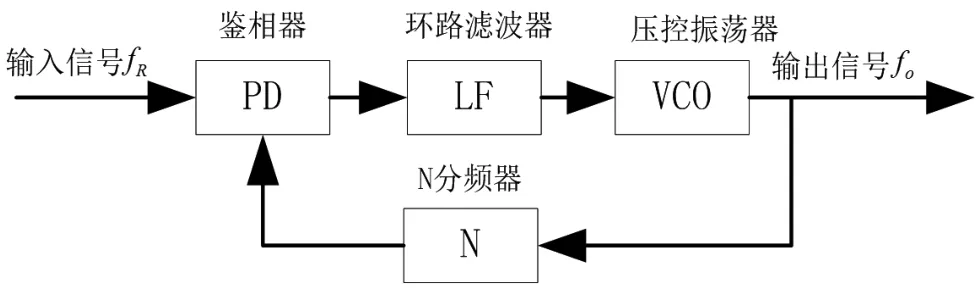

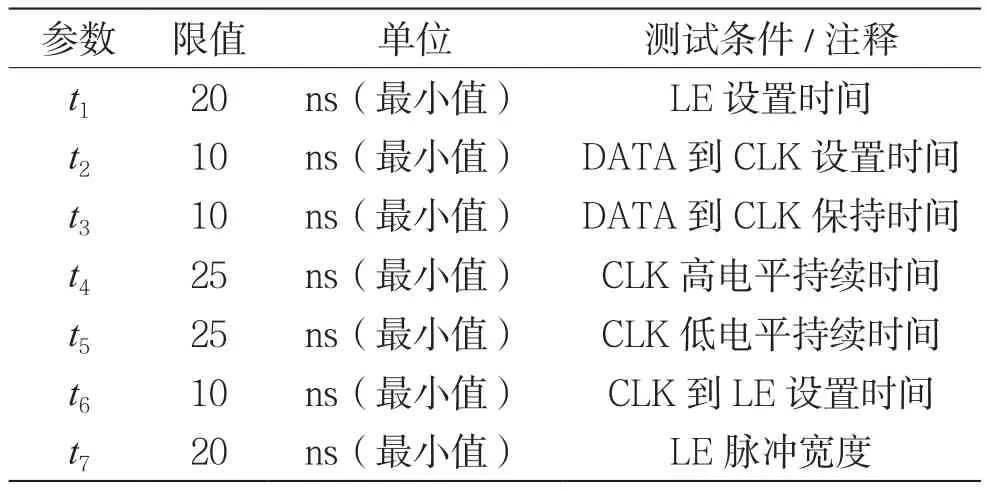

ADF4350的數字接口是與SPI兼容的串行接口,作用在于將數據寫入器件。CLK、DATA和LE則控制數據傳輸。在CLK從低電平到高電平時,將32位數據逐位寫入對應寄存器;當LE由低電平變為高電平時,數據被傳輸至對應的鎖存器[5]。ADF4350的時序特性如表1所示,時序圖如圖2所示。

1 鎖相環芯片ADF4350簡介

ADF4350是一款由ADI公司生產的集成低噪聲VCO的PLL,可以連續調諧137.5 MHz至4 400 MHz。ADF4350結合外部環路濾波器和外部基準頻率使用時,可以實現小數N分頻或整數N分頻

表1 時序特性

圖2 時序圖

2 鎖相頻率合成器在ADIsimPLL中的仿真設計

ADISimPLL用于輔助設計ADF4350外部電路,如圖3所示。ADISimPLL是ADI公司為其產品提供的PLL輔助設計軟件,適用于一切ADFxxx系列的鎖相環產品。在已知參考輸入頻率、輸出頻率、環路帶寬和相位裕度時,可以通過ADISimPLL輕松設計環路濾波器的各項參數。然后,根據實際情況選擇相對應的電阻和電容值,就可以實現對環路濾波器的設計。ADISimPLL同樣可以對鎖相頻率合成器系統各部分的相位噪聲進行分析[6]。

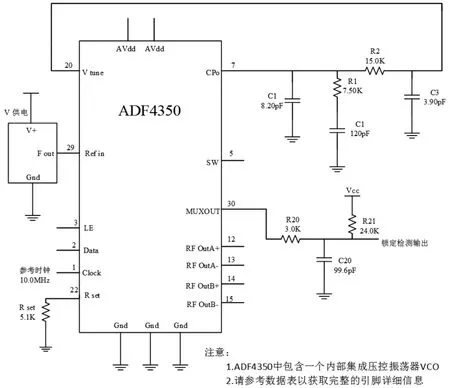

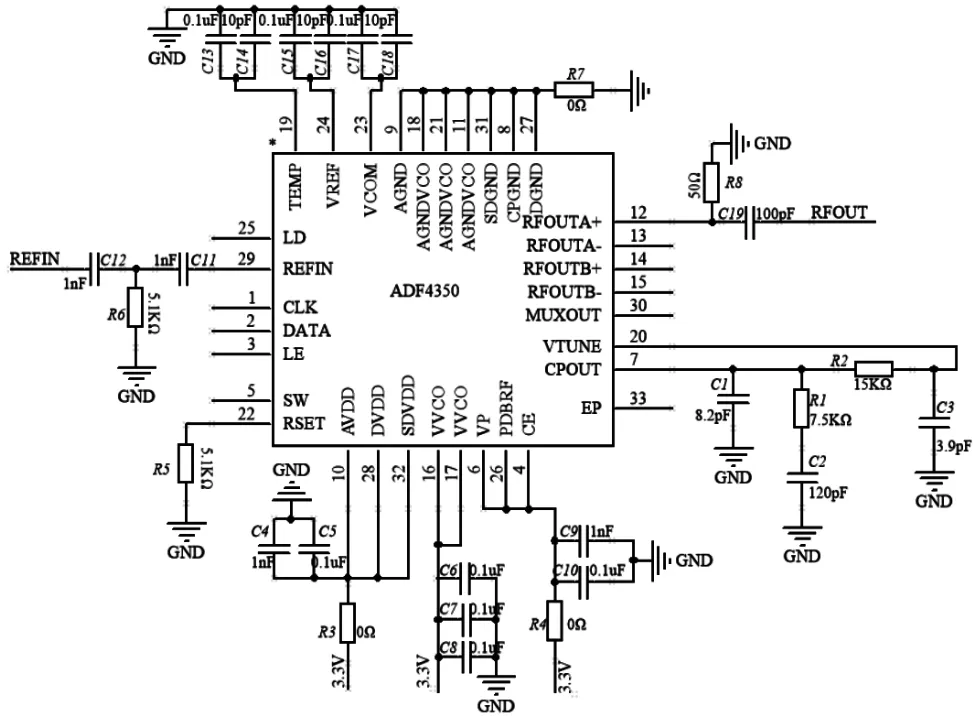

環路濾波器的設計是PLL頻率合成器設計中最重要的一個環節。合理的設計參數直接關系到頻率合成器輸出信號的雜散、相位噪聲、頻率穩定度、頻率轉換時間等諸多指標[4]。它的作用是濾除鑒相器產生的高頻信號。相對于有源濾波器,無源濾波器只使用RC低通濾波器,成本低,不像有源濾波器帶來噪聲和零點漂移。所以,本文采用三階無源低通濾波器作為PLL的環路濾波器。該濾波器電路結構簡單,噪聲低,穩定性高。圖3中,環路濾波器參數為:C1=8.2 pF,R1=7.5 kΩ,C2=120 pF,R2=15 kΩ,C3=3.9 pF。

為了實現鎖相環的快速鎖定,本文將環路帶寬設計為200 kHz。通過ADIsimPLL對設計的環路特性進行仿真,環路帶寬設置為200 kHz,輸出頻率為1.0 GHz,系統的開環增益特性如圖4所示。

圖3 ADF4350的外圍電路

圖4 系統的開環特性曲線

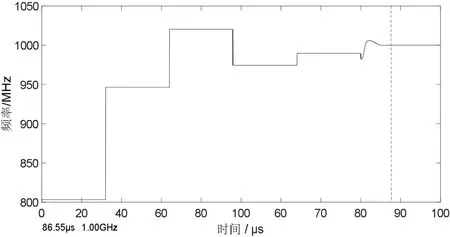

圖4 給出了系統開環傳遞函數的增益和相位曲線。在200 kHz處,對數增益為零,相位裕量在45°左右。當相位偏移為180°時,增益幅度約為-30 dB。可見,當對數增益為零時,相位裕度為正;當相位偏移為180°時,增益幅度為負,符合波特標準穩定條件,所以環路可以穩定[7]。同樣,可以通過ADIsimPLL獲得系統的輸出頻率特性,如圖5所示。在圖5中可以得到,系統輸出穩定即鎖定的時間為86.55 μs,滿足系統的設計要求,鎖定時間小于100 μs。

圖5 系統輸出頻率隨時間的變化

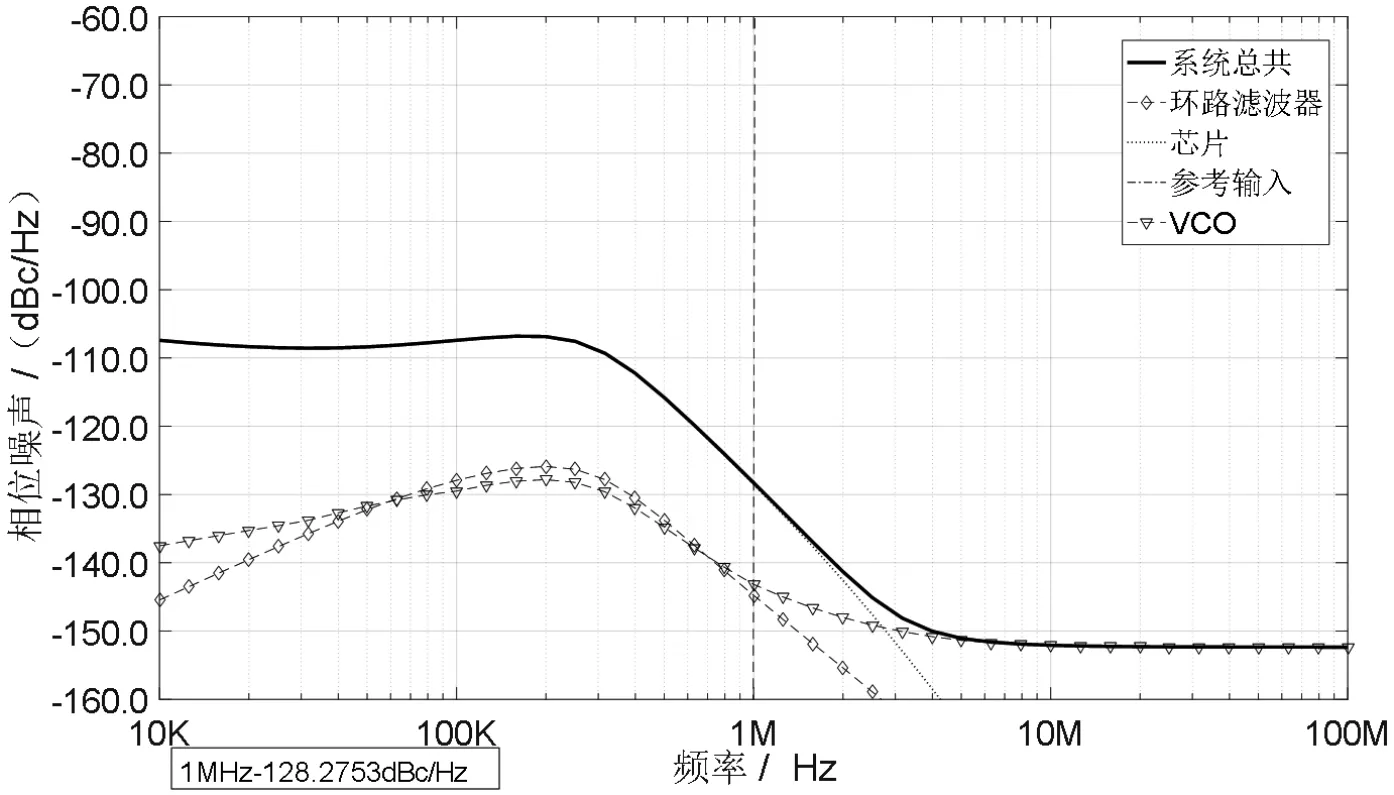

通過ADISimPLL同樣可獲得系統輸出1 GHz時的相位噪聲,如圖6所示。在圖6中可以清楚看到系統各部分對整個系統相位噪聲的貢獻。其中,Chip(芯片)和VCO是ADF4350芯片固有的特性,器件選擇后不能改變;Loop Filter(環路濾波器)和Ref(參考頻率)則可以通過設計和選擇來減少對系統相位噪聲的影響。從圖6可以看出,在1 MHz時,系統的相位噪聲約為-128.275 3 dBc/Hz@1 MHz。這個值為理論值,實際應用中由于存在電磁干擾,相位噪聲會高于理論值[8]。

圖6 1 GHz相位噪聲仿真結果

3 鎖相頻率合成器系統實現

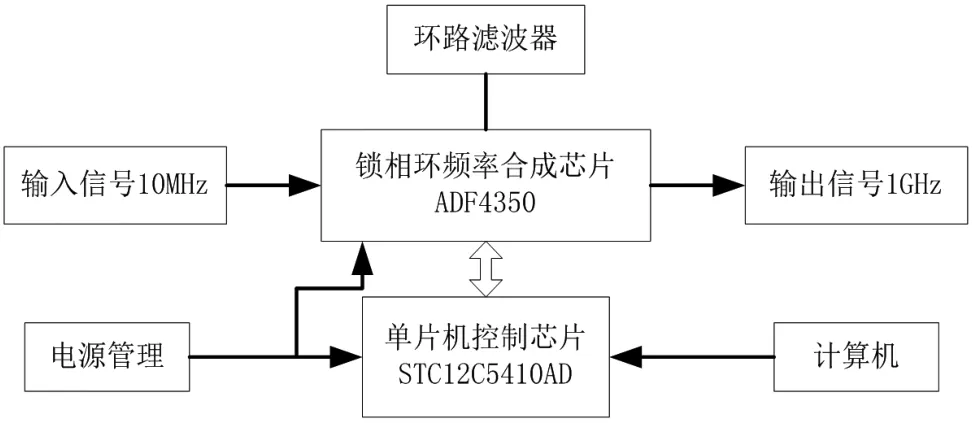

本系統的整體設計,如圖7所示。單片機芯片STC12C5410AD實現對整個系統的控制。單片機芯片通過計算機寫入相應的控制程序,從而控制鎖相環頻率合成芯片ADF4350對應的寄存器,完成對輸出頻率的控制。

圖7 鎖相環頻率合成器的整體設計

3.1 頻率合成器硬件電路實現

頻率合成器原理圖的核心部分,如圖8所示。原理圖中包含環路濾波電路、電源輸入電路和信號輸入輸出電路,并運用了大量去耦電容和旁路電容提高電路的抗干擾能力。鎖相環頻率合成芯片ADF4350中,CLK、DATA和LE控制數據的傳輸,分別與單片機控制芯片STC12C5410AD的P1^7~P1^5引腳相連。

如圖7所示,輸入信號10 MHz由外部的晶振或信號源提供,要求高穩定度和低雜散,為整個系統提供準確的參考頻率。單片機STC12C5410AD的作用是通過對ADF4350內部寄存器Register0~5的控制,實現對整個頻率合成器系統輸入和輸出的控制。另外,電源管理給鎖相環芯片ADF4350提供了3.3 V穩定的直流電壓,給單片機芯片STC12C5410AD提供了5.0 V穩定的直流電壓。環路濾波器的作用是濾除鑒相器產生的高頻信號,給后級輸入的電壓控制振蕩器(VCO)提供穩定的控制電壓。整個系統最后實現了輸出1 GHz的穩定信號。

圖8 頻率合成器原理

3.2 頻率合成器參數實現

對于整個頻率合成器系統而言,系統參數設計主要是確定ADF4350中各寄存器Register0~5的值。寄存器Register0~5中包含了鎖相環的主要參數,如參考輸入頻率、輸出頻率、鑒相器頻率、前置預分頻器、反饋分頻系數、環路濾波器的環路帶寬等。本文設計的鎖相環頻率合成器的輸出頻率為1 GHz,相位噪聲優于-100 dBc/Hz@100 kHz,雜散抑制優于-60 dBc,鎖定時間小于100 μs。可以用式(1)分析鎖相環頻率合成器系統的總體隨機相位噪聲[6]:

其中PNTOTAL為整個系統的相位噪聲,其值是一個負數;PNSYNTH是鎖相頻率合成器自身的歸一化帶內相位本底噪聲,典型值為-213 dBc/Hz;201g N是一個與分頻器N有關的相位噪聲增量,其中反饋分頻系數N可以在ADF4350的寄存器Register0中進行設置;101g fPFD是一個與鑒相器的鑒相頻率有關的相位噪聲增量,鑒相頻率可以在寄存器Register1中設置。由式(1)可知,鎖相環頻率合成器的相位噪聲主要由PNSYNTH、分頻器N和鑒相器頻率fPFD決定。而PNSYNTH是由芯片本身決定的一個固定值,可以當作常量處理[9]。所以,可以通過選擇較大的分頻器N和鑒相器頻率fPFD來降低整個系統的相位噪聲。本文最終確定采用鑒相頻率為10 MHz和分頻器N為400。同樣,可以根據式(2)、式(3)和式(4)來確定ADF4350中的其他參數。

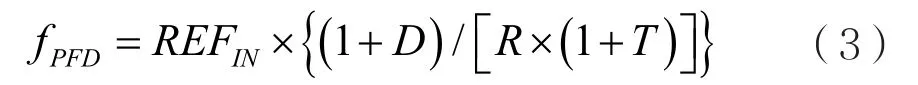

其中RFOUT是頻率合成器的輸出頻率,INT是整數分頻系數,FRAC是小數分頻系數,MOD是模數值,fPFD是頻率合成器的鑒相頻率,DVCO是頻率合成器VCO輸出頻率的分頻器值,可取1、2、4、8、16。

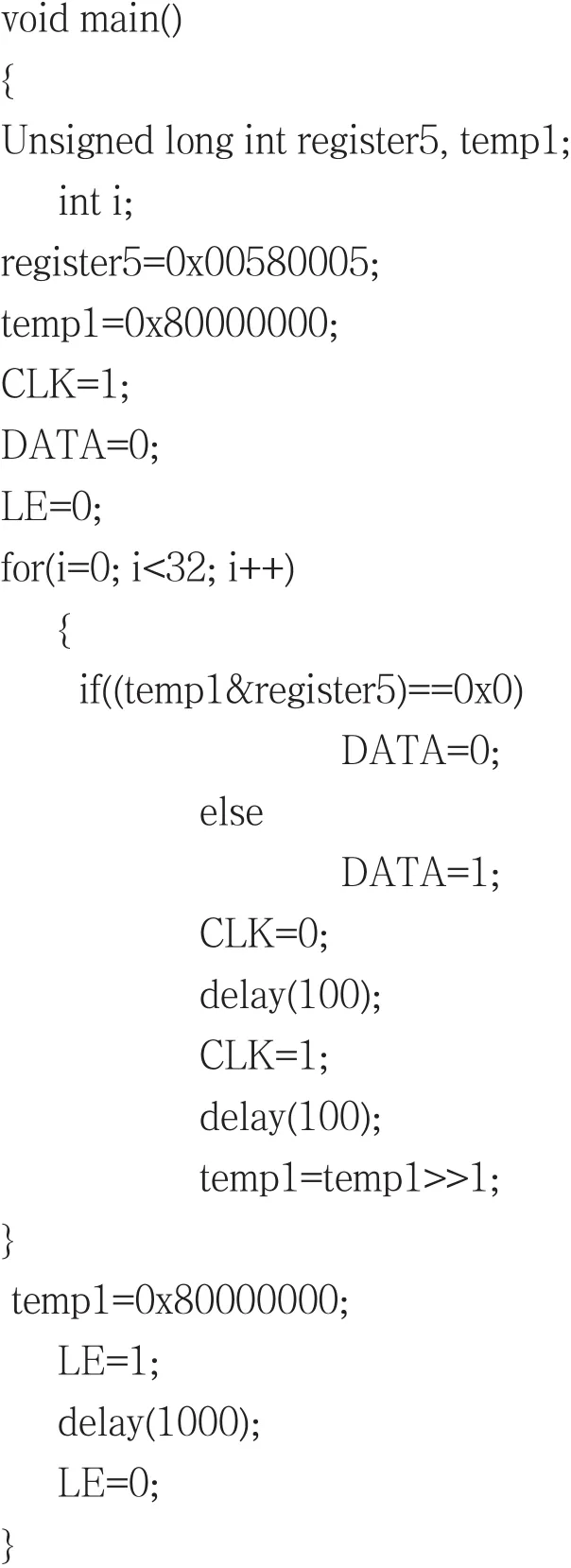

其中REFIN是鎖相頻率合成器的基準輸入頻率,D是REFIN倍頻器位(0或1),T是REFIN基準2分頻位(0或1),R是RF基準分分頻系數。

其中fRES是鎖相中VCO的輸出通道分辨率。

根據鎖相環系統的設計要求,最終確定各參數 為:INT=400、FARC=0、fPFD=10 MHz、DVCO=4、REFIN=10 MHz、D=0、T=0、R=1、fRES=800 kHz、MOD=12。根據上述參數值,結合ADF4350的datasheet資料,可決定R0~R5寄存器的值為:R0(0x00C80000)、R1(0x08008061)、R2(0x00004EC2)、R3(0x000004B3)、R4(0x00A6603C)、R5(0x00580005)。

3.3 頻率合成器控制程序實現

單片機STC12C5410AD芯片主要用來控制鎖相環頻率合成芯片ADF4350的內部寄存器配置和輸入輸出設置。ADF4350數字部分包括10位RF R計數器、16位RF N計數器、12位FRAC計數器和12位模數計數器。在時鐘CLK的上升沿時,數據輸入32位移位寄存器中,再在LE上升沿時從移位寄存器傳輸到6個鎖存器之一。其中,R0配置16位INT值和12位FRAC值,R1配置12位相位值和12位MOD值,R2配置10位R值和MUXOUT輸出參數,R3配置12位時鐘分頻器和其他參數,R4配置射頻輸出功率等參數,R5是鎖定檢測。ADF4350的寄存器序列的初始化順序為從R5到R0。根據ADF4350的時序特性,如表1、圖2所示,可以編寫出單片機STC12C5410AD的控制程序。由于篇幅有限,本文僅給出了控制寄存器R5的程序[10]。

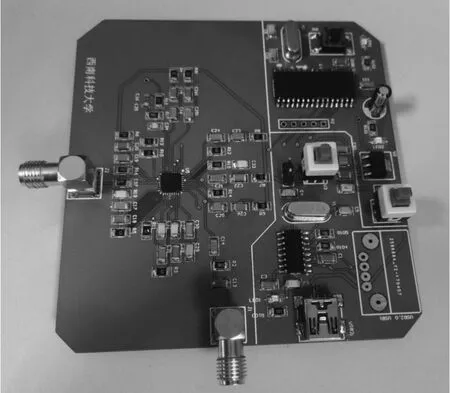

4 鎖相頻率合成器性能測試

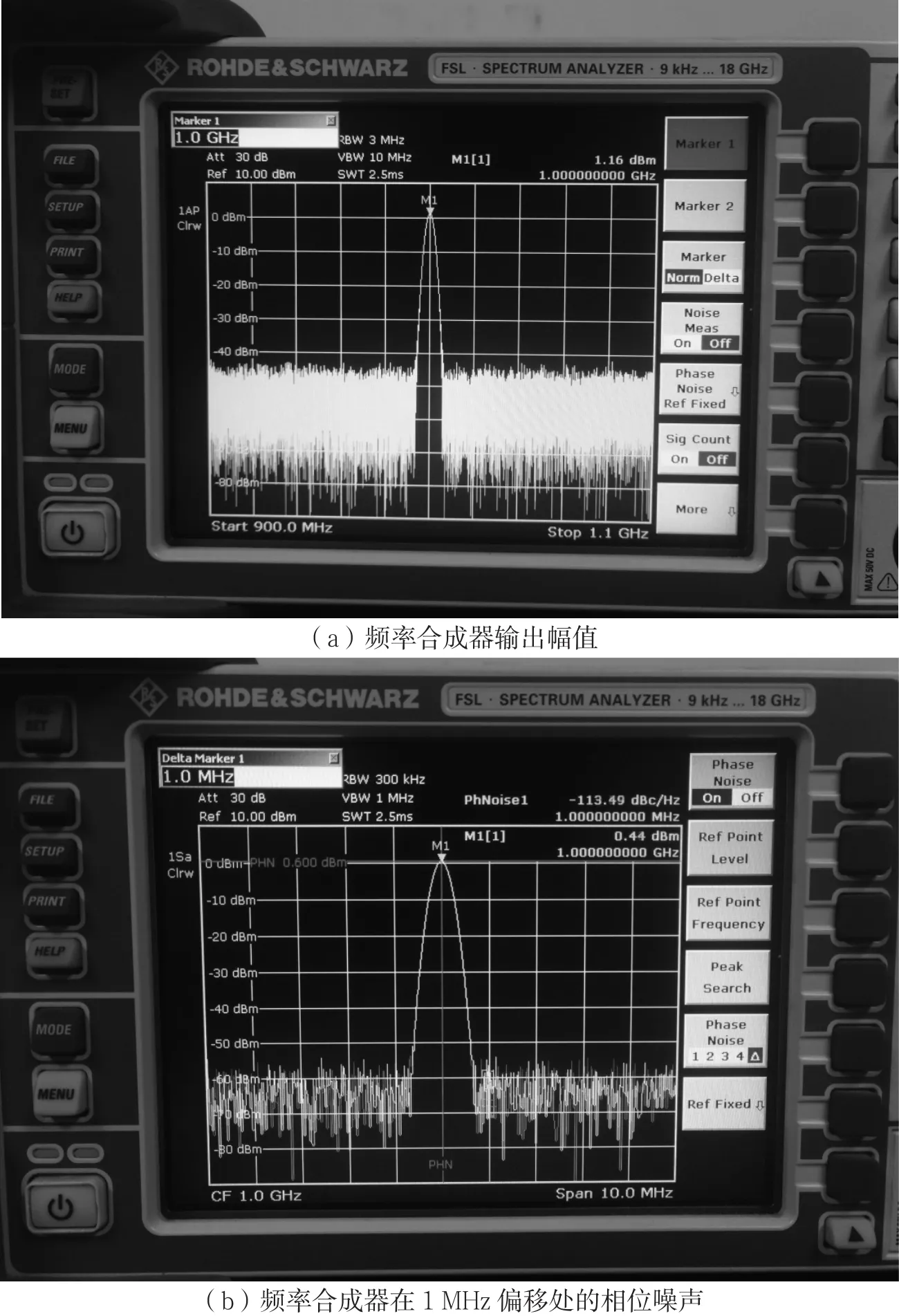

采用以上硬件電路設計,研制出輸出1 GHz的鎖相頻率合成器,實物照片如圖9所示。通過對單片機STC12C5410AD的合理編程,實現鎖相頻率合成器輸出1 GHz的穩定信號,并通過頻譜儀對頻率合成器的性能進行測試,結果如圖10所示。

圖9 頻率合成器的實物照片

在圖10(a)的測試中,頻率合成器穩定輸出1 GHz的信號,且輸出幅值達到1.16 dBm。測試相位噪聲時,將頻譜儀的RBW設為300 kHz,SPAN設為10 MHz,測得在1 MHz處的相位噪聲為-113.49 dBc/Hz,其圖像如圖10(b)所示。

5 結 語

本文介紹了運用ADF4350鎖相環芯片和單片機STC12C5410AD設計1 GHz頻率合成器的設計過程和設計方法,最終設計完成了大小為45 mm×45 mm、輸出幅度為1.16 dBm、相位噪聲為-113.49 dBc/Hz@1 MHz的高穩定度頻率合成器。實驗證明,該頻率合成器能很好地運用于本地振蕩器。

圖10 頻率合成器測試結果

[1] 萬天才.頻率合成器技術發展動態[J].微電子學,2004,34(04):366-370.WAN Tian-cai.Development of Frequency Synthesizer Technology[J].Microelectronics,2004,34(04):366-370.

[2] 李黨鋒.鎖相環頻率合成器的發展及應用[J].現代導航,2010(06):37-41.LI Dang-feng.Development and Application of the PLL Frequency Synthesizer[J].Modern Navigation,2010(06):37-41.

[3] 于為健,張娟.基于ADF4350的S頻段鎖相頻率合成器設計[J].電子科技,2013,26(11):69.YU Wei-jian,ZHANG Juan.Design and Implementation of S-band PLL Frequency Synthesizer Based on ADF4350[J].Electronics Technology,2013,26(11):69.

[4] 金玉琳,佘世剛,周毅等.鎖相環環路濾波器噪聲特性分析與仿真[J].現代電子技術,2011,34(21):193-195.JIN Yu-lin,SHE Shi-gang,ZHOU Yi.Noise Analysis and Simulation of of PLL Loop Filter[J].Modern Electronics Technique,2011,34(21):193-195.

[5] Wideband Synthesizer with Integrated VCO ADF4350 Datasheet[Z].Analog Deices,2008.

[6] 徐述武,汪海勇,唐云峰.基于ADF4350鎖相頻率合成器的頻率源設計與實現[J].電子器件,2010,33(06):725-729.XU Shu-wu,WANG Hai-yong,TANG Yun-feng.Design and Realization of Frequency Source Based on ADF4350 PLL Frequency Synthesizer[J].Electronic Devices,2010,33(06):725-729.

[7] Song Q,Qi J.ADF4350-based Frequency Modulation transmitter design[C].International Conference on Cyberspace Technology IET,2015:1-3.

[8] 黃建鋼.鎖相環頻率合成器相位噪聲分析[J].雷達與對抗,1994(03):57-63.HUANG Jian-gang.Phase Noise Analysis of Phaselocked Loop Frequency Synthesizer[J].Radar &Ecm,1994(03):57-63.

[9] Xu H,Peng L.Design of Ultra-broadband Microwave Sources Based on ADF4350[C].International Conference on Advanced Computer Control IEEE,2010:459-462.

[10] Cao H,Qu Y.A Miniaturized Frequency Synthesizer System Design Based on ADF4350[C].IEEE International Conference on Signal Processing,Communications and Computing IEEE,2016:1-4.