一種CMOS高階曲率補償?shù)膸痘鶞试措娐返脑O(shè)計

李樹鎮(zhèn),馮全源

(西南交通大學(xué) 微電子研究所,成都 611756)

一種CMOS高階曲率補償?shù)膸痘鶞试措娐返脑O(shè)計

李樹鎮(zhèn),馮全源

(西南交通大學(xué) 微電子研究所,成都 611756)

為解決傳統(tǒng)CMOS帶隙基準電壓源的溫度系數(shù)較高的問題,采用高階曲率補償方法,提出了一種新型的帶隙基準電壓源,這種基準電壓源的結(jié)構(gòu)簡單同時具有良好耗能性能,并且基準電壓的溫度系數(shù)得到一定的優(yōu)化.利用NMOS管工作在亞閾值區(qū)域時漏電流和柵源電壓的非線性特性,通過引入與基準電壓溫度系數(shù)成相反趨勢的高階補償電流,降低基準電壓的溫度系數(shù),以較少的硬件消耗為代價大幅提高了其溫度特性,最后推導(dǎo)出補償后的基準電壓的計算公式.基于0.18 μm BCD工藝進行仿真,結(jié)果表明:在-40℃~150℃溫度范圍內(nèi),基準電壓的溫度系數(shù)為6.94×10-6;電源電壓VDD在2.5~5.0 V范圍內(nèi),線性調(diào)整率為0.033%,電路在5 V電源電壓為下工作電流為7.36 μA;在典型工藝下(TT),電源抑制比(PSRR)為77.4 dB.基準電壓的溫度特性的理論分析結(jié)果與仿真結(jié)果吻合較好,通過高階補償后,帶隙基準電壓源表現(xiàn)出優(yōu)良的性能,滿足了帶隙基準源的低功耗和低溫漂的設(shè)計要求.

帶隙基準;高階曲率補償;低功耗;高精度;溫度系數(shù)

隨著集成電路、信號與系統(tǒng)和功率轉(zhuǎn)換器等的快速發(fā)展,帶隙基準源在模擬和數(shù)字電路中起到了重要的作用[1-3],例如在AD轉(zhuǎn)換器和DRAMs中的應(yīng)用.一般數(shù)據(jù)轉(zhuǎn)換器工作的溫度范圍是-40 ℃~125 ℃,12位編碼器的溫度系數(shù)為240×10-6和16位編碼器溫度系數(shù)為12×10-6.由于帶隙基準電壓幾乎不受溫度和電源電壓變化的影響[4-6],系統(tǒng)的精度和抗干擾能力直接受基準電壓的性能的影響,高性能的基準電壓已成為電力、電子行業(yè)中關(guān)鍵技術(shù)之一.文獻[7-8]介紹了幾種帶隙基準電壓源,文獻[7]提出的帶隙基準源結(jié)構(gòu),利用MOSFETs工作在弱反型區(qū)產(chǎn)生的正負溫度系數(shù)的電壓相加得到的基準電壓,雖然該結(jié)構(gòu)可以減小功耗,但是由于MOSFETs工作在弱反型區(qū)漏極電流是溫度函數(shù).當溫度變化時,基準電壓溫漂大,不能達到高精度的目的.文獻[8]中提出的一種傳統(tǒng)的帶隙基準電壓源,雖然通過增加三極管發(fā)射極面積減小運放的輸入失調(diào)電壓,但是該結(jié)構(gòu)精度低溫漂大.

由于傳統(tǒng)的基準電壓精度低和功耗大等缺點,本文基于傳統(tǒng)帶隙基準結(jié)構(gòu)的基礎(chǔ)上,首次提出了一種分段高階曲率補償?shù)膸痘鶞孰妷涸矗霉ぷ髟诓煌娏髅芏认碌娜龢O管的基極—發(fā)射極的壓差作用在MOSFET的源—漏極,在MOSFET中產(chǎn)生具有溫度特性電流,疊加到基準源上進行高階補償,實現(xiàn)低功耗、低溫漂以及較低的線性調(diào)整率.

1 帶隙基準的基本原理分析

1.1 帶隙基準的基本原理分析

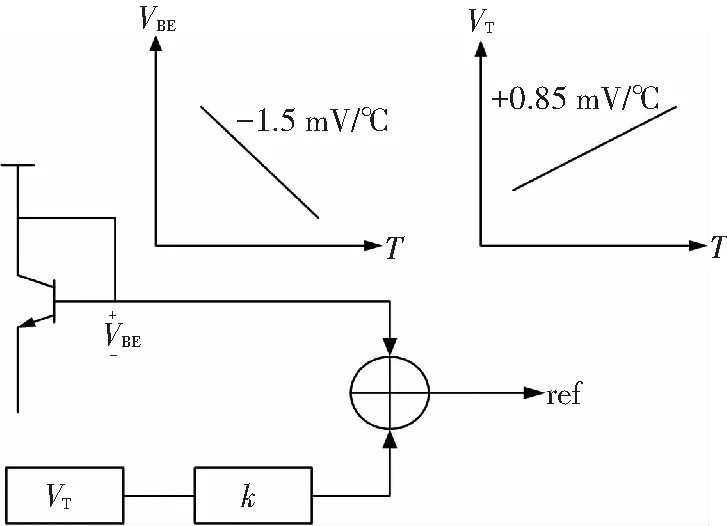

傳統(tǒng)帶隙基準電壓源基本原理如圖1所示,由于三極管的基極—發(fā)射極電壓VBE的溫度系數(shù)為-1.5 mV/℃,而熱溫度電壓VT(=kT/q)溫度系數(shù)為+0.085 mV/℃.其中k是Boltzmann常數(shù)(1.38×10-23J/K),T是絕對溫度,q是電子電荷量(1.6×10-19J)[9].如果將具有正溫度系數(shù)(PTAT)的電壓VT和具有負溫度系數(shù)(CTAT)的電壓VBE相加,理論上可以得到與溫度無關(guān)的基準電壓,就可以抑制溫度變化的影響[10-11].

圖1 帶隙基準的基本原理

如果正溫度系數(shù)電壓按一定比例加上負溫度系數(shù)電壓,那么基準電壓Vref可以表示為

Vref=VBE+KVT,

式中K為比例因子,那么基準電壓的溫度函數(shù)可以表示為

?Vref/?T=?VBE/?T+K?VT/?T.

只要合理的設(shè)置K值大小,理論上就可以得到零溫度系數(shù)的帶隙基準電壓.但是傳統(tǒng)結(jié)構(gòu)的基準電壓精度低溫漂大,不能滿足當今系統(tǒng)的設(shè)計要求,所以必須對帶隙基準電壓源進行溫度補償.

1.2 分段高階曲率補償原理

由于傳統(tǒng)的帶隙基準源的溫度特性曲線只有一個極值點,提高帶隙基準電壓精度的有效方法是使帶隙基準電壓的溫度特性曲線具有多個極值點,而不是只有一個峰值或谷值.想要獲得高精度的基準電壓源,必須需要高階的溫度曲率補償[12-13].一階溫度補償僅僅可以補償溫度T的一次項,而僅僅通過傳統(tǒng)的補償技術(shù)不能達到基準電壓的高階溫度曲率補償,就不能獲得高精度的帶隙基準源.

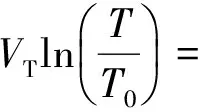

如圖2所示是利用補償技術(shù)得到的帶隙基準源的溫度特性曲線.采用合適的補償方法,在低溫或者高溫區(qū)域引入與基準電壓的溫度特性曲線呈相反趨勢的補償電流,使溫度特性曲線在低溫或高溫區(qū)域產(chǎn)生新的極點.

圖2 高階補償?shù)幕驹?/p>

高階補償技術(shù)可以抵消溫度T的高次項,通過高階補償可以得到高精度的基準電壓源.理論上最好的方法是利用有TlnT的函數(shù)去補償VBE的高階非線性項,而TlnT函數(shù)在實際中很難獲得,一般用近似的方法得到TlnT的函數(shù),一般情況下是以Tln[T/Vref]的函數(shù)實現(xiàn),Tln[T/Vref]補償技術(shù)如圖2所示,Vref_first(second/third)是補償?shù)淖顑?yōu)點,Tln[T/Vref]可以準確的抵消VBE的非線性項,如果補償電壓值電壓大于或者小于Vref_first(second/third),將會出現(xiàn)補償不夠或者補償過度,基準電壓不能得到精確的補償.只有選擇合適的補償電壓,基準電壓才能具有低的溫度系數(shù).

選擇三極管是因為它有很好的溫度特性[14],三極管的基極—發(fā)射極電壓VBE可以表示為

VBE(T)=VG0(T0)-[VG0(T0)-VBE(T0)]T/T0-

(η-ζ)VTln(T/T0).

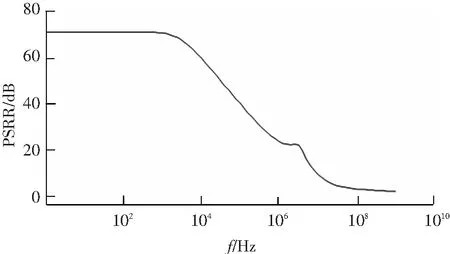

式中:VG0(T0)為溫度在T時的帶隙基準電壓;VBE(T0)為BJT管在溫度T0時基極—發(fā)射極的壓降;η為與溫度無關(guān)而與工藝相關(guān)的常數(shù);ζ為集電極電流隨溫度變化的指數(shù); [VG0(T0)-VBE(T0)]T/T0為與溫度相關(guān)的一次相;(η-ζ)VTln(T/T0)為高階非線性相.在T0時刻將VTln(T/T0)泰勒展開得到:

(1)

基于這一原理提出了如圖3所示的高階曲率補償?shù)膸痘鶞孰妷涸?

2 新型的帶隙基準電壓源設(shè)計

本文提出的高階曲率補償帶隙基準電壓源由3個部分組成,分別為啟動電路、帶隙基準核心電路和補償電路.

2.1 啟動電路

啟動電路是帶隙基準電壓源中不可缺少的,作用在于使帶隙基準電路脫零工作點狀態(tài).如圖3所示,啟動電路由NM1~NM6、R1、R2和C0組成.其中NM1~NM4構(gòu)成二極管的連接方式,上電階段,NM1~NM4處于線性工作區(qū),隨著電源電壓的升高,NM5的柵極電壓逐迅速升高而導(dǎo)通,電源電壓通過NM5向基準注入電流,基準電路開始啟動.啟動完成后,隨著基準電壓的升高,NM6會把A點拉低而關(guān)閉NM5,基準啟動結(jié)束.

2.2 基準核心電路

本文設(shè)計基準產(chǎn)生電路如圖3所示,帶隙基準的運算放大器是由Q3、Q4、R3、PM7和PM8組成,電路中的運放不需要額外的偏置電流源,可以減小基準的功耗,主要思想是利用反函數(shù)技術(shù)——跨導(dǎo)gmr和互阻gmc的函數(shù),因為ΔVBE=VBE2-VBE1gmr·gmc·ΔVBE=MΔVBE·gmc.ΔVBE可能產(chǎn)生非線性電流,跨導(dǎo)gmr可以抵消非線性電流并且產(chǎn)生需要的增益M.帶隙基準的核心是由R5~R9、Q1和Q2組成,差放的兩個輸入端分解接在Q1的集電極和Q2的集電極,鉗制X點和Y點的壓差相等,三極管Q1和Q2的組成一種復(fù)合管的連接方式,Q1與Q2的基極—射極的壓差ΔVBE作用在電阻R7上,產(chǎn)生正溫度系數(shù)電流,由于電阻R6=R7,所以流過R6和R7的電流相等.設(shè)Q1和Q2的電流密度之比為n∶1.基準電壓Vref可以表示為

電路中NM10接成源跟隨器的形式,大幅度減小其輸出阻抗,它為基準核心提供所需電流.

圖3 采用高階曲率補償方法設(shè)計的帶隙基準電壓源

2.3 補償電路

本文提出的高階補償電路如圖3所示,由Q5~Q7、PM12~PM16、NM17、NM18和R10組成,主要機理是隨著溫度的升高,Q2基極的負溫度系數(shù)電壓作用在NM17的柵極,產(chǎn)生CTAT電流,根據(jù)MOS管的特性可知,NM17的漏極電流ICTAT可表示為

(2)

式中S為工藝常數(shù).PM14~PM16組成電流鏡結(jié)構(gòu),PM15和PM16的漏極電流可以表示為IPM15=αIPM14,IPM16=βIPM14,其中α=WL(PM15)/WL(PM14),β=WL(PM16)/WL(PM14).

由于Q6和Q7的有效發(fā)射截面積比為M∶1,兩者基極—射極的壓差作用在NM18的漏極和源級,驅(qū)使NM18工作在線性區(qū).NM18的漏極電流INM18可表示為

(3)

由于MOSFET的閾值電壓VTH與溫度成線性關(guān)系,可以表示成

VTHT=VTHT0-μT-T0.

(4)

根據(jù)基爾霍夫定律(KCL)可知,結(jié)合式(1),式(2)~(4)展開,三極管Q5的集電極電流ICQ5可表示為

ICQ5≈INM18-αICTAT=-aT4+bT3+cT2-dT-eT1,

(5)

其中:

式中:μ為閾值電壓的溫度相關(guān)系數(shù);VTH0為MOSFET的襯底和源極電壓的差值為零時的閾值電壓.由此可以得出a、b、c、d和e是與溫度無關(guān)的常數(shù).根據(jù)式(2)、(3)可知,ICTAT和INM18都是負溫度系數(shù)的電流,而INM18的比例系數(shù)大于ICTAT,隨著溫度升高,INM18下降速度要快于ICTAT,由式(5)可知基準電壓源的補償電流的穿越溫度為T1,在溫度T≤T1時,補償電流對基準電壓Vref的溫度特性曲線進行高階補償,減小基準電壓的溫度系數(shù);當T>T1時,Q5處于截至區(qū)沒有電流通過,ICQ5=0,綜上所述,補償電流可表示為

通過調(diào)整PM14~PM16電流鏡的比例和NM18的寬長比等參數(shù),可以實現(xiàn)對穿越溫度為T1的調(diào)節(jié),補償電流ICQ5注入到電阻R9,對基準的溫度特性曲線進行高階補償,在高溫時關(guān)閉補償電流.經(jīng)過補償后的帶隙基準電壓Vref可表示為

高階補償電路由ICTAT為其提供偏置電流,它的大小決定了補償電路的功耗,由于ICTAT具有負溫度系數(shù)特性,高階補償電路的功耗隨著溫度的升高而減小.要實現(xiàn)補償?shù)淖顑?yōu)化,在盡可能減少硬件開銷的情況下,也要限制電路的功耗,并且使芯片面積達到最小,所以要合理的設(shè)置各個器件的參數(shù)以達到性能最優(yōu).

3 仿真結(jié)果

本文帶隙基準電壓源仿真采用0.18 μm BCD工藝.利用Hspice仿真軟件,溫度在25 ℃,基準電壓線性調(diào)整率仿真結(jié)果如圖4所示.仿真結(jié)果表明,基準電壓的典型值為1.229 V.供電電壓VDD在2.5~5.0 V范圍內(nèi),線性調(diào)整率為0.033%.

圖4 基準電壓隨電源電壓的變化曲線

基準電壓源的溫度特性仿真結(jié)果如圖5所示,供電電壓VDD為5 V,在-40 ℃~150 ℃的溫度范圍內(nèi),仿真結(jié)果表明,基準電壓源補償前的的溫度系數(shù)為20×10-6/℃,補償后的溫度系數(shù)為6.94×10-6/℃,可以看出補償后帶隙基準電壓源的溫度特性得到明顯的改善.

圖5 基準電壓溫度特性曲線

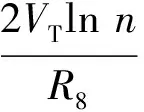

基準電壓源的電源抑制比仿真結(jié)果如圖6所示,供電電壓VDD為5 V,溫度為25 ℃,仿真結(jié)果表明,低頻時PSRR為77 dB,具有很好的抑制電源干擾的能力.

圖6 基準電壓的PSRR仿真結(jié)果

基準電壓源功耗如圖7所示,從仿真結(jié)果可以看出,電路的靜態(tài)電流功耗僅為7.36 μA,電路具有較低的功耗.

圖7 電路工作電流仿真結(jié)果

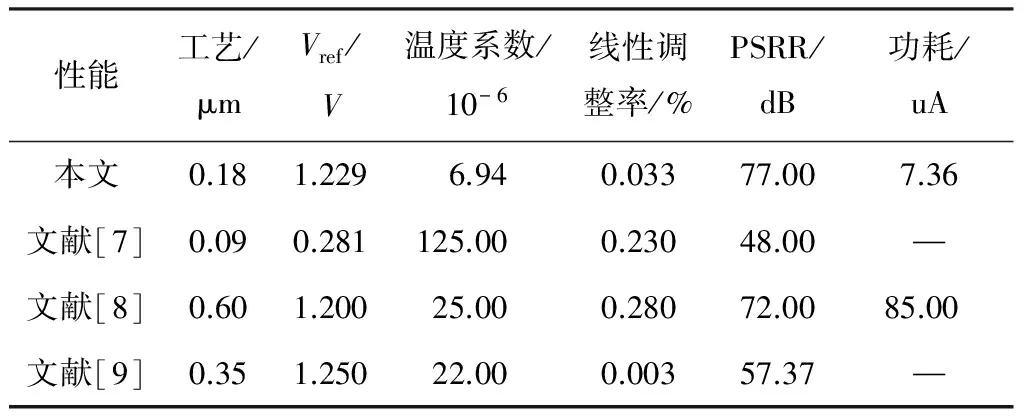

表1為本文和文獻[7-9]的參數(shù)性能的比較,從表1中可以看出,基準電壓源的溫度系數(shù)明顯優(yōu)于文獻[7-9],功耗遠低于文獻[8].

表1 帶隙基準的性能比較

4 結(jié) 論

1)本文對傳統(tǒng)的帶隙基準電壓源結(jié)構(gòu)進行改進,提出了一種新型的高階曲率補償?shù)膸痘鶞孰妷弘娐罚撾娐分胁捎昧艘环N簡單的補償電路實現(xiàn)高階曲率補償,使基準電壓的溫度特性曲線呈現(xiàn)出多個極值點,克服了傳統(tǒng)帶隙基準電壓帶隙基準源的溫度特性差的缺點,同時電路正常工作時需要較小的電流.雖然利用三極管占用較多的芯片面積,但性能優(yōu)勢是明顯的.

2)通過和傳統(tǒng)的帶隙基準電壓源性能的對比,表明了高階曲率補償方法可以使基準電壓源獲得良好的溫度特性,通過仿真對比,證明了所設(shè)計的補償電路明顯的提高了溫度特性.結(jié)果表明,各項指標性能滿足設(shè)計要求.此基準電壓源可以應(yīng)用到對性能要求較為嚴格場合,如掌上電腦、第3代手機和GPS接收器等等.

[1] PARK J S, AN T J, KIM Y M, et al. A 10b 50MS/s 90nm CMOS skinny-shape ADC using variable references for CIS applications[C]//2013 International Soc Design Conference. Busan, South Korea: IEEE, 2013: 80-82. DOI: 10.1109/ISOCC.2013.6863990.

[2] FULDE M, WIMSHOFER M, KNOBLINGER G, et al. Design of low-voltage bandgap reference circuits in multi-gate CMOS technologies[C]//IEEE International Symposium on Circuits and Systems. Taipei, Taiwan: IEEE, 2009: 2537-2540. DOI: 10.1109/ISCAS.2009.5118318.

[3] YANG Xinbo, DENG Honghui, QUAN Lei, et al. A differential reference voltage source and its output buffer used in high-speed high-precision pipelined ADC[C]//Proceedings of the 5th International Congress on Image and Signal Processing. Chongqing, China: IEEE, 2012:1398-1402. DOI: 10.1109/CISP.2012.6469818.

[4] MA Jirong, LI Yongming, ZHANG Chun, et al. A 1V Ultra-low power high precision CMOS voltage reference[C] // IEEE Conference on Electron Devices and Solid-State Circuits. Tainan, Taiwan: IEEE, 2008: 847-850. DOI: 10.1109/EDSSC.2007.4450258.

[5] 李睿,馮全源.一種低功耗高精度帶隙基準的設(shè)計[J].電子技術(shù)應(yīng)用, 2015, 41(3): 51-54. DOI: 10.16157/j.issn.0258-7998.2015.03.012.

LI Rui, FENG Quanyuan. Design of a bandgap reference voltage with low power consumption and high-accurary [J]. Application of Electronic Technique, 2015, 41(3): 51-54. DOI: 10.16157/j.issn.0258-7998.2015.03.012.

[6] WADHWA S K. A low voltage CMOS bandgap reference circuit[C]//International Symposium on Circuits and Systems. Seattle, WA: IEEE, 2008: 2693-2696. DOI: 10.1109/ISCAS.2008.4542012.

[7] MOHAMMED M, ABUGHARBIEH K, ABDELFATTAH M, et al. Design of a voltage reference circuit based on subthreshold and triode MOSFETs in 90nm CMOS[C]//IEEE International Conference on Ic Design & Technology. Austin, TX: IEEE, 2014:1-4. DOI: 10.1109/ICICDT.2014.6838605.

[8] 唐宇,馮全源.一種低溫漂低功耗帶隙基準的設(shè)計[J].電子元件與材料, 2014, 33(2): 35-38. DOI: 10.3969/j.issn.1001-2028.2014.02.009.

TANG Yu, FENG Quanyuan. Design of a bandgap reference with low temperature-drift and low power consumption[J]. Electronic Components and Materials, 2014, 33(2): 35-38. DOI: 10.3969/j.issn.1001-2028.2014.02.009.

[9] 王宇星,朱波.一種用于PWM控制Buck型DC-DC變換器的帶隙基準源[J].電子器件,2013,36(2): 252-255. DOI: 10.3969/j.issn.1005-9490.2013.02.026.

WANG Yuxing, ZHU Bo. A CMOS bandgap reference for PWM control buck DC-DC converters[J].Chinese Journal of Electron Devices, 2013, 36(2): 252-255. DOI: 10.3969/j.issn.1005-9490.2013.02.026.

[10]CHOUHAN SS, HALONEN K. A micro-power 4.8 ppm/℃ CMOS voltage reference circuit for linear drop out regulator used in RFID[C]//Proceedings of the 20th International Conference on Electronics, Circuits, and Systems. Abu Dhabi, United Arab Emirates: IEEE, 2013: 893-896. DOI: 10.1109/ICECS.2013.6815557.

[11]TAN Xiaoyun, LIANG Chen, SHI Min, et al. A low temperature coefficient 4th-order curvature-compensated CMOS bandgap reference[C]// Academic International Symposium on Optoelectronics and Microelectronics Technology. Harbin, China: IEEE,2011:251-254. DOI: 10.1109/AISMOT.2011.6159366.

[12]DUAN Quanzhen, ROH J. A 1.2-V 4.2-ppm/℃ high-order curvature-compensated CMOS bandgap reference[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2015, 62(3): 662-670. DOI:10.1109/TCSI.2014.2374832.

[13]PENG Zhenyu, LV Changzhi, SHE Shuojie. A High-order temperature curvature compensated CMOS bandgap reference[C]//Proceedings of the 2nd International Conference on Consumer Electronics, Communications and Networks. Yichang, China: IEEE, 2012: 2254-2257. DOI: 10.1109/CECNet.2012.6201536.

[14]MA B, YU Fengqi. A novel 1.2-V 4.5-ppm/℃ curvature-compensated CMOS bandgap reference[J]. IEEE Transactions on Circuits Systems I: Regular Papers, 2014, 61 (4):1026-1035. DOI: 10.1109/TCSI.2013.2286032.

DesignofaCMOSbandgapreferencecircuitwithhighordercurvaturecompensation

LI Shuzhen, FENG Quanyuan

(Institute of Microelectronics, Southwest Jiaotong University, Chengdu 611756, China)

A bandgap reference is designed with high order curvature compensation method, which has advantages of simple structure, good energy dissipation capacity and an optimized temperature coefficient of the reference voltage. Taking advantage of the nonlinear characteristics between leakage current and gate-source voltage when NMOS is working in the sub-threshold region, the proposed method decreases the temperature coefficient of reference voltage by introducing a high order curvature compensation current of which the temperature coefficient is contrary to reference. The formula of the compensated reference voltage is derived. Based on the 0.18 μm BCD process, the simulation results show that temperature coefficient of reference is 6.94×10-6in the temperature range of -40 ℃~150 ℃, linear regulation rate is 0.033% in the supply voltageVDDrange of 2.5~5.0 V, the supply current is 7.36 μA with 5V power supply, the power supply rejection ratio(PSRR) is 77.4 dB at the Tipical corner(TT). The theoretical analysis results of reference agree well with the simulated results. The bandgap reference voltage source shows excellent performance vias the high order compensation, which satisfies the requirement of low power consumption and low temperature drift in bandgap reference designing.

bandgap reference; high order curvature compensation; low power consumption; high-precision performance; temperature coefficient

10.11918/j.issn.0367-6234.201604085

TN433

A

0367-6234(2017)10-0095-05

2016-04-16

國家自然科學(xué)基金重點項目(61531016);國家自然科學(xué)基金面上項目(61271090);四川省科技支撐計劃項目(2015GZ0103)

李樹鎮(zhèn)(1990—),男,碩士研究生;

馮全源(1963—),男,教授,博士生導(dǎo)師

馮全源,fengquanyuan@163.com

(編輯張 紅)