基于有限狀態(tài)機(jī)的多周期CPU實驗設(shè)計

馮建文

(杭州電子科技大學(xué) 計算機(jī)學(xué)院, 浙江 杭州 310018)

基于有限狀態(tài)機(jī)的多周期CPU實驗設(shè)計

馮建文

(杭州電子科技大學(xué) 計算機(jī)學(xué)院, 浙江 杭州 310018)

設(shè)計了一個基于FPGA的多周期CPU實驗,并將有限狀態(tài)機(jī)應(yīng)用于模型計算機(jī)的設(shè)計與實現(xiàn)。模型計算機(jī)基于MIPS處理器,含8條典型指令。給出了多周期CPU的數(shù)據(jù)通路與指令流程圖,并按照有限狀態(tài)機(jī)的設(shè)計方法,完成了狀態(tài)轉(zhuǎn)移圖的設(shè)計和HDL的程序描述。實驗不僅使學(xué)生掌握有限狀態(tài)機(jī)這一重要的數(shù)字系統(tǒng)設(shè)計工具,同時也有助于學(xué)生加深理解“計算機(jī)就是一個有限狀態(tài)機(jī)”的概念。在課程實踐應(yīng)用中教學(xué)效果良好。

多周期CPU; 有限狀態(tài)機(jī); 實驗設(shè)計; FPGA

CPU是計算機(jī)硬件系統(tǒng)的核心部件,CPU的設(shè)計與實現(xiàn)是“計算機(jī)組成原理”課程實踐環(huán)節(jié)的重要內(nèi)容[1-3]。隨著EDA技術(shù)的迅猛發(fā)展,使用FPGA實驗平臺完成硬件實驗已成為計算機(jī)硬件課程實踐教學(xué)的主流趨勢[4-5]。

但是受課時等因素的影響,地方高校“計算機(jī)組成原理”實驗課程通常采用單周期方式設(shè)計CPU[6],然而卻不能適用于后續(xù)的流水線CPU設(shè)計。本文設(shè)計了一個基于FPGA的多周期CPU實驗,將有限狀態(tài)機(jī)應(yīng)用于CPU的設(shè)計與實現(xiàn),既為后續(xù)的流水線CPU設(shè)計打下基礎(chǔ),也培養(yǎng)了學(xué)生對復(fù)雜工程問題的分析與解決能力[7-8]。

1 CPU模型與結(jié)構(gòu)

CPU的模型與指令系統(tǒng)均基于MIPS處理器。

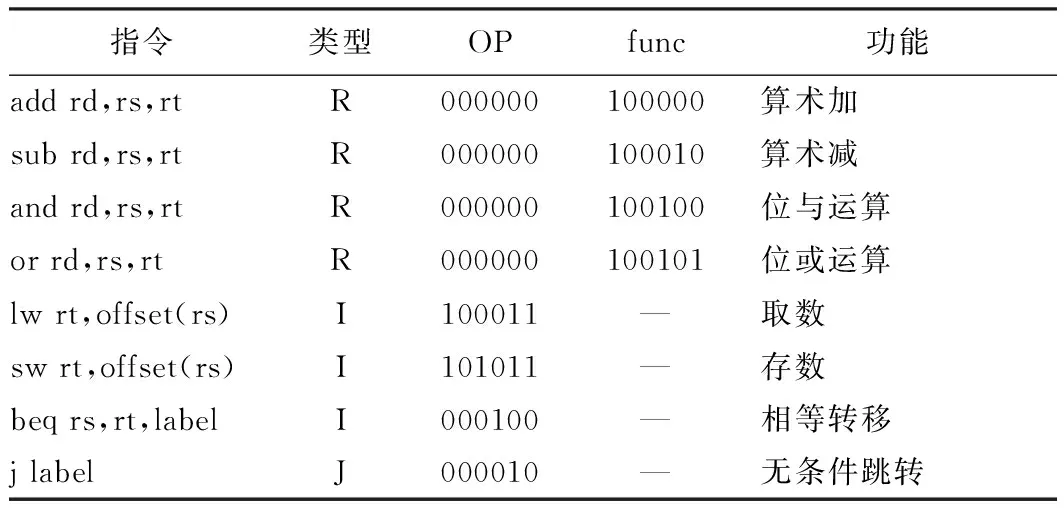

在MIPS處理器的核心指令集中,選取了8條典型指令,指令格式、編碼與功能如表1所示。

表1 指令系統(tǒng)編碼與功能表

在前期的單周期CPU設(shè)計實驗的基礎(chǔ)上,引導(dǎo)學(xué)生分析多周期CPU的特點并設(shè)計系統(tǒng)結(jié)構(gòu)與數(shù)據(jù)通路[9-10](見圖1)。

圖1 CPU的系統(tǒng)結(jié)構(gòu)與數(shù)據(jù)通路框圖

在CPU的多周期實現(xiàn)方案中,指令的執(zhí)行被分成若干步驟,每一步驟占用一個機(jī)器周期。一方面,硬件在不同機(jī)器周期可以重復(fù)使用;另一方面,在上一周期中指令執(zhí)行的結(jié)果,需要用于下一周期的操作。因此,必須添加功能部件之間的緩沖寄存器,用以暫存時鐘周期之間交換的數(shù)據(jù)。例如圖1中的暫存器A、B用于保存從寄存器堆讀出的數(shù)據(jù),F用于保存ALU運算的結(jié)果,MDR用于保存從存儲器讀出的數(shù)據(jù),IR用于保存從存儲器讀出的指令。

圖中的寄存器堆為三端口寄存器,含兩個讀端口A、B和一個寫端口,能同時執(zhí)行A、B兩個端口的讀操作和寫端口的寫操作。

2 指令執(zhí)行的過程分析

2.1 指令流程圖

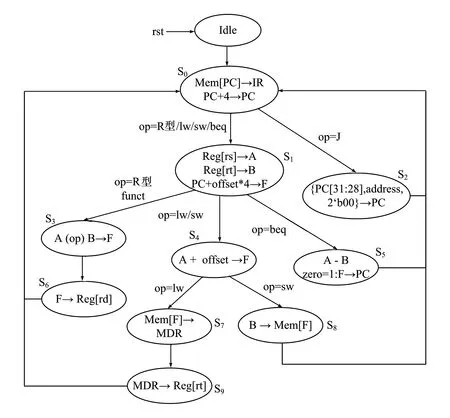

對指令系統(tǒng)中的每一條指令進(jìn)行逐條分析,研究其在圖1上的數(shù)據(jù)通路,按照機(jī)器周期可以畫出指令流程圖,如圖2所示。

圖2 指令流程圖

由圖2可見,8條指令中,指令周期最長的指令是lw指令,需要5個機(jī)器周期M0—M4。

2.2 控制信號流

根據(jù)指令執(zhí)行過程分析及數(shù)據(jù)通路分析,引導(dǎo)學(xué)生進(jìn)一步細(xì)化控制需求。一是需要在部件入口處添加一系列的數(shù)據(jù)選擇器,二是定義控制信號含義[6]。圖3為細(xì)化后的模型計算機(jī)的完整數(shù)據(jù)通路與控制線路。圖3中的粗體字為部件控制信號與多路選擇器的選擇信號,其中,選擇器中的數(shù)字指明了選擇信號的定義。部件控制信號具體定義如表2所示。

圖3 多周期CPU的模型計算機(jī)完整數(shù)據(jù)通路與控制線路

部件控制信號作用有效邊沿PCPC_write寫入PC作用周期下跳沿存儲器Mem_write寫入存儲器作用周期上跳沿IRIR_write寫入IR作用周期下跳沿寄存器堆Reg_write寫入寄存器作用周期下跳沿

從表2可以看出,寄存器的寫入操作總是在后邊沿有效,以保證功能部件操作完成后,再保存結(jié)果。存儲器的讀寫操作均在時鐘上跳沿執(zhí)行。

寄存器堆和存儲器沒有讀信號,寄存器讀操作不受時鐘控制且始終讀出;存儲器則在每個時鐘的上跳沿執(zhí)行讀出操作。暫存器MDR、A、B、F沒有控制信號,直接使用CPU時鐘作為其時鐘脈沖——意即每個時鐘周期后沿,它們均要執(zhí)行寫入操作,且沒有輸出控制,內(nèi)容始終可用。

3 有限狀態(tài)機(jī)的實現(xiàn)

3.1 有限狀態(tài)機(jī)概述

FPGA最大的優(yōu)勢是它的電路是并行實現(xiàn)的,從而具有高速性。但是有限狀態(tài)機(jī)則可以通過狀態(tài)遷移來完成一些特定的順序控制邏輯,而非并行邏輯,例如指令的執(zhí)行。

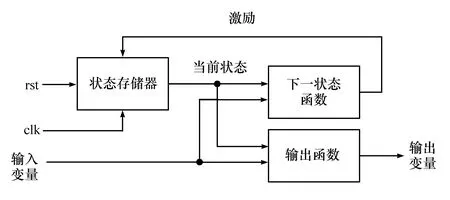

有限狀態(tài)機(jī)包含了1個狀態(tài)存儲器和2個函數(shù)——下一狀態(tài)函數(shù)和輸出函數(shù)[10-11],如圖4所示。

圖4 有限狀態(tài)機(jī)的結(jié)構(gòu)圖

rst是復(fù)位信號,用于確定有限狀態(tài)機(jī)的初始狀態(tài);clk是時鐘信號,用于同步狀態(tài)轉(zhuǎn)換的邊沿。狀態(tài)存儲器是儲存狀態(tài)機(jī)狀態(tài)的一組觸發(fā)器,觸發(fā)器的次態(tài)由下一狀態(tài)函數(shù)決定,下一狀態(tài)函數(shù)則是輸入變量和當(dāng)前狀態(tài)的函數(shù),通過激勵狀態(tài)觸發(fā)器,實現(xiàn)狀態(tài)的轉(zhuǎn)移。狀態(tài)機(jī)的輸出,則由輸出函數(shù)決定,它是當(dāng)前狀態(tài)和輸入變量的組合邏輯函數(shù)。

使用FPGA設(shè)計有限狀態(tài)機(jī)的步驟如下:

(1) 確定輸入、輸出與狀態(tài)機(jī)狀態(tài),畫出狀態(tài)轉(zhuǎn)移圖;

(2) 狀態(tài)簡化,得到最簡的狀態(tài)轉(zhuǎn)移圖;

(3) 對狀態(tài)進(jìn)行編碼:有binary、gray、one-hot等編碼方式,在FPGA的開發(fā)平臺中,可以進(jìn)行選擇和自定義;

(4) 使用HDL描述,并綜合、仿真與實現(xiàn)。

3.2 多周期CPU的有限狀態(tài)機(jī)設(shè)計

在有限狀態(tài)機(jī)相關(guān)知識的基礎(chǔ)上,引導(dǎo)學(xué)生設(shè)計多周期CPU的有限狀態(tài)機(jī)。

3.2.1 狀態(tài)圖

圖2(指令流程圖)是原始狀態(tài)轉(zhuǎn)移圖,經(jīng)過分析、化簡,可得到圖5所示的最簡狀態(tài)轉(zhuǎn)移圖,除空閑狀態(tài)Idle之外,圖中有10個有效狀態(tài)。顯然,圖5所示的狀態(tài)機(jī)是CPU的控制器,除了定序之外,還要發(fā)送各個控制信號和多路選擇信號。狀態(tài)機(jī)的輸入變量就是指令碼,輸出變量即為所有的控制信號和多路選擇信號。分析可知,該有限狀態(tài)機(jī)為Mealy型狀態(tài)機(jī),因為其輸出的控制信號取決于當(dāng)前狀態(tài)與輸入的指令碼。

圖5 最簡狀態(tài)轉(zhuǎn)移圖

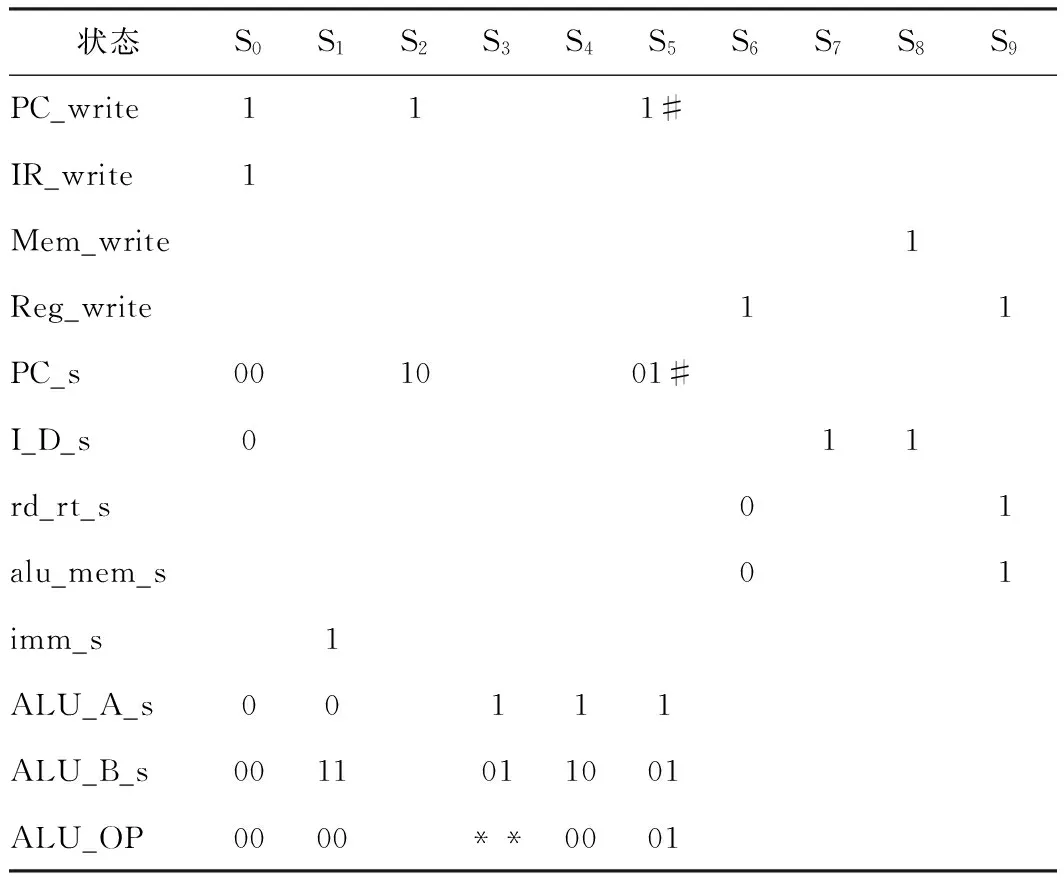

3.2.2 狀態(tài)輸出的信號

結(jié)合圖3的數(shù)據(jù)通路,分析每一個狀態(tài)下輸出的有效信號如表3所示。

表3 各狀態(tài)下有效的控制信號

注:#表示當(dāng)zero=1時;**表示根據(jù)指令的func字段譯碼

3.2.3 狀態(tài)機(jī)的HDL描述

在有限狀態(tài)機(jī)的HDL實現(xiàn)上,使學(xué)生了解一段式、二段式和三段式描述各自的優(yōu)缺點,引導(dǎo)學(xué)生嘗試使用更可靠的三段式方法描述多周期CPU的控制器有限狀態(tài)機(jī),即:狀態(tài)轉(zhuǎn)移、次態(tài)函數(shù)和輸出函數(shù)各用一個或者多個獨立的always或者assign語句實現(xiàn)。三段式有限狀態(tài)機(jī)的框架如下:

//狀態(tài)轉(zhuǎn)移 always @(posedge rst or posedge clk)begin if (rst)ST <= Idle; else ST <= Next_ST; end //次態(tài)函數(shù) always @(*)begin Next_ST = Idle; case (ST) Idle: Next_ST = S0; S0: if (OP==`OP_J_J) Next_ST = S2; else Next_ST = S1; ……//次態(tài)的阻塞式賦值 default:Next_ST = S0; endcase end //輸出函數(shù) always @(posedge rst or posedge clk) begin if (rst)begin PC_write <= 1′b0; IR_write <= 1′b0; ……//全部信號初始化為0 end else begin case(Next_ST) S0:begin//信號的非阻塞式賦值 PC_write<=1′b1;IR_write<=1′b1;…… end ……//每個狀態(tài)下輸出的控制信號 endcase end; end assign Mem_write = (Next_ST==S8); assign I_D_s = (Next_ST==S7)||(Next_ST==S8);

上述輸出函數(shù)的代碼中,大部分使用次態(tài)Next_ST作為輸入,對控制信號進(jìn)行非阻塞式賦值。但是,因為存儲器的讀寫操作在clk上跳沿觸發(fā),所以地址選擇信號I_D_s和存儲器寫信號Mem_write需要使用數(shù)據(jù)流驅(qū)動,以保證存儲器地址和讀寫信號先于clk上跳沿置為有效。

3.2.4 測試程序與調(diào)試

控制器的有限狀態(tài)機(jī)只是模型計算機(jī)的一部分,其他計算機(jī)部件如存儲器、運算器、專用寄存器等,需要指導(dǎo)學(xué)生在單周期CPU的基礎(chǔ)上進(jìn)行改造。

將各部件通過控制器的有限狀態(tài)機(jī)連接而成整機(jī),然后針對實現(xiàn)的MIPS指令集自行編寫測試程序。綜合與實現(xiàn)后,對模型計算機(jī)進(jìn)行功能仿真,如圖6所示。

圖6 多周期CPU的功能仿真

板級驗證可借助按鍵、數(shù)碼管等輸入、輸出設(shè)備進(jìn)行單步執(zhí)行,顯示狀態(tài)機(jī)每一個狀態(tài)下的執(zhí)行結(jié)果,如圖7所示為當(dāng)前指令碼的高16位。

圖7 多周期CPU的板級驗證

4 結(jié)語

多周期CPU具有時鐘周期短、各功能部件可共享的優(yōu)點,它既符合現(xiàn)代CPU的真實設(shè)計,又是流水線CPU設(shè)計的基礎(chǔ)。采用有限狀態(tài)機(jī)實現(xiàn)其控制單元部分,不僅能夠幫助學(xué)生掌握有限狀態(tài)機(jī)這一重要的數(shù)字系統(tǒng)設(shè)計工具,也有助于學(xué)生進(jìn)一步深刻理解“計算機(jī)就是一個有限狀態(tài)機(jī)”的概念。

多周期CPU實驗基于FPGA實驗平臺而開設(shè),使實驗具有較高的開放性和擴(kuò)展性[12],在指令集的選取、有限狀態(tài)機(jī)的狀態(tài)分析、控制信號設(shè)計、輸出函數(shù)的硬布線設(shè)計、測試程序與板級調(diào)試等環(huán)節(jié),均可以為學(xué)生提供自主設(shè)計與發(fā)揮的空間,培養(yǎng)學(xué)生的綜合分析、研究與設(shè)計能力。在課程實踐中,絕大多數(shù)學(xué)生達(dá)到了設(shè)計目標(biāo),收到了良好的實驗教學(xué)效果。

References)

[1] 姜欣寧,陳宇.“計算機(jī)組成原理專題實驗”的教學(xué)改革[J].實驗技術(shù)與管理,2013,30(4):162-165.

[2] 高小鵬.計算機(jī)專業(yè)系統(tǒng)能力培養(yǎng)的技術(shù)途徑[J].中國大學(xué)教學(xué),2014(8):53-57.

[3] 周剛,師維,陳潤,等.計算機(jī)組成原理實驗創(chuàng)新性改革探索與實現(xiàn)[J].實驗技術(shù)與管理,2016,33(11):26-29.

[4] 劉敬猛,徐東,陳柏成,等.少學(xué)時FPGA實驗課體系結(jié)構(gòu)[J].實驗技術(shù)與管理,2012,29(4):280-282.

[5] 肖堃,邢建川.計算機(jī)專業(yè)硬件實驗體系與綜合實驗平臺[J].實驗科學(xué)與技術(shù),2012,10(6):227-229.

[6] 馮建文,章復(fù)嘉,包健.計算機(jī)組成原理與系統(tǒng)結(jié)構(gòu)實驗指導(dǎo)書[M].2版.北京:高等教育出版社,2015.

[7] 劉衛(wèi)東,張悠慧,向勇,等.面向系統(tǒng)能力培養(yǎng)的計算機(jī)專業(yè)課程體系建設(shè)實踐[J].中國大學(xué)教學(xué),2014(8):48-52.

[8] 全成斌,鄭寧漢,楊士強(qiáng).計算機(jī)一體化實驗教學(xué)改革與探索[J].中國大學(xué)教學(xué),2014(6):78-80.

[9] Patterson D A, Hennessy J L.計算機(jī)組成與設(shè)計:硬件/軟件接口[M].英文版.北京:機(jī)械工業(yè)出版社,2013.

[10] Harris D M,Harris S L.數(shù)字設(shè)計和計算機(jī)體系結(jié)構(gòu)[M].英文版.北京:機(jī)械工業(yè)出版社,2016.

[11] 夏宇聞.Verilog數(shù)字系統(tǒng)設(shè)計教程 [M].3版.北京:北京航空航天大學(xué)出版社,2013.

[12] 劉玉潔,沈世全.多級流水線處理機(jī)的少課時實踐內(nèi)容設(shè)計[J].實驗技術(shù)與管理,2016,33(7):96-99.

Design of multi-period CPU experiment based on finite state machine

Feng Jianwen

(School of Computer Science and Technology, Hangzhou University of Electronic Science and Technology,Hangzhou 310018,China)

A multi-period CPU experiment based on FPGA is designed,and the finite state machine is designed and applied to the model computer. The model computer is based on MIPS processor with 8 typical instructions. The data path and instruction flow chart of multi-period CPU are presented,and according to the design method of the finite state machine,the state transition diagram and the program description of HDL are completed. The experiment helps the students not only to grasp the important digital system design tool of the finite state machine,but also to understand the concept that “Computer is a finite state machine.” In practice,the teaching effect is fine.

multi-period CPU; finite state machine; experimental design; FPGA

10.16791/j.cnki.sjg.2017.07.033

2017-01-19

教育部國家精品資源共享課程“計算機(jī)組成原理”;浙江省教育技術(shù)研究規(guī)劃課題(JA007)

馮建文(1971—),女,浙江杭州,碩士,副教授,主要研究方向為嵌入式系統(tǒng)與智能控制.

E-mail:fengjianwen@hdu.edu.cn

G642;TP3-4

A

1002-4956(2017)07-0127-05