雷達(dá)回波存儲(chǔ)設(shè)備的信號完整性研究

范國浩, 楊少博, 張艷兵, 馬鐵華

(1.中北大學(xué) 電子測試技術(shù)國家重點(diǎn)實(shí)驗(yàn)室,山西 太原 030051;2.中北大學(xué) 儀器科學(xué)與動(dòng)態(tài)測試教育部重點(diǎn)實(shí)驗(yàn)室,山西 太原 030051)

雷達(dá)回波存儲(chǔ)設(shè)備的信號完整性研究

范國浩1,2, 楊少博1,2, 張艷兵1,2, 馬鐵華1,2

(1.中北大學(xué) 電子測試技術(shù)國家重點(diǎn)實(shí)驗(yàn)室,山西 太原 030051;2.中北大學(xué) 儀器科學(xué)與動(dòng)態(tài)測試教育部重點(diǎn)實(shí)驗(yàn)室,山西 太原 030051)

該文設(shè)計(jì)高速雷達(dá)回波存儲(chǔ)系統(tǒng),針對在系統(tǒng)設(shè)計(jì)過程中可能出現(xiàn)的影響信號傳輸完整性的諸多因素進(jìn)行分析,并做出多種預(yù)防性措施。從主要器件選型、PCB板布局布線、疊層設(shè)計(jì)以及在PCB板設(shè)計(jì)制造中結(jié)合IBIS模型與Cadence仿真軟件對所遇到的差分對的反射問題進(jìn)行分析與研究。在重點(diǎn)分析差分傳輸線理論的基礎(chǔ)上選取高速接口處的1組差分對提取拓?fù)浣Y(jié)構(gòu),并對其在進(jìn)行端接匹配前后接收的信號進(jìn)行分析及眼圖仿真。實(shí)驗(yàn)結(jié)果表明:采用ESD芯片進(jìn)行端接處理后所接收的眼圖波形變得整齊,抖動(dòng)與尖峰明顯減少。目前采取的措施可以確保實(shí)際存儲(chǔ)設(shè)備工作的可靠性,為工程實(shí)踐提供有益的借鑒。

雷達(dá)回波;存儲(chǔ)測試;信號完整性;差分對;IBIS模型

0 引 言

雷達(dá)技術(shù)向高分辨率方向發(fā)展,增加了雷達(dá)回波的信息量,對雷達(dá)數(shù)據(jù)記錄設(shè)備的速度提出更高要求,同時(shí)對存儲(chǔ)設(shè)備PCB板的信號傳輸也提出更高要求[1]。本文研究設(shè)計(jì)了高速雷達(dá)回波信號記錄設(shè)備,主要針對機(jī)載雷達(dá)探測其他飛行器飛行中的各種參數(shù)并進(jìn)行采集與加密存儲(chǔ)。返回陸地后經(jīng)高速接口進(jìn)行數(shù)據(jù)回讀分析。

對于高速電路有兩個(gè)方面的含義:1)從頻率角度考慮,數(shù)字電路的頻率達(dá)到或是超過40~50MHz,且工作于此頻率之上的電路占整個(gè)系統(tǒng)的1/3。2)考慮信號的上升與下降時(shí)間,若某信號的上升時(shí)間小于6倍信號傳輸延時(shí)即認(rèn)為是高速信號[2]。本文所采集的激光雷達(dá)回波信號的最大頻率為40MHz,采樣頻率為信號頻率的4~10倍,數(shù)據(jù)采用的是LVDS低壓差分形式進(jìn)行傳輸。對于高速的雷達(dá)回波信號采集存儲(chǔ)設(shè)備,在PCB板的設(shè)計(jì)過程中需要對采集、存儲(chǔ)、回讀過程中信號傳輸?shù)耐暾赃M(jìn)行分析,以最大程度保證信號傳輸?shù)牟皇д嫘訹3-4]。本文針對此問題在系統(tǒng)設(shè)計(jì)過程中主要從PCB布局布線、疊層設(shè)計(jì)、差分對設(shè)計(jì)等方面進(jìn)行研究,并對差分對信號提出合理的端接,保證數(shù)據(jù)傳輸?shù)耐暾浴?/p>

1 系統(tǒng)結(jié)構(gòu)

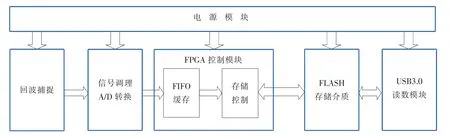

系統(tǒng)結(jié)構(gòu)由回波捕捉與信號調(diào)理、主控存儲(chǔ)、讀數(shù)接口和電源等模塊組成。回波捕捉與信號調(diào)理模塊完成有效信號的捕捉、模數(shù)轉(zhuǎn)換、外部數(shù)據(jù)的匹配、隔離等工作;存儲(chǔ)模塊工作是在主控芯片控制下經(jīng)數(shù)據(jù)緩存電路存入FLASH陣列中。讀數(shù)接口模塊用于設(shè)備采集后的數(shù)據(jù)回讀;電源模塊給其他模塊提供穩(wěn)定、精準(zhǔn)的各等級電壓。系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

圖1 系統(tǒng)結(jié)構(gòu)框圖

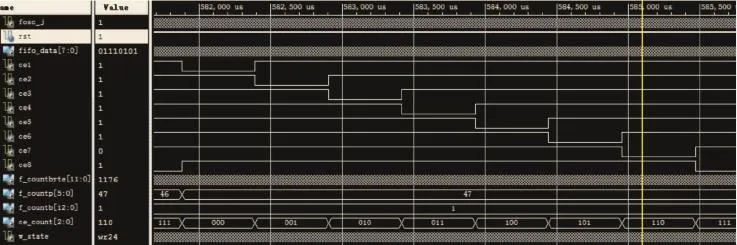

系統(tǒng)上電后各個(gè)模塊完成復(fù)位操作,回波捕捉電路捕捉到有效的回波信號后使系統(tǒng)觸發(fā),回波信號經(jīng)信號調(diào)理電路,之后進(jìn)入模數(shù)轉(zhuǎn)換部分。其輸出類型為LVDS信號,經(jīng)接口芯片轉(zhuǎn)換為TTL信號,經(jīng)FPGA內(nèi)部調(diào)用的FIFO實(shí)現(xiàn)高速數(shù)據(jù)緩沖,并在其控制下存儲(chǔ)至FLASH介質(zhì)中。記錄結(jié)束后通過USB3.0讀數(shù)接口將數(shù)據(jù)回讀分析,繼而實(shí)現(xiàn)了雷達(dá)回波數(shù)據(jù)從采集到高速傳輸,存儲(chǔ)以及回讀等功能。數(shù)據(jù)高速存儲(chǔ)使用流水線的方式存入FLASH芯片,系統(tǒng)邏輯控制時(shí)序仿真圖如圖2所示。

圖2 系統(tǒng)邏輯控制時(shí)序仿真圖

2 信號完整性研究

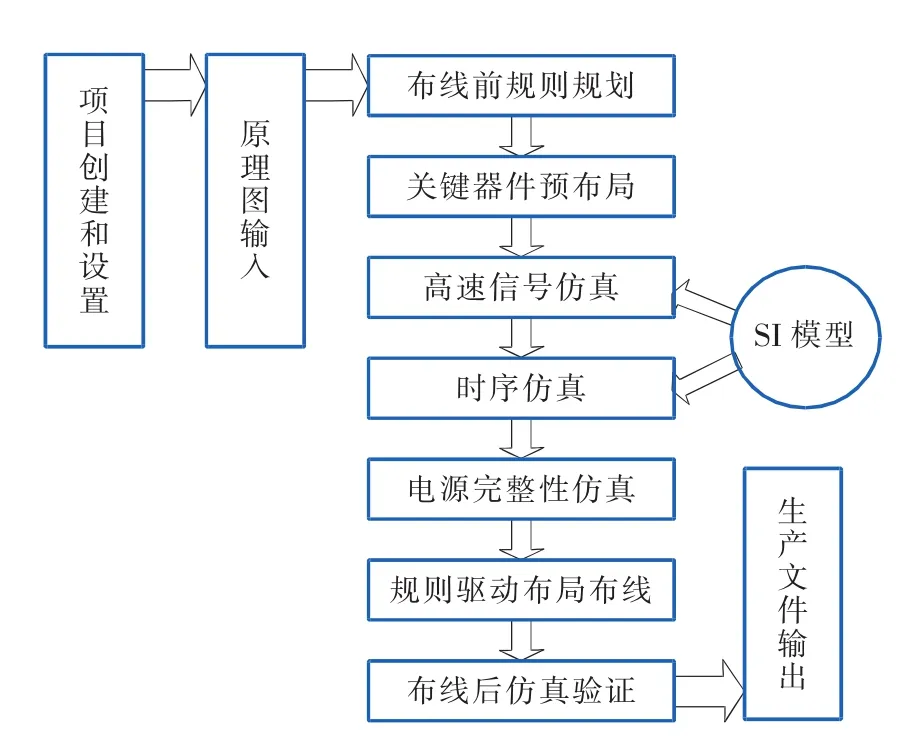

PCB板的設(shè)計(jì)主要是從狹義的信號完整性(SI)、電源完整性(PI)和電磁兼容性(EMC)3個(gè)角度出發(fā)[3,5]。從原理圖的設(shè)計(jì),元器件的封裝與布局布線,電路板的疊層與參數(shù)等方面統(tǒng)籌協(xié)調(diào),綜合規(guī)劃。本存儲(chǔ)系統(tǒng)對體積有所要求,導(dǎo)致單位面積PCB板上的元件很多,布局布線的密度也很大。在PCB板的設(shè)計(jì)制造過程中信號完整性的思想始終貫穿其中[6]。具體的PCB設(shè)計(jì)過程,如圖3所示。

圖3 PCB設(shè)計(jì)過程

2.1 主要器件選型

對于高速系統(tǒng)的設(shè)計(jì),對主要器件的選型從高速信號傳輸角度也需要進(jìn)行全面考慮。在滿足系統(tǒng)設(shè)計(jì)與成本要求的前提下系統(tǒng)的中央控制模塊所采用的可編程邏輯器件為Xilinx公司的Spartan II系列的XC2S50(XCR3256),它擁有1728個(gè)宏單元,大大增強(qiáng)了系統(tǒng)的可擴(kuò)展性。模數(shù)轉(zhuǎn)換器選取具有雙倍速率低壓差分信號輸出的 14位 65MSPS的 ADS6142,在速度與性能上都滿足設(shè)計(jì)要求。讀數(shù)模塊中USB芯片為CYUSB3014,另外還加有對接口進(jìn)行保護(hù)的ESD防護(hù)芯片。

2.2 PCB板的布局布線

在進(jìn)行仿真和布線之前要先進(jìn)行預(yù)布局,即按照一般的外形因素、機(jī)械限制和慣例預(yù)先確定關(guān)鍵元器件的位置。器件的布局決定了布線的大致走向和結(jié)構(gòu)、電源和地平面的分割,以及對EMI和噪聲的控制情況[4,7]。PCB布局堅(jiān)持以下原則:按照信號流動(dòng)的方向布局各功能模塊在PCB板上的位置;在各功能模塊中以核心器件為中心,將器件歸類布局,盡量使其均勻、整齊、緊湊地圍繞著核心器件,并使元器件之間的引線與連線最簡化;高頻和低頻電路相隔離,模擬與數(shù)字電路相隔離,且數(shù)字器件盡量集中放置以減少走線長度;晶振盡量靠近其驅(qū)動(dòng)器件,高頻去耦電容放在芯片電源引腳附近[8]。

設(shè)計(jì)的 PCB板尺寸為 56 mm×82 mm,高速數(shù)據(jù)傳輸系統(tǒng)器件較少,先確定LVDS轉(zhuǎn)換芯片DS92LV090A和USB3.0芯片CYUSB3014的位置,然后依次放置擴(kuò)展口接插件、FLASH、電源管理芯片、配置芯片,晶振和去耦電容等。在進(jìn)行前仿真過程中,根據(jù)線長和結(jié)構(gòu)優(yōu)化調(diào)整布局。

2.3 PCB板的疊層設(shè)計(jì)

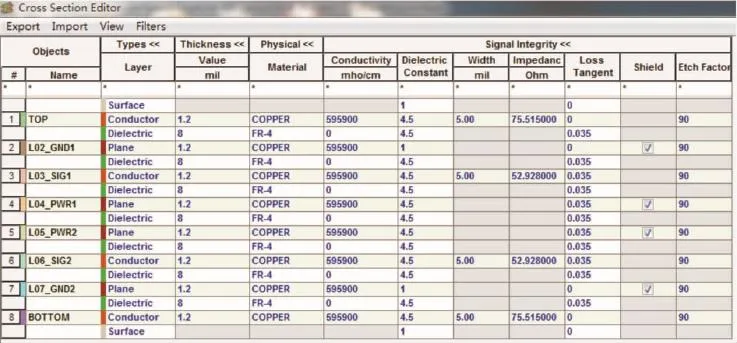

設(shè)計(jì)合理的PCB疊層可以使系統(tǒng)的EMC性能極大改善,同時(shí)會(huì)使回路的輻射效應(yīng)大大減弱。穩(wěn)定可靠的電源平面為信號提供理想的返回路徑,使之減少環(huán)路面積[9]。多層板應(yīng)用于高速數(shù)字系統(tǒng)設(shè)計(jì)中主要考慮其板層結(jié)構(gòu)設(shè)計(jì)、介質(zhì)選擇和電源/地層的設(shè)計(jì)。參考有關(guān)手冊和設(shè)計(jì)經(jīng)驗(yàn),本系統(tǒng)采用的PCB疊層設(shè)置如圖4所示。

圖4 PCB疊層參數(shù)設(shè)置

系統(tǒng)采用8層PCB設(shè)計(jì),總厚度1.67mm。將中間的兩個(gè)信號層置于地層與電源層之間,頂部與底部的信號層與底層相鄰。表層走線為微帶線和內(nèi)層走線為帶狀線。loss tangent是介質(zhì)損耗因數(shù),其類型包括表層、信號層、電介質(zhì)和電源平面4種。信號層和電源/地的材料選擇COPPER,厚度設(shè)為0.03mm,絕緣層設(shè)為FR-4材料,通過改變絕緣層的厚度達(dá)到期望的各層阻抗和PCB厚度。PCB頂層和底層的阻抗最終設(shè)為75.515 Ω,中間信號層的阻抗設(shè)為52.928Ω。

2.4 差分對設(shè)計(jì)

如今高速數(shù)字信號頻率大大提高,邊沿十分陡峭,互聯(lián)結(jié)構(gòu)中各種寄生參數(shù)效應(yīng)也越發(fā)明顯[5],只有把信號從發(fā)送端到達(dá)接收端的傳輸看作是消耗一定時(shí)間的“動(dòng)態(tài)過程”,把高速電路中的互聯(lián)結(jié)構(gòu)當(dāng)作傳輸線對待,并從電磁波傳播的角度來理解信號的傳播[10-11]。在時(shí)鐘頻率和噪聲隔離要求較高的情況下,常使用差分傳輸線。在差分互聯(lián)模式下,成對擺放著兩條電壓和電流大小相等但極性相反的傳輸線,如圖5所示。兩個(gè)信號從驅(qū)動(dòng)端出發(fā),到達(dá)接收端時(shí)根據(jù)兩信號的數(shù)值差判斷電平高低。

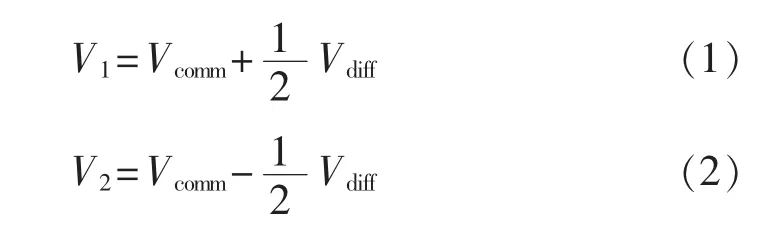

理想時(shí),兩信號可用共模分量以及差分分量形式[5]表示:

其中Vcomm表示共模分量,Vdiff表示差分分量。兩條信號傳輸過程的環(huán)境是相同的,所以接收端有很好的共模抑制能力,若只考慮其中的差分分量,則兩個(gè)信號可記為

式中 V1diff、V2diff分別表示第 1個(gè)信號和第 2個(gè)信號的差分分量,是兩條電壓相等極性相反的信號線,其每條差分分量的阻抗都是奇模阻抗Zodd。假設(shè)由差分分量引起的電流為Idiff,則Zodd可表示為

即定義差分阻抗Zdiff為

差分阻抗(或特性阻抗,兩條差分傳輸線之間的阻抗)為單條傳輸線對地特性阻抗的2倍[12]。通常,差分對信號間距越近,其特性阻抗越小[13](其他因素保持不變的條件下)。常使用的差分對的特性阻抗為100Ω,有時(shí)也用75Ω。

差分對中的兩個(gè)單端信號傳輸?shù)絺鬏斁€末端時(shí),如果沒有端接信號可能發(fā)生反射,接收端波形可能會(huì)產(chǎn)生振鈴。對差分信號和共模信號同時(shí)端接是減小振鈴現(xiàn)象最理想的方式,常用的端接方式有T型和π型端接,如圖6所示。

圖6 差分對端接方法

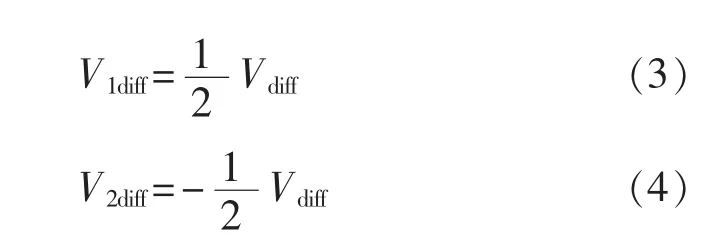

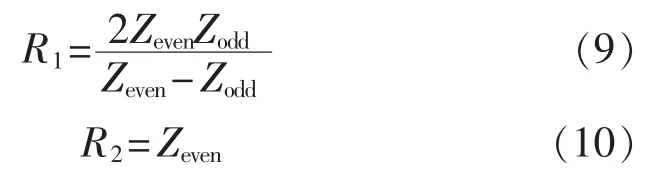

圖中電阻R1和R2分別為

兩個(gè)R1串聯(lián)作用在差分信號上,剛好等于差分阻抗。兩個(gè)R1并聯(lián)再與R2串聯(lián)作用在共模信號上,阻值為Zeven/2,恰好為共模阻抗的值。

π型端接中電阻R1和R2分別為

那么差分信號感受到的阻抗為R1//2R2=2Zodd,共模信號感受到的阻抗為R2/2=Zodd/2,這兩種方法對差分信號和共模信號皆有端接作用。

圖7 USB3.0接口與CYUSB3014之間拓?fù)浣Y(jié)構(gòu)

差分對設(shè)計(jì)的一個(gè)基本要求就是盡量保持等長平行布線,如果繞線處不得不改變間距,那么盡量在小范圍內(nèi)改變間距,這樣做的目的是使差分對兩條傳輸線的延時(shí)相等,使差分信號畸變變小,并減少共模噪聲引起的抖動(dòng)。由于差分信號在傳輸過程中,兩條路徑上遭遇的噪聲干擾完全一樣,這樣其相互產(chǎn)生的電磁場將相互抵消,所以比單端傳輸在減小地線回路噪聲與外部噪聲上更有優(yōu)勢。需要注意的是,在差分對與單端線間距較小的情況下,單端線對差分信號的串?dāng)_噪聲依然較大,因此,即便是使用差分傳輸,最有效的減小串?dāng)_的方法仍然是盡量拉開差分對與攻擊信號的間距。對于差分對中一條走線的返回電流路徑,參考平面中的返回電流占總電流的90%左右,另一條走線上的返回電流約占10%,因此參考平面對于差分對同樣重要。

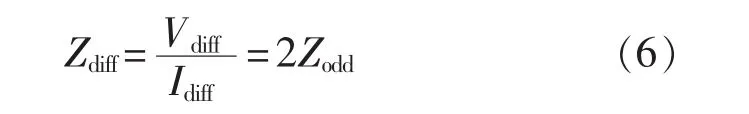

綜上,針對差分對特性阻抗、差分互聯(lián)的反射與端接、串?dāng)_等的分析,進(jìn)行差分對設(shè)計(jì)。根據(jù)相關(guān)數(shù)據(jù)手冊建議,信號線阻抗為90Ω(±7%)的差分值[12]。本設(shè)計(jì)中差分對的特性阻抗設(shè)為90 Ω,線寬設(shè)為0.28 mm,走線間距設(shè)為0.2 mm,同時(shí)在布線時(shí)將差分信號線完全與接地層鄰近,盡量遠(yuǎn)離其他信號線,減少串?dāng)_。本文中差分對設(shè)計(jì)的重點(diǎn)在于USB接口處,其中USB接口處差分信號接收端反射現(xiàn)象并不明顯,因此在USB3.0接口與CYUSB3014之間接入ESD芯片,防止靜電干擾,減少外部噪聲。

3 仿真實(shí)驗(yàn)

3.1 SI模型分配

圖8 波形及眼圖仿真

在進(jìn)行仿真前需要對元器件進(jìn)行模型分配,這里采用(input/output buffer information specification,IBIS)模型仿真。只有IC類有源器件能夠分配IBIS模型,DISCRETE無源器件和IO類輸入/輸出器件沒有IBIS模型。IBIS定義引腳與哪一個(gè)緩沖模型相關(guān),這里采用手動(dòng)分配模型方式,分配給元器件的信號模型名不必與Allegro元器件名匹配[14]。如果模型庫中沒有某個(gè)器件的IBIS模型,則需要親自創(chuàng)建,確定該器件的引腳寄生參數(shù)和各個(gè)引腳的輸入輸出特性。

USB3.0接口與CYUSB3014之間的3對差分信號線起著連接USB3.0芯片與上位機(jī)的關(guān)鍵作用,這些差分對信號能否準(zhǔn)確傳輸對整個(gè)高速數(shù)據(jù)存儲(chǔ)系統(tǒng)起著重要作用,因此必需考慮這些差分信號在傳輸過程中的完整性問題。此處選取USB3.0接口處的SSRX+和SSRX-差分對提取拓?fù)浣Y(jié)構(gòu),并按照前面分析進(jìn)行相關(guān)參數(shù)設(shè)置,拓?fù)浣Y(jié)構(gòu)如圖7所示。

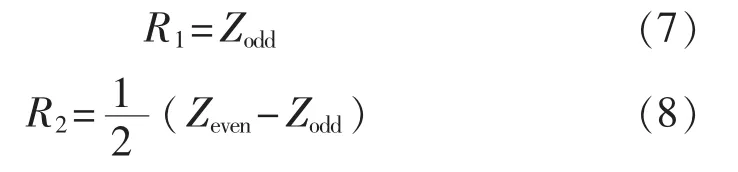

3.2 眼圖仿真

眼圖通過余暉方式積累疊加,然后顯示采集信號的比特位[9]。對高速差分互聯(lián)通常使用眼圖來評估信號的傳輸,從“眼睛”睜開的大小(高度及寬度)能看出接收信號的誤碼率相對大小,“眼睛”睜開得越大,接收的出錯(cuò)概論越小。下面利用Cadence軟件的Allegro PCB SI部件對差分對進(jìn)行仿真分析。

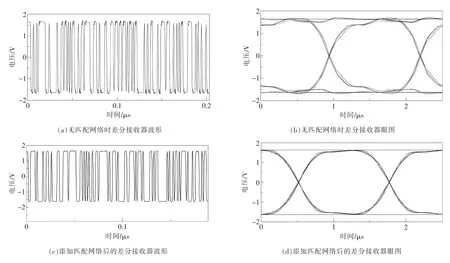

圖 7拓?fù)浣Y(jié)構(gòu)中,USB3.0接口為驅(qū)動(dòng)端,CYUSB3014為接收端。對驅(qū)動(dòng)端激勵(lì)信號進(jìn)行設(shè)置,激勵(lì)形式為Custom,頻率為400 MHz,采用時(shí)鐘同步方式。傳輸數(shù)據(jù)設(shè)為1024字節(jié)隨機(jī)數(shù)。設(shè)置好參數(shù)后,開始仿真。圖8為在添加ESD芯片SP3010-04UTG前后的仿真結(jié)果圖。在仿真結(jié)果中只顯示CYUSB3014接收到的差分信號,圖8(a)、圖8(b)中接收器所接收到的信號尖峰明顯,說明所受到的抖動(dòng)與外部噪聲對信號有較大干擾,眼圖波形失真嚴(yán)重。而進(jìn)行端接匹配之后,如圖8(c)、圖8(d)所示,無論從接收到的波形的平整程度還是眼圖的優(yōu)化結(jié)果都可以明顯觀察到尖峰與抖動(dòng)減小,足以說明信號得到完整的傳輸。

4 結(jié)束語

本文設(shè)計(jì)了高速雷達(dá)回波信號存儲(chǔ)設(shè)備,針對在系統(tǒng)設(shè)計(jì)過程中可能出現(xiàn)的影響信號傳輸完整性的諸多因素進(jìn)行分析。主要包括核心器件的選型,PCB板的布局布線,疊層以及差分對的設(shè)計(jì)。在整個(gè)PCB板的設(shè)計(jì)制造過程中信號完整性的思想始終貫穿其中。在重點(diǎn)分析差分傳輸線理論的基礎(chǔ)上選取高速接口處的1組差分對提取拓?fù)浣Y(jié)構(gòu),并對該差分對在進(jìn)行端接匹配前后進(jìn)行分析及眼圖仿真。實(shí)驗(yàn)結(jié)果表明:采用ESD芯片進(jìn)行端接處理后波形變得整齊,抖動(dòng)與外部噪聲明顯減少,在PCB設(shè)計(jì)過程采用的多種預(yù)防性措施保證系統(tǒng)傳輸信號的完整,使存儲(chǔ)設(shè)備穩(wěn)定工作。

[1]任敏.基于FPGA的雙通道機(jī)載數(shù)據(jù)存儲(chǔ)系統(tǒng)設(shè)計(jì)[D].太原:中北大學(xué),2015.

[2]王澤強(qiáng).高速電路之信號回流路徑分析[J].現(xiàn)代電子技術(shù),2013,36(1):155-157,160.

[3]周潤景,蘇良碧.Cadence高速電路板設(shè)計(jì)與仿真[M].4版.北京:電子工業(yè)出版社,2011:97-105.

[4]王雪茹.信號完整性對雷達(dá)對抗系統(tǒng)的影響[D].西安:西安電子科技大學(xué),2014.

[5]郁昊,葉勇.基于雷達(dá)處理機(jī)高速信號的信號完整性設(shè)計(jì)[J].測控技術(shù),2012,31(3):128-130,134.

[6]楊少博,裴東興,岳孝忠.高速數(shù)據(jù)采集系統(tǒng)中USB3.0數(shù)據(jù)傳輸接口設(shè)計(jì)[J].電子器件,2015,38(4):912-916.

[7]劉定坤.差分對對信號完整性的分析[J].電子制作,2013(11):162.

[8]李小榮.高速數(shù)模混合電路信號完整性分析與PCB設(shè)計(jì)[D].杭州:杭州電子科技大學(xué),2010.

[9]王祥.信號完整性在高速PCB設(shè)計(jì)中的應(yīng)用[D].上海:復(fù)旦大學(xué),2013.

[10]ZHOU S L,GUAN Y L,TANG X K.Signal integrity analysis of high-speed signal connector USB3.0[J].Advanced Materials Research,2013(760):320-324.

[11]陳蘭兵.Cadence高速電路設(shè)計(jì):Allegro Sigrity SI/PI/EMI設(shè)計(jì)指南[M].北京:電子工業(yè)出版社,2014:171-178.

[12]沈立,朱來文,陳宏偉,等.高速數(shù)字設(shè)計(jì)[M].北京:電子工業(yè)出版社,2010:213-227.

[13]于爭.信號完整性揭秘:于博士SI設(shè)計(jì)手記[M].北京:機(jī)械工業(yè)出版社,2013:91-99.

[14]田廣錕,范如東.高速電路PCB設(shè)計(jì)與EMC技術(shù)分析[M].北京:電子工業(yè)出版社,2011:41-49.

(編輯:李妮)

Research on signal integrity of radar echo storage equipment

FAN Guohao1,2,YANG Shaobo1,2,ZHANG Yanbing1,2,MA Tiehua1,2

(1.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China;2.Key Laboratory of Instrumentation Science&Dynamic Measurement of Ministry of Education,North University of China,Taiyuan 030051,China)

A high-speed radar echo storage system was designed and in view of the many factors that may affect the signal transmission integrity in the system design process,a variety of preventive measures were taken.From the main component selection,PCB locating and wiring,stack design and PCB design and manufacturing,IBIS model and Cadence simulation software were combined to analyze and study the problems of signal integrity differential pair reflection encountered in the radar echo storage system.On the basis of analysis on difference transmission line theory,a group of differential pair at high-speed interface was selected to extracts its topological structure.Analysis and eye pattern simulation were conducted for the signals received before and after termination matching.Experimental results show that using ESD chip for termination processing can reduce the jitter and external noise and neat the eye pattern.These measures can ensure reliability of the actual storage device and provide a useful reference for engineering practices.

radar echo;storage test;signal integrity;difference pair;IBIS model

A

:1674-5124(2017)02-0139-06

10.11857/j.issn.1674-5124.2017.02.028

2016-05-10;

:2016-08-30

范國浩(1991-),男,山西汾陽市人,碩士研究生,專業(yè)方向?yàn)橹悄軆x器與動(dòng)態(tài)測試。

張艷兵(1973-),男,山西運(yùn)城市人,副教授,碩士生導(dǎo)師,研究方向?yàn)閯?dòng)態(tài)測控與智能儀器、計(jì)算機(jī)控制。