多通道同步時(shí)鐘技術(shù)

涂正林,趙晨光

(中國(guó)船舶重工集團(tuán)公司第723研究所,揚(yáng)州 225001)

?

多通道同步時(shí)鐘技術(shù)

涂正林,趙晨光

(中國(guó)船舶重工集團(tuán)公司第723研究所,揚(yáng)州 225001)

隨著陣列天線(xiàn)應(yīng)用的發(fā)展,通訊、儀表、雷達(dá)、電子戰(zhàn)等行業(yè)已不再滿(mǎn)足于單通道高速模數(shù)轉(zhuǎn)換器(ADC)的使用,因此多通道同步采樣技術(shù)得到長(zhǎng)足發(fā)展。基于ADI公司主流器件搭建了一個(gè)可行的多通道同步采樣架構(gòu)。

多通道;同步時(shí)鐘;陣列采樣

0 引 言

隨著陣列數(shù)字信號(hào)處理技術(shù)的發(fā)展,單通道模數(shù)轉(zhuǎn)換器(ADC)采樣已不能滿(mǎn)足通訊、儀表、雷達(dá)、電子戰(zhàn)等行業(yè)需求,這促進(jìn)了多通道高速ADC同步采樣技術(shù)的長(zhǎng)足發(fā)展與進(jìn)步。這項(xiàng)技術(shù)面臨的最大挑戰(zhàn)除ADC的采樣速度和接口速度匹配,還有如何控制這些先進(jìn)的ADC同步采樣、同步傳輸、同步存儲(chǔ)以及數(shù)據(jù)重構(gòu)等。本文基于TI公司高速器件搭建了一個(gè)可行的多通道同步采樣架構(gòu)。

1 多通道同步采樣的3個(gè)關(guān)鍵要素

1.1 采樣時(shí)鐘的同步

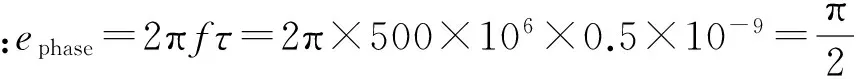

一般陣列時(shí)鐘以功分器組陣,它的優(yōu)點(diǎn)是組陣方案簡(jiǎn)單易行,缺點(diǎn)是若陣面孔徑較大,則體積重量會(huì)隨之增大,對(duì)時(shí)鐘源功率也要求較高。如果ADC采用壓控振蕩器(VCO)+鎖相環(huán)(PLL)的獨(dú)立時(shí)鐘,比如ADI公司的LMX2531、LMX2582等器件,優(yōu)點(diǎn)是體積小,重量輕,時(shí)鐘雜散和相噪控制較好;缺點(diǎn)則是每個(gè)采樣板之間時(shí)鐘相對(duì)獨(dú)立,不能同步[1]。各AD板時(shí)鐘之間相位差是隨機(jī)的,最壞的情況是,某2個(gè)子陣時(shí)鐘相差π,此時(shí)2個(gè)時(shí)鐘延時(shí)達(dá)到最大值。對(duì)于1GHz采樣時(shí)鐘,時(shí)間延時(shí):

根據(jù)存在誤差時(shí)陣列天線(xiàn)方向圖公式:

(1)

由上式可以推導(dǎo)出以下幾種情況[3]:

當(dāng)存在幅相誤差時(shí),陣列天線(xiàn)增益損失:

(2)

當(dāng)各陣元幅度加權(quán)相等時(shí),波束指向誤差方差:

(3)

當(dāng)存在相位誤差時(shí),波束平均旁瓣電平:

(4)

從公式(2)可知,當(dāng)陣元數(shù)N較大時(shí),陣列天線(xiàn)增益損耗只與相位誤差成正比;從公式(3)可知,波束指向誤差正比于相位誤差,但與陣元數(shù)成反比;從公式(4)可知,旁瓣電平隨相位誤差的增大而抬高。

從以上計(jì)算可以看到,在中頻頻率更高的場(chǎng)合,即使時(shí)鐘間延時(shí)非常微小,相位差都會(huì)導(dǎo)致后端很大的通道間相位采樣誤差,而相位誤差增大會(huì)導(dǎo)致數(shù)字波束增益下降,旁瓣惡化,主波束指向偏離。

1.2 系統(tǒng)參考信號(hào)的同步

在各通道時(shí)鐘同步的前提下,系統(tǒng)同步參考信號(hào)在多通道同步采樣系統(tǒng)中十分重要,它也是周期信號(hào),用于ADC內(nèi)部多幀時(shí)鐘的前沿對(duì)準(zhǔn)。系統(tǒng)同步參考信號(hào)不僅讓多通道同步采樣系統(tǒng)進(jìn)行時(shí)鐘前沿同步,同時(shí)也實(shí)現(xiàn)了整個(gè)ADC系統(tǒng)的同步數(shù)據(jù)傳輸。如果陣列存儲(chǔ)系統(tǒng)沒(méi)有收到同步參考信號(hào),各個(gè)通道采集的數(shù)據(jù)將被認(rèn)為無(wú)效而忽略。因此,同步參考信號(hào)將對(duì)系統(tǒng)陣列數(shù)據(jù)采集、同步傳輸和存儲(chǔ)起著關(guān)鍵作用。外部系統(tǒng)參考信號(hào)用于對(duì)齊所有的內(nèi)部時(shí)鐘相位和本地多幀時(shí)鐘到一個(gè)特定的采樣時(shí)鐘邊緣,允許在一個(gè)系統(tǒng)中的多個(gè)設(shè)備同步,并最大限度地減少時(shí)間和定位的不確定性。

1.3 數(shù)據(jù)傳輸?shù)耐?/p>

高速ADC器件都有SYNC*輸入引腳,它是ADC的一個(gè)對(duì)外接口,用于數(shù)據(jù)傳輸同步,它的時(shí)序產(chǎn)生也是依賴(lài)采樣時(shí)鐘和SYSREF,由現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)統(tǒng)一觸發(fā)產(chǎn)生。有了這個(gè)同步輸入引腳,使大規(guī)模ADC組陣成為可能。

2 多通道時(shí)鐘和控制設(shè)計(jì)與分析

早期時(shí)鐘同步使用功分器和射頻電纜,通過(guò)調(diào)整射頻電纜長(zhǎng)度保證各通道時(shí)鐘同步,再以SYSREF進(jìn)行采樣時(shí)鐘前沿對(duì)齊。其基本框圖見(jiàn)圖1。

圖1 早期多通道同步采樣

但這種方法只適用于通道較少的情況,而且時(shí)鐘源功率要求較大,同步精度不高,調(diào)試需要矢量分析網(wǎng)絡(luò)、高精度等相電纜,調(diào)試維護(hù)工作量較大,遇到差分時(shí)鐘要求的ADC器件,還需使用類(lèi)似ADT1-1WT等射頻變壓器轉(zhuǎn)換。由于射頻變壓器的個(gè)體差異,各通道原本同步的時(shí)鐘會(huì)再次失配。 隨著電子器件工作頻段的不斷提高,當(dāng)前相當(dāng)數(shù)量的高速ADC時(shí)鐘都可以由集成電路直接提供,并且現(xiàn)在高速ADC支持多種類(lèi)型的時(shí)鐘信號(hào),包括LVDS時(shí)鐘信號(hào)。本文選用TI公司推出的LMX2581鎖相時(shí)鐘源、高速ADC芯片ADS54J40和多通道時(shí)鐘分配器LMK01010搭建了1個(gè)多通道同步采樣系統(tǒng)框架。

LMK01010是TI公司LMK01000系列高速時(shí)鐘分配芯片,它具有以下優(yōu)點(diǎn):

(1) 8路獨(dú)立可編程LVDS時(shí)鐘,支持0~1 600 MHz;

(2) 全局時(shí)鐘輸出同步,支持多片時(shí)鐘同步;

(3) 30 fs時(shí)鐘抖動(dòng)@20 MHz;

(4) 芯片內(nèi)任一時(shí)鐘輸出都可以獨(dú)立完成延時(shí)、移相、分頻等操作;

(5) 最多可同時(shí)為8個(gè)高速ADC提供等頻率(分頻)同步高速時(shí)鐘。

其基本框圖如圖2所示。

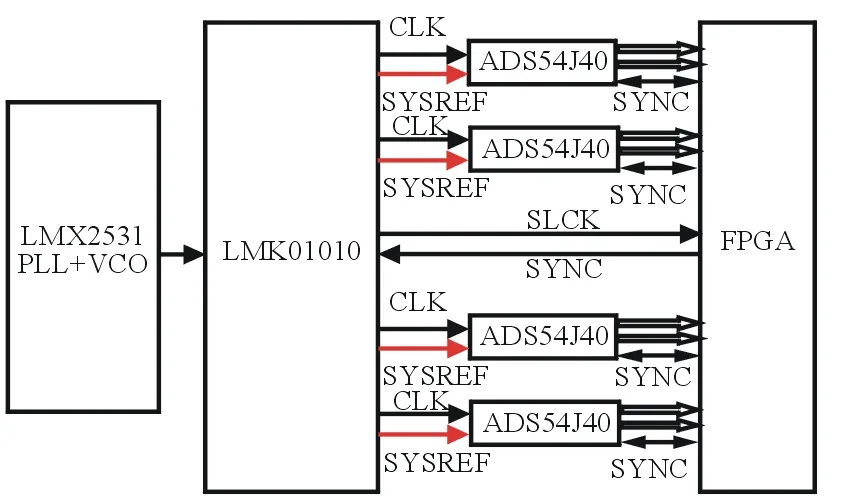

圖3是以單片LMK01010為核心的多通道ADC同步采樣系統(tǒng),其中LMX2531作為L(zhǎng)MK01010唯一的驅(qū)動(dòng),為整個(gè)同步采樣系統(tǒng)提供統(tǒng)一的時(shí)鐘源;ADS54J40采樣率1 GSPS并支持LVDS時(shí)鐘。FPGA為AD54J40經(jīng)過(guò)直接數(shù)字控制器(DDC)后的采樣數(shù)據(jù)分配傳遞給后端的信號(hào)存儲(chǔ)分析系統(tǒng)。

圖2 LMK01010框架簡(jiǎn)圖

圖3 單片LMK01010為核心的多通道采樣系統(tǒng)

然而在某些場(chǎng)合,幾路ADC同步采樣并不能滿(mǎn)足對(duì)數(shù)量龐大的傳感器系統(tǒng)采樣分析的需求。因此,對(duì)于大規(guī)模通道傳感器場(chǎng)合,可以充分利用LMK01010芯片中SYNC*全局時(shí)鐘控制信號(hào)實(shí)現(xiàn)多片時(shí)鐘分配芯片的組合,驅(qū)動(dòng)更大數(shù)量的ADC進(jìn)行同步采樣。

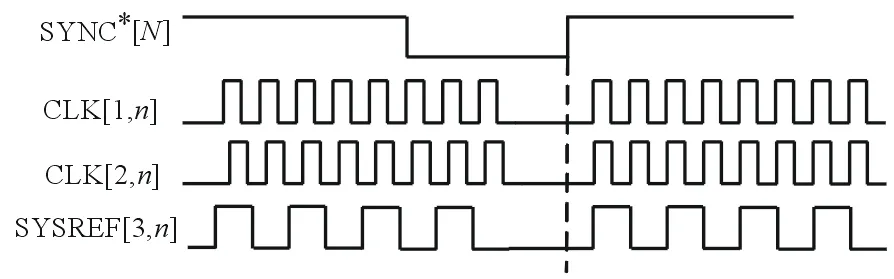

圖4中每一個(gè)LMK01010都有一個(gè)獨(dú)立的時(shí)鐘源,它們分配時(shí)鐘的同步控制都由高精度前沿正對(duì)的SYNC*[N]來(lái)實(shí)現(xiàn)。同步時(shí)序如圖5所示。

圖4 多片LMK01010架構(gòu)的多通道同步采樣系統(tǒng)

圖5 多片時(shí)鐘分配同步時(shí)序

圖5中,SYNC*[N]抽取任意一路時(shí)鐘同步信號(hào),CLK[1,n]為第1片LMK01010芯片的第n路時(shí)鐘輸出(n=1,3,5,7;n=2,4,6,8分頻后作為SYSREF使用);CLK[2,n]為第2片LMK01010芯片的第n路時(shí)鐘輸出;SYSREF[3,n]為第3片LMK01010芯片的系統(tǒng)參考信號(hào)。這樣選取時(shí)鐘邏輯進(jìn)行測(cè)量比較,能客觀反映多片LMK01010芯片系統(tǒng)中由SYNC*控制的同步情況。

相對(duì)于高頻的時(shí)鐘信號(hào),頻率低得多的視頻信號(hào)SYNC*[N]更容易實(shí)現(xiàn)前沿正對(duì)。但隨著ADC陣列板的數(shù)量不斷增加,SYNC*[N]控制線(xiàn)的長(zhǎng)度差也會(huì)越來(lái)越大,這個(gè)長(zhǎng)度差對(duì)SYNC*延時(shí)影響根據(jù)傳輸線(xiàn)介電常數(shù)ε的不同而不同,如表1所示。

選取介電常數(shù)2.3進(jìn)行計(jì)算,信號(hào)傳輸延時(shí)的計(jì)算公式為:

(5)

假設(shè)最長(zhǎng)傳輸線(xiàn)與最短傳輸線(xiàn)的長(zhǎng)度差為1.5 m,那么它們之間SYNC*傳輸時(shí)間差為7.58 ns。這樣的時(shí)間差是無(wú)法讓板間LMK01010的時(shí)鐘同步的,SYNC*信號(hào)在傳輸線(xiàn)中的延遲補(bǔ)償設(shè)計(jì)也必須重點(diǎn)設(shè)計(jì)。根據(jù)上述計(jì)算,知道在一個(gè)強(qiáng)調(diào)高度同步的采樣系統(tǒng)中,首先選擇好同步信號(hào)傳輸線(xiàn),保證其電長(zhǎng)度誤差在設(shè)計(jì)范圍;如果實(shí)際長(zhǎng)度之間存在誤差,還可以根據(jù)時(shí)鐘前沿實(shí)際測(cè)量結(jié)果,通過(guò)LMK01010的時(shí)鐘延遲通道或者移相,對(duì)時(shí)鐘同步進(jìn)行微調(diào)。

表1 介電常數(shù)延遲對(duì)照表

LMK01010不僅可以在單板中為ADC及其外部接口提供高精度的同步時(shí)鐘,還可以應(yīng)用于ADC的組陣。在設(shè)計(jì)指標(biāo)允許范圍內(nèi),通過(guò)SYNC*管腳將LMK01010組陣,再通過(guò)其8路時(shí)鐘輸出將ADC同步組陣,以滿(mǎn)足大陣面場(chǎng)合的應(yīng)用需求。只要對(duì)SYNC*前沿進(jìn)行精心設(shè)計(jì),并輔以芯片內(nèi)部移相和延遲功能,ADC陣面可以進(jìn)一步擴(kuò)展。以LMK01010為核心的時(shí)鐘設(shè)計(jì)方案具有體積小、重量輕、功耗低、工作頻帶寬、設(shè)計(jì)一致性好、擴(kuò)展能力強(qiáng)、生產(chǎn)調(diào)試方便、陣元微調(diào)能力突出等優(yōu)點(diǎn)。

3 結(jié)束語(yǔ)

多通道同步采樣時(shí)鐘是系統(tǒng)同步的先決條件,設(shè)計(jì)方案不同,選取器件不同,設(shè)計(jì)方法也有不同。現(xiàn)在各大公司廠家根據(jù)設(shè)計(jì)師要求提供了各種不同的時(shí)鐘分配芯片,方便電子設(shè)計(jì)師的設(shè)計(jì)和調(diào)試,同時(shí)也為多通道采樣系統(tǒng)的小型化、實(shí)用化提供了技術(shù)支持。類(lèi)似系統(tǒng)可以廣泛應(yīng)用于多輸入多輸出系統(tǒng)、電磁環(huán)境采集與檢測(cè)、雷達(dá)電子戰(zhàn)、陣列聲納等領(lǐng)域。

[1] 孫進(jìn)才,朱維杰.信號(hào)相位匹配原理及其應(yīng)用[M].西安:西北工業(yè)大學(xué)出版社,2007.

[2] 畢增軍,徐晨曦,張賢志.相控陣?yán)走_(dá)資源管理技術(shù)[M].北京:國(guó)防工業(yè)出版社,2016.

[3] MAILLOUX R J.Phased Array Antenna Handbook[M].Boston,America:Artech House,1993.

Multi-channelSynchronousClockTechnology

TUZheng-lin,ZHAOChen-guang

(The723InstiuteofCSIC,Yangzhou225001,China)

Withdevelopmentoftheapplicationofarrayantenna,communication,instrumentation,radar,electronicwarfareandotherindustriesarenolongersatisfiedwiththeuseofsinglechannelhigh-speedanalogtodigitalconverter(ADC),somulti-channelsynchronoussamplingtechnologyhasbeengreatlydeveloped.Thispaperconstructsaviablemulti-channelsynchronoussamplingarchitecturebasedonthemainstreamdevicesofADICo..

multi-channel;synchronousclock;arraysampling

2016-06-11

TN

A

CN32-1413(2016)05-0094-04

10.16426/j.cnki.jcdzdk.2016.05.024