面向多任務密碼處理的多核核間通信單元設計與研究

陳 帆 徐金甫 李 偉

(解放軍信息工程大學密碼工程學院 河南 鄭州 450001)

?

面向多任務密碼處理的多核核間通信單元設計與研究

陳帆徐金甫李偉

(解放軍信息工程大學密碼工程學院河南 鄭州 450001)

為了解決面向多任務密碼處理的多核核間通信機制的優(yōu)化實現問題,設計一種混合通信機制。在分析多核處理架構及核間通信特點的基礎上,融合了簇內共享存儲通信和簇間NoC通信機制,同時引入了DMA通信機制,提出構建混合通信機制,進一步提升通信效率。其次,給出核間通信同步機制的優(yōu)化實現,解決了同步和存儲一致性沖突問題。最后,基于DesignComplier對設計方案進行了實驗評估。實驗結果表明,相比其他方案,該方案具有較小的資源代價和較高的性能指標,獲得了滿意的通信吞吐率。

多核密碼處理器密碼運算核間通信同步機制

0 引 言

信息安全領域中,單核密碼處理器已無法滿足密碼算法日益增長的實現復雜性和高速性,因此多核密碼處理器應運而生[1]。隨著處理器數目的增加,如何有效地實現核與核之間的通信互聯成為了突破多核密碼處理器性能的關鍵[2]。

本文針對多核密碼處理器的密碼處理特性和核間通信需求,分析了密碼算法處理特征,提出了符合密碼算法硬件實現的混合核間通信架構,設計了核間通信同步模塊,實現了多核處理器核間高效同步通信,并對其性能進行了評估。

1 多任務密碼算法與核間通信機制分析與研究

1.1多任務密碼算法分析與研究

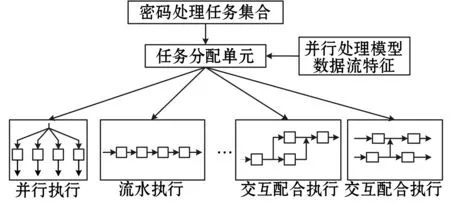

當前的密碼算法正朝著大位寬、多協(xié)議配合完成加密算法的趨勢發(fā)展[3]。多任務密碼處理結構是針對密碼算法執(zhí)行過程,按照多核并行處理模型的數據流特征將其拆分為多個處理子任務,并將子任務分別映射至各處理核單元,在時間與資源上保證密碼算法執(zhí)行的并行性。多核并行處理模型的數據流特征包括:基于任務拆分的多核并行處理模型、基于算法拆分的多核并行處理模型和安全協(xié)議多核并行處理模型[4]。

多核系統(tǒng)任務拆分工作流程如圖1所示。

圖1 多任務處理模型

任務分配單元按照密碼處理任務的需求將多核系統(tǒng)重組成最佳執(zhí)行模式,最大限度地提升密碼處理的并行性。通過對多任務密碼處理模型的分析可知,多任務密碼算法實現加密處理任務的效率直接取決于核間數據傳遞的時效性。因此,多核系統(tǒng)的設計可通過優(yōu)化核間通信單元及數據同步單元來提升多任務密碼算法的實現效率。

1.2多核系統(tǒng)核間通信單元分析

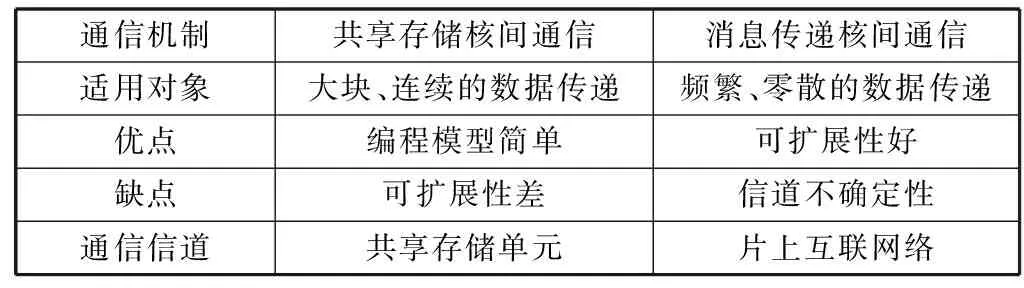

目前,在密碼多核處理器中,解決核間通信問題的方法主要有兩類。一類是共享存儲通信。如TI公司的OMAP4430[5],斯坦福大學的Hydra[6]等均采用共享存儲通信,具有編程簡單、易于利用軟件編程實現通信調度的優(yōu)點。但是由于訪存帶寬的限制,其可擴展性較差,隨著處理核數增加,核間通信延遲顯著增加,硬件開銷也會迅速增加。另一類是消息傳遞通信。如麻省理工學院的RAW處理器[7],英特爾公司的80-Tile處理器[8]等均采用消息傳遞通信,具有較高的帶寬和良好的可擴展性,適用于處理器數據較多的情況。但是隨著處理核數目的增加,片上網絡的通信延遲會明顯增加,同時局部還會出現擁塞情況。

表1 共享存儲與消息傳遞核間通信機制對比

通過分析表1總結的兩種通信方式的特點及適用情景可知,當前主流的兩種核間通信方式在針對不同通信需求的情況下各具優(yōu)勢。在實際應用中應按照實際通信情況進行合理選配不同機制。

1.3多任務密碼算法對核間通信的需求分析

通過多核系統(tǒng)實現多任務密碼算法,最大的優(yōu)勢之一就是多核系統(tǒng)相比于單核密碼處理器能夠提供更高的性能,而這種性能的提升并不是基于單核密碼處理器的簡單堆疊,而是通過充分挖掘多任務密碼算法中的并行性,通過多核系統(tǒng)中高效的核間通信機制與同步技術有效地調度各處理器核單元,以此利用多核處理器在處理器數目上的優(yōu)勢來提高系統(tǒng)吞吐率。

基于上述分析,本文需要解決兩個問題。第一,建立一種高效的核間通信機制。該機制能夠支持較大的通信量和較小的通信延遲,同時能夠便于擴展。第二,設計一種便于硬件實現且高效的數據同步方式,同時要能夠與本文設計的通信機制有機銜接。

2 混合核間通信機制設計與實現

2.1混合核間通信機制

針對多任務密碼算法對多核系統(tǒng)的通信要求,本文建立了一種混合通信機制。通過在設計中優(yōu)化各通信機制的硬件實現,將多種通信方式集成在多核系統(tǒng)中。不同通信機制對應不同通信需求、多種通信機制并行配合使用,以此高效發(fā)揮各通信機制的優(yōu)勢。

針對簇內相鄰核間通信,系統(tǒng)采用基于共享存儲的通信方式,在簇內建立雙緩沖結構的共享存儲單元,以此實現相鄰運算核心間數據的交互。雙緩沖結構設計主要解決了數據“發(fā)送者”與“接收者”速度不一致、計算不同步所造成的數據遺失問題。第一級緩沖主要解決運算核心與第二級緩沖之間速度匹配問題,用較快的存儲速度接收并暫存運算核心的計算結果,再以與第二級緩沖相匹配的速度將數據傳遞存儲至第二級緩沖。第二級緩沖主要由共享存儲單元實現,其作用是:主要依靠其較大的存儲容量將第一級緩沖中的數據保存起來,等待數據接收者讀取,完成核間數據交互。利用雙緩沖結構的共享存儲通信避免了簇內通信數據通過路由節(jié)點進行的數據包轉發(fā),以存儲器的訪問為代價有效減輕了片上網絡的通信負荷。

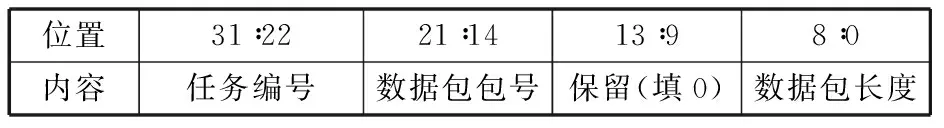

針對全局網絡中簇間運算核心間的通信,系統(tǒng)采用基于片上網絡的通信方式。通過“數據包頭+數據包”的方式進行通信。本文設計的簇間通信數據包包頭格式如表2所示。其中數據包長度代表了本次通信中數據包的個數;數據包包號代表了本次通信在本次運算任務中的執(zhí)行位置;任務編號代表了本次通信所屬的運算任務。

表2 數據包格式

通過建立簇間片上網絡數據包通信方式,實現了整個網絡上運算核心間通信數據的互聯互通,保證了系統(tǒng)中任意運算核心間通信的靈活性。同時,由于片上網絡通信方式中,數據包的傳遞在路由節(jié)點層,僅受路由節(jié)點互聯結構的影響,與路由節(jié)點的規(guī)模無關。系統(tǒng)的擴展則只增加了路由節(jié)點的數目,而不影響路由節(jié)點的互聯結構。因此片上網絡的數據包通信方式保證了系統(tǒng)較好的擴展性。

由于片上網絡的通信方式在數據交互時采用有限數據位的數據包進行交互,因此當大批量的數據在片上網絡間進行交互時,片上網絡負載較重,容易產生阻塞現象。因此針對簇間大批量數據傳輸的情況,本文引進了DMA傳輸方式也稱為“直接存儲器存取方式”[9]。該通信方式能夠將相臨共享存儲單元之間存儲的通信數據成批量進行傳輸,以減輕片上網絡通信壓力,同時減小通信時延。

通過三種通信機制的混合集成,在編寫各個處理器核單元的執(zhí)行程序時,根據通信的需求選用對應的通信機制。既保證了不同通信機制的優(yōu)勢得以發(fā)揮,又實現了多路通信的并行執(zhí)行,降低了單一通信機制的通信負載。

2.2混合核間通信機制的硬件實現

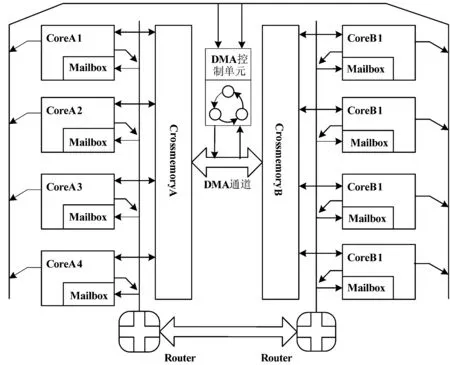

本文設計的混合通信機制硬件實現如圖2所示。

圖2 混合核間通信硬件結構圖

在該多核通信系統(tǒng)中,整個系統(tǒng)通過路由節(jié)點(Router)進行互聯與擴展,其中每個Router上連接四個密碼處理核單元(CoreX)構成一個簇。在簇中,各處理核單元能夠獨立的與Router進行數據交互,通過Router對數據中轉,以此實現數據在整個片上網絡的互聯互通。同時在每個簇內構建一個共享存儲單元(Crossmemory),各處理核單元能夠采用統(tǒng)一尋址的方式對Crossmemory進行數據讀/寫操作,以此實現簇內處理核單元的共享存儲通信。在鄰簇之間的共享存儲單元間,建立一個DMA通道,DMA通道通過一個狀態(tài)機控制通道的開關,兩個簇中不同處理器核單元能夠單獨發(fā)出控制信號,以控制狀態(tài)機狀態(tài)轉換。各處理器核單元本地設計了一個同步單元(mailbox),通過mailbox實現各通信機制的數據同步。

由文獻[10]中,對算法操作特征的統(tǒng)計可知,分組密碼的最大處理位寬一般不超過128bit、大部分序列密碼處理的數據最大位寬都超過了128bit、雜湊算法本身獨立的最大操作位寬一般不會操作128bit,但是其輸出大小一般都超過了128bit。因此在本文設計的多核系統(tǒng)中,DMA通道定為256bit位寬,確保大多數密碼算法通過DMA通道在一個周期內實現數據的傳遞。因為Router與Crossmemory因為與處理核單元要進行交互,所以數據位寬應與處理核單元保持一致,定為32bit。

2.3核間通信同步單元設計與實現

基于對多任務密碼算法的分析可知,同步單元必須支持以下兩種工作模式:①同步通信,即通信雙方工作在同一對應任務下,通信數據均為本次任務所需數據。②異步通信,即通信雙方工作在不同對應任務下,目的核未將任務1的數據讀取完畢,源核已開始同步任務2的數據。

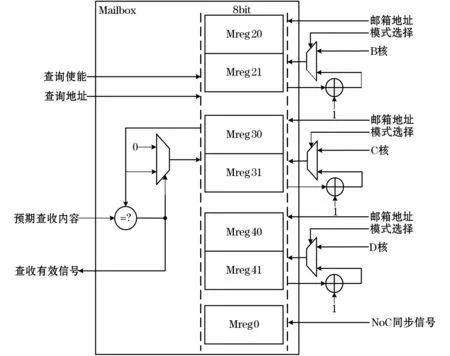

針對同步單元的要求,本文設計的郵箱同步模塊,可以在硬件開銷較小的情況下實現對共享數據一致性的保護。解決了多個處理器核訪問共享數據存儲單元時數據的讀寫先后順序的問題。同步電路硬件實現結構如圖3所示。

圖3 郵箱同步單元硬件結構圖

同步單元中針對本簇的另外三個核及簇間NoC同步,對應分別設計了一組寄存器。與處理器核對應的寄存器組由兩個8bit的寄存器(Mreg**)組成,與NoC同步對應的寄存器組只包含一個8bit寄存器(Mreg0)。同步信號的傳遞通過硬連線的方式進行傳遞。在本地處理核單元中,由本核發(fā)送查詢地址將指定寄存器中數據與預取數據對比,對比結果返回給本地處理器核。如果比對結果有效則清零相應寄存器。

同步機制設計中,針對不同的密碼運算支持任務數、乒乓等不同的同步模式。針對不同的模式,在同步單元提供了兩種同步方式——置數方式和“自加一”方式。通過模式選擇信號采用不同的工作模式。同步過程中,由置數模式可控制通信任意長度的數據,由“自加一”模式可實現不同處理核之間的乒乓操作及規(guī)整的通信數據。

3 性能評估

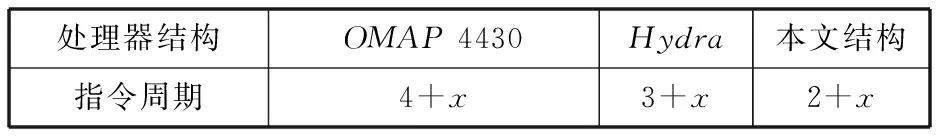

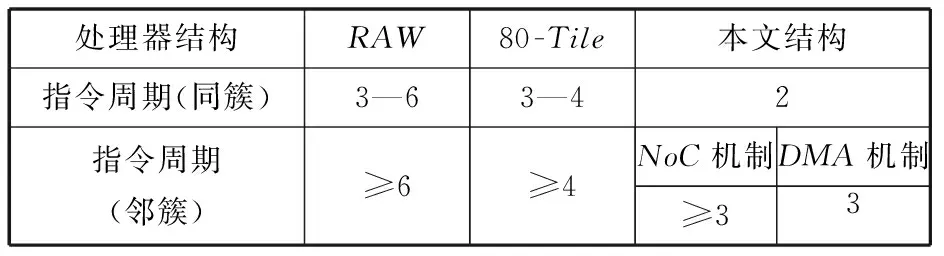

本文利用VCS仿真工具對三種通信機制進行了功能仿真,驗證了其功能的準確性及時鐘關系,驗證結果如表3、表4所示。利用DesignComplier綜合工具對本文設計的同步單元進行了綜合驗證,驗證結果如表5所示。通過仿真、驗證結果與文獻中給出的處理器進行對比可知,本文提出的通信機制具有執(zhí)行效率高、通信延遲短的優(yōu)點,同步單元具有硬件開銷小、同步效率高的特點。

表3 傳輸256 bit數據時共享存儲通信機制對比情況

(備注:對比中,不考慮同步機制帶來的影響,假設同步機制相同,且同步機制產生指令周期數為x。)

表4 傳輸一個數據包時NoC通信機制對比情況

(備注:本文結構下在鄰簇傳輸情況下,NoC通信機制利用3條指令周期傳輸一個數據包,DMA通信機制利用3條指令周期傳輸256bit數據)

由表3、表4可知,在傳輸相同數據量時,本文提出的傳輸機制能夠有效地提升數據傳輸速度,且隨著通信核之間距離的增大,速度提升越明顯。因此驗證結果表明,本文改進取得了預期結果。

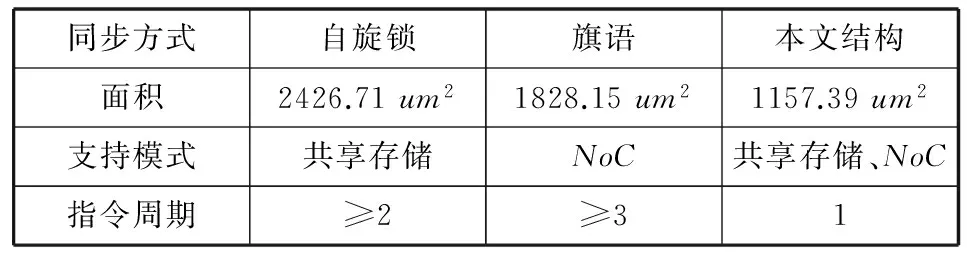

表5 同步單元性能對比

由表5可知,本文設計的同步單元硬件實現簡單,占用硬件資源少,支持模式多,同步靈活,同步延遲短,同步效率高的特點。相比文獻提出的同步單元,本設計顯著地提升同步單元的性能,達到了預期的設計目標。

4 結 語

針對密碼多核處理器中核間通信問題,本文深入研究了多核密碼處理器的核間通信問題及同步機制。針對密碼運算,本文改進了文獻[7,8]中提出的適用于通用多核處理器的共享存儲通信機制和核間信息傳遞通信機制,提出了簇間數據高速傳輸機制——DMA通信機制。和通用處理器中核間通信機制相比,在實現密碼算法過程中,本文提出的結構效率更高、支持通信方式更靈活;與通用處理器中同步單元模塊相比,本文提出的同步單元設計,硬件開銷更小、同步效率更高,與存儲結構的融合性更高。綜合結果表明,該通信機制與同步單元能夠靈活高效地實現核間通信需求,具有很好的應用前景。

[1] 謝子光.多核處理器核間通信技術研究[D].成都:電子科技大學,2009.

[2]JuX,QinY,YangL,etal.Overviewofinter-communicationmechanismonmulti-coreprocessor[C]//ComputerApplicationandSystemModeling(ICCASM),2010InternationalConferenceon.IEEE,2010,7:V7-187-V7-190.

[3]HowardJ,DigheS,HoskoteY,etal.A48-coreIA-32message-passingprocessorwithDVFSin45nmCMOS[C]//Solid-StateCircuitsConferenceDigestofTechnicalPapers(ISSCC),2010IEEEInternational.IEEE,2010:108-109.

[4]QuanH,XiaoR,YouK,etal.Asimplehigh-efficientinter-corecommunicationmechanismformulticoresystems[J].Pro.Asia-PacificSignalInf.Process.Association(APSIPA’11)ASC,2011 (338).

[5]SubramoniH,PetriniF,AgarwalV,etal.Intra-socketandinter-socketcommunicationinmulti-coresystems[J].ComputerArchitectureLetters,2010,9(1):13-16.

[6] 肖瑞瑾.多核處理器層次化存儲體系研究[D].復旦大學,2012.

[7]YuZ,YouK,XiaoR,etal.An800MHz320mW16-coreprocessorwithmessage-passingandshared-memoryinter-corecommunicationmechanisms[C]//Solid-StateCircuitsConferenceDigestofTechnicalPapers(ISSCC),2012IEEEInternational.IEEE,2012:64-66.

[8]VangalSR,HowardJ,RuhlG,etal.An80-tilesub-100-wteraflopsprocessorin65-nmcmos[J].Solid-StateCircuits,IEEEJournalof,2008,43(1):29-41.

[9]HuW,WangR,ChenY,etal.Godson-3B:A1GHz40W8-core128GFlopsprocessorin65nmCMOS[C]//Solid-StateCircuitsConferenceDigestofTechnicalPapers(ISSCC),2011IEEEInternational.IEEE,2011:76-78.

[10]MaT,BosilcaG,BouteillerA,etal.Kernelassistedcollectiveintra-nodeMPIcommunicationamongmulti-coreandmany-coreCPUs[C]//ParallelProcessing(ICPP),2011InternationalConferenceon.IEEE,2011:532-541.

[11]WangMY,SuCP,HorngCL,etal.Single-andmulti-coreconfigurableAESarchitecturesforflexiblesecurity[J].VeryLargeScaleIntegration(VLSI)Systems,IEEETransactionson,2010,18(4):541-552.

DESIGNANDRESEARCHONMCP-ORIENTEDINTER-CORECOMMUNICATIONUNITFORMULTIPLECORES

ChenFanXuJinfuLiWei

(College of Cryptography Engineering,PLA Information Engineering University,Zhengzhou 450001,Henan,China)

Inordertosolvetheproblemofoptimisingimplementationinregardtomulti-taskcipherprocessing-orientedinter-corecommunicationmechanismformultiplecores,wedesignedamixedcommunicationmechanism.Basedonanalysingthemulti-coreprocessingarchitectureandthecharacteristicofinter-corecommunication,inthispaperwefirstproposetoconstructthemixedcommunicationmechanismbyintegratingthecommunicationmechanismofshared-memorywithinclustersandthemessagepassingmechanismamongclustersmeanwhileintroducingthedirectmemoryaccess(DMA)communicationmechanism,andthisfurtherimprovesthecommunicationefficiency.Secondly,wepresenttheoptimisingimplementationofinter-corecommunicationsynchronisationmechanismandthissolvestheproblemofconsistencyconflictinsynchronisationandstorage.Finally,weevaluatethedesignschemethroughexperimentbasedonDesignComplier.Experimentalresultsshowthattheschemehaslessresourcecostandhigherperformanceindicatorscomparedwithotherschemes,andachievessatisfiedcommunicationthroughputaswell.

Multi-corecipherprocessor(MCP)CipheroperationInter-corecommunicationSynchronisationmechanism

2014-10-24。陳帆,碩士生,主研領域:大規(guī)模集成電路設計。徐金甫,副教授。李偉,講師。

TP309.7

ADOI:10.3969/j.issn.1000-386x.2016.03.076