集成電路邊界掃描測試系統中測試方式選擇模塊的電路設計

陳 翎,潘中良

(華南師范大學物理與電信工程學院,廣東 廣州510006)

集成電路邊界掃描測試系統中測試方式選擇模塊的電路設計

陳 翎,潘中良

(華南師范大學物理與電信工程學院,廣東 廣州510006)

集成電路規模的不斷增加,使測試的開銷在產品總成本中所占的比重越來越大,測試的過程更為復雜,因此對電路芯片需要采用邊界掃描測試進行可測性設計。對邊界掃描控制器中的測試方式選擇TMS模塊的功能進行了詳細說明,給出了該模塊的電路設計方法與步驟。通過與測試軟件的結合,能檢測芯片間互連線的開路故障、短路故障、固定型故障,以及芯片的內部邏輯功能是否正常。

集成電路;邊界掃描;TAP控制器;測試方式選擇

隨著集成電路(IC)的設計與制造工藝的發展,電路的集成度不斷提高,電路的規模和布線密度也迅速增大。電路芯片的內部結構日趨復雜,時鐘頻率已在向千兆赫茲及以上發展。大規模集成電路和芯片的應用領域不斷擴大,也使得與其相關的數字系統的功能與結構越來越復雜[1,2]。

在電路芯片和印制電路板的生產過程中,為保證其可靠性,測試一直是一個重要的工藝步驟。電路中常見的故障有信號線的短路、開路、固定型故障s-a-0和s-a-1,信號線和門電路的時延故障,以及信號完整性故障等[3,4]。例如,串擾就是一種典型的信號完整性故障,它是由兩條或多條信號線之間的耦合所引起的,是由一條信號線上的信號向相鄰信號線產生噪聲的現象。串擾根據其耦合源分為容性耦合和感性耦合兩種方式,當信號在通過一條信號線時會按照這兩種方式將能量耦合到相鄰的信號線上。串擾對被干擾的信號線所帶來的噪聲主要有峰值的變化和時序的變化[5,6]。在一個電路中如果存在串擾故障,將會引起電路的時序和邏輯功能發生錯誤,進而對電路的性能造成影響,并導致電路的質量和可靠性的下降。

因此,隨著集成電路規模的不斷增加,對它的測試問題也日益尖銳起來,測試的開銷在產品總成本中所占的比重越來越大,特別是對大規模數字集成電路,其測試的過程更為復雜,不能再采用傳統的物理接觸的針床和測試探針等來進行測試,必須在電路的設計時就考慮測試的問題,進行可測性設計[7,8]。邊界掃描測試就是一種可用于電路芯片與印制電路板的可測性設計技術,能夠有效地進行芯片內部的邏輯功能測試和芯片間的互連測試[9,10]。本文對邊界掃描控制器中的測試方式選擇TMS模塊的功能進行了分析,給出了該模塊的電路實現。

1 邊界掃描測試的結構

邊界掃描測試是針對電路芯片和印制電路板的一種可測試性設計技術,它能夠實現對芯片級、電路板級,乃至系統級等不同層次的測試。它是在芯片的每一個輸入/輸出管腳處添加一個邊界掃描單元,這種邊界掃描單元是由一些寄存器所組成,通過將這些寄存器連成掃描路徑,構成掃描鏈。

在進行測試期間,這些邊界掃描單元用于控制輸入管腳的狀態,并讀出輸出管腳的狀態,這樣就可以檢測出電路板中器件的好壞以及相互連接的正確性。在正常工作期間,這些邊界掃描單元是透明的,不影響芯片和電路板的正常工作。

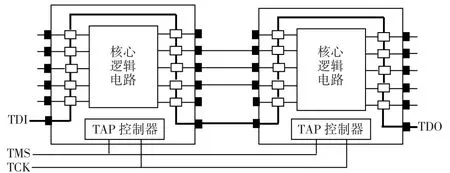

邊界掃描測試的硬件電路結構主要包括:測試存取通道(TAP)、TAP控制器、指令寄存器、旁路寄存器、測試數據寄存器等。在硬件上在電路芯片的每個I/O引腳處添加一個邊界掃描單元,以及添加一些測試控制邏輯。這些邊界掃描單元位于芯片的外部引腳和芯片的內部邏輯之間,在TAP控制器的作用下,對外部引腳和內部邏輯進行信號的采集或施加測試信號。邊界掃描測試的結構如圖1所示。

圖1 邊界掃描測試的結構

測試存取通道TAP(Test Access Port)是邊界掃描測試結構與外部電路的接口,它包括以下五種控制信號:測試時鐘、測試方式選擇、測試數據輸入、測試數據輸出、測試復位。

(1)測試時鐘TCK(Test Clock)是用于控制邊界掃描寄存器和TAP控制器的時鐘。

(2)測試方式選擇TMS(Test Mode Select)是用于確定被測電路中的TAP控制器的當前狀態,以進行測試數據的移入與移出。當該信號有效時,IC芯片處于測試模式,否則是處于正常工作模式。

(3)測試數據輸入TDI(Test Data Input)是用于邊界掃描測試數據的輸入,邊界掃描指令和測試數據均由此進行輸入。TAP控制器的狀態及指令寄存器的內容決定哪個寄存器接受TDI傳來的數據。在TCK的上升沿,TDI的數據裝入到寄存器中。

(4)測試數據輸出TDO(Test Data Output)是用于邊界掃描測試數據的輸出,由TAP控制器的狀態和指令寄存器的內容來決定哪些寄存器用于數據的輸出;TDO在TCK的下降沿改變狀態,并僅在數據輸出時有效,其余時間TDO均為高阻態。

(5)測試復位TRST(Test Reset)是用于邊界掃描測試的邏輯復位,該信號為可選信號。當為低電平時有效,即當TRST的輸入為低電平時,邊界掃描測試的控制邏輯無效,芯片進入正常工作狀態。

每個邊界掃描單元都有兩個數據通道:一個是測試數據通道,它包含測試數據輸入TDI和測試數據輸出TDO;另一個是常規數據通道,即常規數據的輸入與輸出。在常規的工作狀態時,數據的輸入和輸出可以自由地通過每個邊界掃描單元進行傳送。在測試狀態時,對于用作輸入的IC引腳,可以從TDI輸入數據;對于用作輸出的IC引腳,可以從邊界掃描單元輸出數據至TDO.

TAP控制器是邊界掃描測試的核心,它的輸入信號為TCK、TMS和TRST.TAP控制器產生測試時鐘信號,在它進入到相應的狀態時就可以進行測試數據的移位、更新、捕獲等操作。下面對TAP控制器中的測試方式選擇TMS模塊的硬件電路實現進行詳細闡述。

2 TMS模塊的電路設計

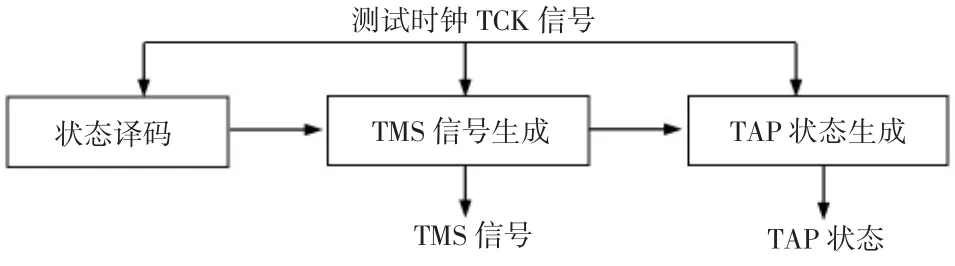

測試方式選擇TMS模塊的功能是確定并給出TAP控制器的當前狀態、產生測試方式選擇TMS信號、控制TDI模塊的數據移出和TDO模塊的數據移入。TMS模塊的結構如圖2所示。

圖2 TMS模塊的結構

在圖2中,狀態譯碼是對測試系統的指令在運行時的一些狀態例如當前狀態、工作狀態、結束狀態等的譯碼操作。測試時鐘TCK對狀態譯碼、TMS信號生成、TAP狀態生成等提供時鐘信息,使得能夠在相應的信號狀態執行特定的操作。

TMS模塊的一個主要功能是給出TAP控制器的當前狀態,這里TAP控制器是邊界掃描測試的關鍵部分,它是一個同步狀態機,把接收到的TMS信號和TCK信號進行譯碼,并產生所需要的操作控制序列,使得被測電路進入相應的測試方式。圖3是TAP控制器的狀態圖,在圖中的箭頭邊上的數字0或1是表示TMS信號在TCK上升沿的值。在圖3中右邊的分支是用于指令寄存器,左邊的分支是用于數據寄存器。

圖3 TAP控制器的狀態圖

當被測電路處于邊界掃描測試模式時,TAP控制器根據指令選擇一種寄存器,該寄存器中的每個單元在TAP控制器的作用下進行數據移位、輸出數據、鎖存數據等各種操作。

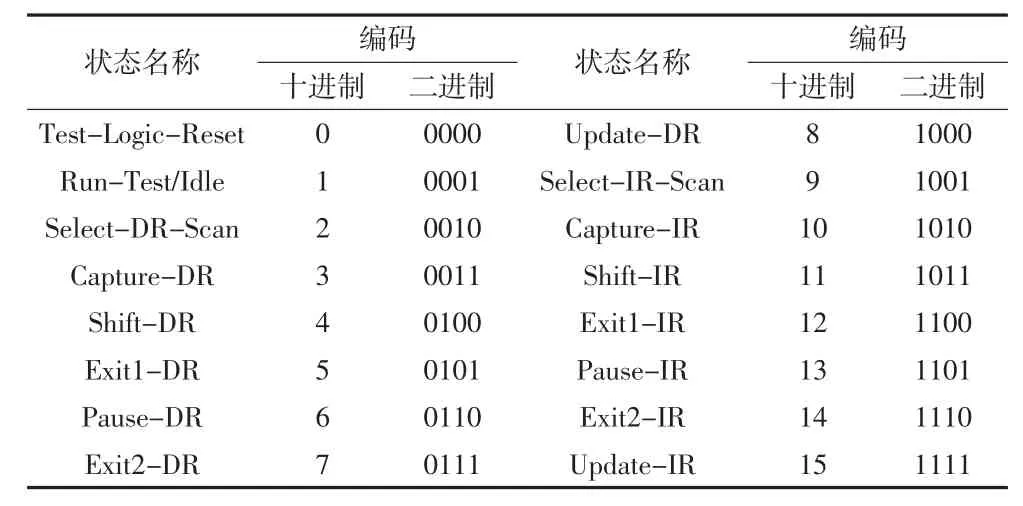

TAP控制器有如下的多個穩定狀態:測試邏輯復位(Test-Logic-Reset),運行測試/空閑(Run-Test/ Idle),數據寄存器移位(Shift-DR),數據寄存器暫停(Pause-DR),指令寄存器移位(Shift-IR),指令寄存器暫停(Pause-IR)。對TAP控制器的狀態轉換,當TMS為高電平時只有測試邏輯復位這一種穩定狀態;當TAP控制器處于其他狀態時,通過設定TMS信號為高電平,就可以在五個測試時鐘TCK的時間內返回到測試邏輯復位這種狀態。當需要對被測電路進行測試時,在TCK和TMS信號的控制下,使得TAP控制器跳出測試邏輯復位狀態,并通過選擇數據寄存器掃描(Select-DR-Scan)或選擇指令寄存器掃描(Select -IR-Scan)而進入到圖3所示的各種狀態。

對兩個分支即選擇數據寄存器掃描和選擇指令寄存器掃描中的狀態的操作過程是類似的。對選擇數據寄存器掃描,第一步是捕獲數據,是把數據并行地加載到相應的串行數據通道中,然后TAP控制器從捕獲狀態(Capture-DR)進入到移位狀態(Shift -DR)或退出1狀態(Exit1-DR)。隨后,TAP控制器可以通過退出1狀態而進入到更新狀態(Update-DR)或暫停(Pause-DR)狀態。當在更新狀態時,移入掃描通道的數據被輸出;當在暫停狀態時,對數據的移位被暫時停止,這時可以對數據寄存器重新加載測試矢量。當跳出Pause-DR狀態之后,就進入到退出2狀態(Exit2-DR),然后通過該狀態可以再次進入移位狀態或更新狀態,或回到運行測試/空閑(Run -Test/Idle)狀態。只要TMS信號保持為邏輯0,則TAP控制器就處于運行測試/空閑狀態。

對被測電路進行測試的第一步是裝入一條指令,此時必須進入到選擇指令寄存器掃描這一分支,為了從運行測試/空閑狀態進入到該分支,需要兩個TCK時鐘脈沖,同時TMS必須保持在邏輯1.當TAP控制器處于該分支時,被測電路中的指令寄存器被串行連接起來,并被連接在TDI與TDO管腳之間;對緊接著的兩個TCK時鐘脈沖,并使TMS為邏輯0,就能進入到捕獲指令寄存(Capture-IR)狀態,隨后可進入到移位指令寄存(Shift-IR)狀態。這里,只要TAP控制器處于移位指令寄存狀態且TMS保持為邏輯0時,在多個TCK時鐘脈沖的時間內,移位操作可以連續進行。若把TMS再次設置為邏輯1,則移位過程結束,進入到退出1狀態(Exit1-IR),然后可進入更新指令寄存(Update-IR)狀態。在更新指令寄存狀態,將TMS設置為邏輯0時,就回到運行測試/空閑狀態;將TMS設置為邏輯1時,就進入到選擇數據寄存器掃描這個狀態。

在對TMS模塊進行硬件電路設計時,首先需要對TAP控制器的狀態進行編碼,以把當前的狀態值鎖存到寄存器中。表1是TAP控制器的狀態的一種編碼方式。

表1 TAP控制器的狀態編碼

其次,TMS模塊的電路結構主要是由一個FIFO緩存、TAP狀態機和TAP狀態寄存器三部分組成。這里的FIFO緩存用于存儲多條測試命令,例如,對整個邊界掃描進行復位操作的命令,進行數據移位的命令,進行指令移位的命令等。這些命令是通過電路的JTAG接口進行測試時使用的測試命令,是由被測電路的生產商在出廠時就已經定義好的,因此可直接使用。通過不斷地對FIFO緩存中的命令進行讀取并執行,每執行完一條命令后,再從FIFO中取出下一條命令,直到FIFO為空。

TMS模塊中的TAP狀態機依據當前所輸入和執行的這條命令,來進行狀態轉移,并根據對應的狀態來產生并輸出相應的TMS信號。例如,當執行的命令是復位命令Reset時,則TMS信號是連續輸出5個TCK周期長度的高電平,使被測電路進入TAP的測試邏輯復位狀態;當執行的命令是數據移位命令時,則TMS信號是TDO使能信號,使TDO模塊進行移位操作。TMS模塊中的TAP狀態寄存器的作用是將當前的狀態值鎖存到寄存器中,以供其它的電路模塊查詢當前的TAP狀態并在此基礎上通過一定的途徑來改變TAP的后續狀態。

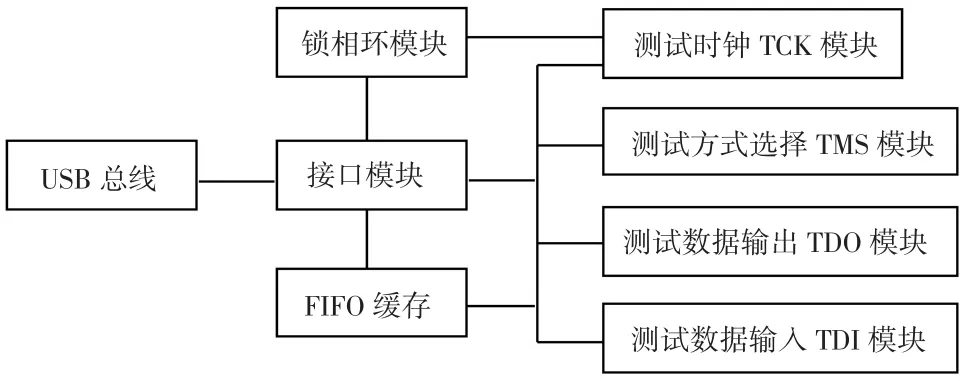

使用如上的TMS模塊的電路結構,采用FPGA設計了一個邊界掃描控制器,如圖4所示。對邊界掃描控制器的USB總線,采用USB芯片CY7C68013A來實現,以完成邊界掃描控制器與微型計算機之間的通信。對邊界掃描控制器的其它部分,采用FPGA芯片EP2C8Q208C8N來實現,通過該控制器對微型計算機傳來的測試命令與測試數據進行相應的時序轉換,實現對被測電路的邊界掃描測試,即完成操作指令與測試矢量的施加,對測試響應的捕獲,對故障與測試結果的分析等。

圖4 邊界掃描控制器的結構

在圖4中,鎖相環模塊是對輸入時鐘信號進行倍頻,供FPGA芯片內的各個模塊使用。接口模塊是完成與USB芯片的通信,通過使用上位機(微型計算機)上的測試程序來實現對邊界掃描控制器的測試過程的控制與測試結果的傳送。測試時鐘TCK模塊是實現可變頻率的測試時鐘信號,測試方式選擇TMS模塊是根據所輸入的命令和TAP狀態,來產生TMS信號以及產生對TDO和TDI模塊的控制信號。測試數據輸出TDO模塊實現對FIFO緩存中數據的并串轉換,并按照TMS的指示來完成數據的輸出。測試數據輸入TDI模塊實現對TDI輸入信號的采樣,并在TMS模塊的控制下完成串并轉換,并進行保存。

3 實驗結果

用C++語言編制了邊界掃描的測試軟件,該軟件由如下模塊組成:電路結構處理、電路網表結構分析、完備性測試、互連測試、芯片內部功能的測試、測試結果輸出等。該軟件在微型計算機上運行,通過與邊界掃描控制器的結合,實現了對被測電路的整個測試過程。

為驗證邊界掃描測試系統的性能,設計了一個被測電路板,在該板上主要有如下六個芯片:EP1C3T144、EPM7064AET44、四個SN74LVTH182512.把這六個芯片通過邊界掃描測試總線中的TCK、TMS、TDI和TDO等進行連接。同時,在它們的互連線上設置了開路、短路、固定型s-a-0和s-a-1等多種類型的故障。

實驗結果說明,所設計的邊界掃描測試系統,能檢測芯片的內部邏輯功能是否正常,能夠檢測芯片間互連線的開路故障、短路故障、固定型故障s-a-0 和s-a-1等多種類型的故障。

4 結束語

邊界掃描測試能夠對電路芯片的內部邏輯功能以及芯片間互連線的故障進行檢測,可以有效地提高電路芯片和印制電路板的可靠性。在進行邊界掃描控制器的設計時,測試方式選擇TMS模塊對整個測試過程起主要作用。本文對TMS模塊的功能進行了詳細闡述,給出了對它的電路實現方法。

[1]潘中良.系統芯片SoC的設計與測試[M].北京:科學出版社,2009.

[2]陳光禹,潘中良.可測性設計與技術[M].北京:電子工業出版社,1997.

[3]W.Dghais,J.Rodriguez.New multiport I/O model for poweraware signal integrity analysis[J].IEEE Trans.on Components Packaging&Manufacturing Technology,2016,6(3):447-454.

[4]B.A.Khaled,N.C.Roda,G.Ali.RF performance of SOI CMOS technology on commercial 200-mm enhanced signal integrity high resistivity SOI substrate[J].IEEE Trans.on Electron Devices,2014,61(3):722-728.

[5]V.R.Kumar,A.Alam,B.Kaushik.An unconditionally stable FDTD model for crosstalk analysis of VLSI interconnects[J]. IEEE Trans.on Components,Packaging&Manufacturing Technology,2015,5(12):1810-1817.

[6]K.Karmarkar,S.Tragoudas.On-chip codeword generation to cope with crosstalk[J].IEEE Trans.on CAD,2014,33(2): 237-250.

[7]IEEE Std1149.1-2001,IEEE standard test access port and boundary-scan architecture[S].2001.

[8]F.Farnaz,N.Bahareh,T.Fatemeh.A new approach to model the effect of topology on testing using boundary scan[J].Journal of Electronic Testing,2015,31(3):301-310.

[9]L.Y.Ungar.Boundary scan as a system-level diagnostic tool [J].IEEE Instrumentation&Measurement Magazine,2013,16 (4):8-15.

[10]B.Terry.Considerations in the design of a boundary scan runtime library[J].IEEE Instrumentation&Measurement Magazine,2014,17(4):27-30.

Circuit Design of Test Mode Selection Module for Integrated Circuits Boundary Scan Testing System

CHEN Ling,PAN Zhong-liang

(School of Physics and Telecommunication Engineering,South China Normal University,Guangzhou Guangdong 510006,China)

The increasing scale of integrated circuits makes that the cost of the testing process is increasing in the proportion of the total cost of the product.The testing process of chip is more complex,therefore it is needed to adopt the boundary scan testing which is one of design for testability.The function of test mode selection module in boundary scan controller is demonstrated in this paper,the circuit design method and procedure are given.The combination of boundary scan controller and testing software can detect the open faults,bridge faults,stuck-at faults,and can detect the internal logic function of the chips.

integrated circuits;boundary scan;TAP controller;test mode selection

TN407

A

1672-545X(2016)07-0023-05

2016-04-02

廣東省自然科學基金(編號:2014A030313441);廣東省科技計劃項目(編號:2013B090600063,2014B090901005),廣州市科技計劃項目(編號:201510010169)資助。

陳翎(1968-),女,四川成都人,本科,工程師,研究方向:電路與系統。