基于有限狀態(tài)機(jī)的二進(jìn)制序列信號檢測器的設(shè)計

李建偉(長治學(xué)院電子信息與物理系,山西長治,046011)

基于有限狀態(tài)機(jī)的二進(jìn)制序列信號檢測器的設(shè)計

李建偉

(長治學(xué)院電子信息與物理系,山西長治,046011)

本文用Verilog HDL語言在Altera公司的現(xiàn)場可編程邏輯器件EP1C6Q240C8上設(shè)計了一個8位序列信號檢測電路。文中介紹了Verilog HDL狀態(tài)機(jī)設(shè)計電路的方法,給出了所設(shè)計電路的仿真波形,并最終在可編程邏輯器件EP1C6Q240C8上實現(xiàn)了該電路。

有限狀態(tài)機(jī)(FSM);序列信號檢測器;Verilog HDL;EP1C6Q240C8

0 引言

序列信號檢測器是將一個指定序列從數(shù)字碼流中識別出來,它在雷達(dá)、遙測、數(shù)據(jù)通信、密碼認(rèn)證等領(lǐng)域中用有著廣泛的應(yīng)用。

在設(shè)計序列信號檢測器時可以采用可編程邏輯芯片和硬件描述語言相結(jié)合的方式進(jìn)行,與常規(guī)的設(shè)計方法對比,該設(shè)計方法簡化了電路硬件的設(shè)計過程,使設(shè)計者將更多的精力用于軟件設(shè)計,而且電路設(shè)計的穩(wěn)定性也有顯著提高。

1 有限狀態(tài)機(jī)(FSM)及其設(shè)計電路步驟

1.1有限狀態(tài)機(jī)硬件優(yōu)勢

當(dāng)前以硬件描述語言為工具,邏輯器件為載體的系統(tǒng)設(shè)計越來越廣泛。在設(shè)計中,狀態(tài)機(jī)是最典型,應(yīng)用最廣泛的電路模塊,其結(jié)構(gòu)模式相對簡單、層次分明、運行速度高效、執(zhí)行時間確定。

有限狀態(tài)機(jī)可應(yīng)用于各種系統(tǒng)控制,如:微處理機(jī)與外設(shè)之間的控制、工業(yè)控制數(shù)據(jù)的加密與解密,數(shù)字信號與處理中的時序控制等。

1.2有限狀態(tài)機(jī)的結(jié)構(gòu)示意圖

常用狀態(tài)機(jī)的一般結(jié)構(gòu)示意圖如圖1所示。

1.3有限狀態(tài)機(jī)設(shè)計的一般步驟

利用狀態(tài)機(jī)進(jìn)行設(shè)計有如下幾個步驟:

圖1 狀態(tài)機(jī)的一般結(jié)構(gòu)示意圖

(1) 定義輸入變量和輸出變量。

(2) 根據(jù)具體問題,定義狀態(tài)機(jī)可能出現(xiàn)的狀態(tài)。

(3) 用二進(jìn)制碼對出現(xiàn)的狀態(tài)進(jìn)行合理編碼。

(4) 用Verilog HDL語言對狀態(tài)機(jī)進(jìn)行描述。

1.4設(shè)計電路說明

設(shè)計一個二進(jìn)制串行輸入信號為“10101110”的序列信號檢測電路,并通過一個7段數(shù)碼顯示譯碼器作為檢測結(jié)果的輸出顯示,如果串行序列為“10101110”,譯碼器顯示“C”,否則顯示“F”。

2 序列信號檢測器的設(shè)計

2.1設(shè)計思路

設(shè)計時假設(shè)電路的初始狀態(tài)為s0,如果輸入信號按照“10101110”的次序依次輸入,則電路的狀態(tài)依次出現(xiàn)s0→s1→s2→s3→s4→s5→s6→s7→s8,當(dāng)出現(xiàn)s8時,輸出狀態(tài)顯示為“C”。

2.2Verilog HDL源程序

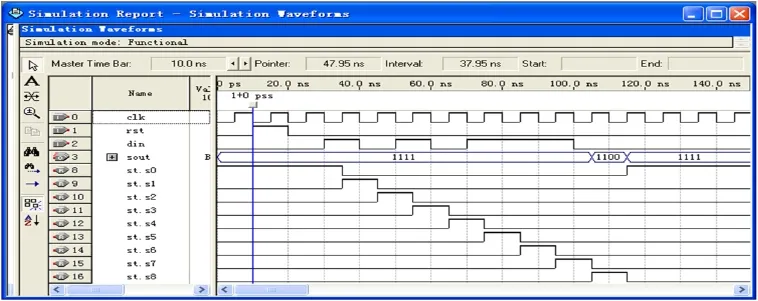

圖2 序列信號發(fā)生器的仿真結(jié)果

圖3 GW48實驗系統(tǒng)電路結(jié)構(gòu)圖

2.3程序說明

程序中clk是時鐘信號,上升沿有效;rst是異步清零信號,高電平有效。如果rst產(chǎn)生一個有效信號,當(dāng)前狀態(tài)進(jìn)入s0,同時程序啟動組合進(jìn)程,開始執(zhí)行條件分支語句。為和實驗系統(tǒng)有機(jī)結(jié)合,程序的輸出sout定義為一個4位位寬的矢量。

2.4功能仿真

在對源程序編譯后,進(jìn)行仿真時,選擇Assignments-Settings-Simulator Settings-Simution -mode-functional仿真,仿真結(jié)果如圖2所示。

仿真波形顯示,當(dāng)有正確序列“10101110”進(jìn)入時,時序進(jìn)程在時鐘脈沖的上升沿會完成狀態(tài)s0~s8的變化。當(dāng)?shù)搅藸顟B(tài)s8時,輸出序列標(biāo)志sout=1100(譯碼后顯示為“C”),否則輸出序列標(biāo)志sout=1111(譯碼后顯示為“F”)。

2.5引腳鎖定

該電路的硬件測試是在GW48實驗系統(tǒng)上完成的。GW48實驗系統(tǒng)的核心器件是采用Alter公司的EP1C6Q240C8芯片。EP1C6Q240C8芯片是Altera公司推出的新一代低成本、中等規(guī)模的FPGAGW48實驗系統(tǒng)的電路圖如圖3所示。

結(jié)合實驗系統(tǒng),在進(jìn)行引腳鎖定時,按鍵7用來控制復(fù)位信號CLR;按鍵6來控制時序脈沖CLK;需要檢測串行序列數(shù)輸入信號DIN與PIN_3連接;輸出端AF接PIN_168~ PIN_165。引腳鎖定如圖4所示。

2.6硬件測試

編程下載后,用按鍵2和按鍵1輸入兩個十六進(jìn)制待測序列數(shù)“10101110”(密碼),按鍵6(CLK)8次后,串行輸入的8位二進(jìn)制序列碼與預(yù)置碼“10101110”相同,數(shù)碼8的顯示就從字符“F”變成字符“C”。

3 結(jié)論

用有限狀態(tài)機(jī)編寫的該序列檢測器成功的通過了綜合和布局布線,從仿真波形和硬件測試結(jié)果發(fā)現(xiàn),該電路功能完全正確,實現(xiàn)了預(yù)定任務(wù)。通過該電路的設(shè)計可以看出,與傳統(tǒng)的電路設(shè)計方法比較,EDA技術(shù)可以用HDL語言對數(shù)字系統(tǒng)進(jìn)行抽象的行為與功能描述,可利用計算機(jī)在電子設(shè)計的每一個階段來模擬驗證,確保了設(shè)計過程的正確性,從而降低了設(shè)計成本,縮短了設(shè)計周期。

[1] 潘松,黃繼業(yè).EDA技術(shù)實用教程(第四版)[M].北京:科學(xué)出版社,2012.

[2] 周小仨.基于verilog的序列檢測器設(shè)計[J].軟件工程師,2015,(3):7-8.

[3] 張武.基于VHDL的有限狀態(tài)機(jī)設(shè)計[J].華東理工學(xué)院學(xué)報,2007,30(4):366-369.

[4] 李瑞,孫顯龍等.基于FPGA和VHDL的序列檢測器設(shè)計[J].微處理機(jī),2012,33(5):4-6.

[5] 劉斌,孫志雄.基于FP G A 的序列檢測器設(shè)計[J].科技信息,2013, 30(6):306.

[6] 李蕓,黃繼業(yè)等.EDA技術(shù)實踐教程 [M].北京電子工業(yè)出版社,2014.

Detecting Device Design for Binary Sequence Signal Based on the Finite State Machine

Li Jianwei

(Department of Electronic Information and Physics,Changzhi University,Changzhi Shanxi,046011,china)

In this paper,a detecting electric circuit for 8 binary digits sequence signal is designed by employing the language of Verilog HDL,based on Field Complicated Programmable Logic Device EP1C6Q240C8 from Altera Company.This paper first introduce the design method for the detecting electric circuit device by use of Verilog HDL finite state machine,subsequently show the simulation waveforms for the designed electric circuit device,and finally implement the detecting functionality of the electric circuit device at the Field-Programmable Gate Array EP1C6Q240C8.

Finite State Machine(FSM);Sequence Detector;Verilog HDL;EP1C6Q240C8

圖4 EP1C6Q240C8引腳鎖定

TP302

A