DRAM中一種延遲時間穩定的時鐘樹驅動電路

【摘要】 本文介紹了一個應用于DRAM芯片的延遲時間穩定的時鐘樹驅動電路。所述的時鐘樹驅動電路采用一種隨電壓變化不敏感的驅動電路設計,以保證在驅動電路的供電電壓發生過沖或者是有壓降時,時鐘樹驅動電路的延遲時間能夠保持相對穩定,從而保證輸出數據時序穩定,實現較好的數據輸出眼圖。

【關鍵詞】 時鐘樹 延遲時間 模擬集成電路

一、引言

隨著JEDEC接口標準的不斷升級,從最初的SDR到DDR,DDR2/DDR3,到目前最新的DDR4 接口協議, 動態內存芯片(DRAM)支持的時鐘頻率不斷升高,DDR4 最高支持3200的數據傳輸速率。為了保證良好的數據輸出眼圖性能,DRAM中的時鐘樹電路設計變得非常關鍵。時鐘樹電路的時序穩定直接關系到DRAM輸出數據眼圖的大小。

二、DRAM中傳統的時鐘驅動樹電路設計

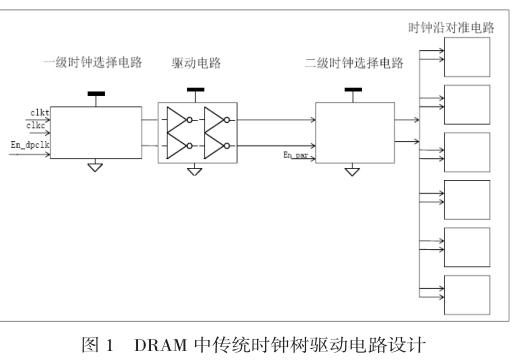

DRAM中的數字時鐘鎖相環輸出的時鐘信號需要經過時鐘樹驅動電路和片上輸出驅動最終輸出數據。而時鐘樹驅動電路部分的設計尤其關鍵。圖1為一個目前DRAM中傳統的時鐘樹驅動電路。Clkt,clkc為鎖相環輸出的互補時鐘信號,en_dplck為一級時鐘選通信號,en_par為二級時鐘選通信號。由于時鐘樹驅動電路耗電較大,加上其一級時鐘選擇電路和二級時鐘選擇電路的使能信號隨不同的操作模式進行開關切換,由此導致時鐘樹電路的耗電也會有動態的切換。

在DRAM芯片中,時鐘樹的供電電壓由內部的LDO電壓供電模塊提供。一級時鐘選擇信號由與省電模式相關的信號生成,當芯片進入省電模式時,時鐘樹的時鐘信號被關掉,耗電減少,電壓會有瞬態的上沖;當退出省電模式時,時鐘開啟,耗電增大,內部供電電壓有下降,由此會導致整個時鐘樹電路的傳遞延遲變慢,而且由于電壓抖動對時鐘信號的上升沿和下降沿部分的影響不同,也會導致時鐘樹電路的輸出信號的占空比變差。而在目前的DRAM設計中,大多是通過增加供電電壓網絡上的電容或者改善供電電壓生成器的性能來減少電壓抖動,以期望改善時鐘樹輸出信號的性能。但是這些方法占用了很大的芯片面積而且效果不是很理想。

三、DRAM中一種延遲時間穩定的時鐘樹驅動電路

為了解決現有的時鐘樹驅動電路在供電電壓抖動時會產生延遲,造成輸出數據眼圖變窄的技術問題,本文所述時鐘樹驅動電路采用一種隨電壓變化不敏感的驅動電路設計,以保證在驅動電路的供電電壓發生過沖或者是有壓降時,時鐘樹驅動電路的延遲時間能夠保持相對穩定,從而保證輸出數據時序穩定,實現較好的數據輸出眼圖。

如圖2所示,本時鐘樹驅動電路主要包括四部分電路:一級時鐘選擇電路,驅動電路,二級時鐘選擇電路,時鐘沿對準電路,以及電流鏡像電路。一級時鐘選擇電路上還連接有NMOS管和PMOS管,NMOS管和PMOS管的漏端均與一級時鐘選擇電路連接;驅動電路上連接有NMOS管和PMOS管,NMOS管和PMOS管的漏端均與驅動電連接;二級時鐘選擇電路上連接NMOS管和PMOS管,NMOS管和PMOS管的漏端均與二級時鐘選擇電路連接;

其中clkt,clkc為從數字時鐘鎖相環輸出的一組互補時鐘信號。En_dpclk為一級時鐘使能信號,主要與省電模式操作相關。En_par為二級時鐘使能信號,主要與讀操作命令有關。Iref為DRAM芯片中與溫度電壓基本無關的參考電流。經過電流鏡像電路生成vbiasn和vbiasp兩個電壓,分別連接到NMOS和PMOS的柵端鏡像一個固定的電流到時鐘樹電路中。圖3所示電流鏡像電路的結構圖。當然除了電流鏡像電路,還可以是其他現有技術中一些能夠產生電壓的電路。

對于輸入時鐘信號clkt,clkc,當信號從低變高時,經過PMOS管精確鏡像過來的電流Iref對內部節點進行充電,其充電時間固定,無論供電電壓抖動大小,此時鐘信號的上升沿和延遲時間都僅有Iref決定,同理,當信號由高變低時,經過NMOS管鏡像過來的電流Iref對內部電壓節點進行放電,其放電時間也不隨供電電壓變化,所以時鐘信號的下降沿和延遲時間也都相對穩定。時鐘樹電路的每一級均經過上述處理后,那么整個時鐘樹電路的延遲時間和輸出時鐘的占空比都會對供電電壓不敏感,從而保證了較好的輸出數據眼圖。此固定電流通過PMOS管和NMOS管對中間節點進行充電/放電,其充電/放電時間基本保持恒定。所以每一級電路的傳遞延遲僅與iref有關,與內部供電電壓的抖動基本無關。

本文所述的延遲時間穩定的時鐘樹驅動電路,具有以下優點:

1、在時鐘樹驅動電路的設計中,采用一種隨電壓變化不敏感的驅動電路設計,以保證在驅動電路的供電電壓發生過沖或者是有壓降時,時鐘樹驅動電路的延遲時間能夠保持相對穩定,從而保證輸出時鐘信號穩定,實現較好的數據輸出眼圖。2、本文所述電路結構設計簡單,但卻大大改善了電路的性能。

四、結論

通過采用一種隨電壓變化不敏感的時鐘樹驅動電路設計,以保證在驅動電路的供電電壓發生過沖或者是有壓降時,時鐘樹驅動電路的延遲時間和時鐘的占空比能夠保持相對穩定,從而保證輸出數據時序穩定,實現較好的數據輸出眼圖。

參 考 文 獻

[1]賈雪絨,“一種延遲時間穩定的時鐘樹驅動電路”專利號201420575679.2,證書號4086328;授權日期 2015/01/21