基于CUDA的數字調相信號并行解調程序設計*

劉燕都,鄭海昕,王小平

(1.裝備學院,北京 101416;2.76160部隊,廣東 廣州 510000)

?

基于CUDA的數字調相信號并行解調程序設計*

劉燕都1,鄭海昕1,王小平2

(1.裝備學院,北京 101416;2.76160部隊,廣東 廣州 510000)

摘要:在通用計算機上實現數字通信的接收解調是近年來信號處理領域的重要研究方向。就實時性要求較高的數字調相信號解調問題,分析了算法的可并行性,研究了在通用計算機上實現的算法。針對“CPU+GPU”異構計算平臺特點,提出了數字調相信號并行計算模型,基于CUDA平臺設計了混頻器、鑒相器、濾波器等模塊的并行程序,實現了BPSK信號解調。測試結果表明,計算時間比為1:1.7,在SNR=9.6 dB時誤碼率可以達到10-5,與專有硬件解調數字調相信號的指標相當,但通用計算機平臺實現方法更為靈活、易于功能擴展。

關鍵詞:數字調相信號;解調;CUDA;并行

0引言

近年來,隨著通用計算機性能的不斷提高,數字通信系統中信號處理平臺在經歷了由模擬器件構建的硬件平臺向軟件無線電技術的數字化平臺的轉變后,正在開始向純軟件化的方向發展,將采樣后的信號直接送入通用計算機,以軟件處理的方式完成信號的解調、解碼等。

數字相位調制,也就是相移鍵控(Phase Shift Keying,PSK),是一種十分重要的基本數字調制技術,也是一種用載波相位表示輸入信號信息的調制技術。在時不變信道中,調相信號比調幅和調頻信號具有更高的抗噪聲性能和頻帶利用率,即使在有衰落信道、多徑和強干擾的情況下也有較好的效果。因此,數字相位調制是一種性能優良的調制方式,在衛星通信、高速數據傳輸中得到了廣泛應用。根據理想軟件無線電的發展趨勢[1],通信過程中,各項功能都應由軟件來實現。本文基于高性能計算平臺,研究了調相信號的軟件化并行解調算法,以及基于CUDA的并行程序設計方法,并對調相信號并行解調程序進行測試,驗證了調相信號并行解調的可行性。此處填入前言內容 。

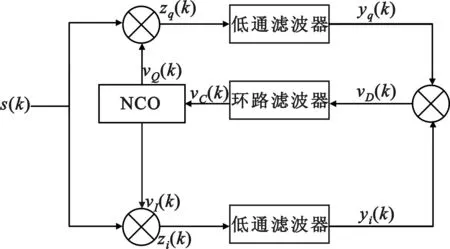

1調相信號解調

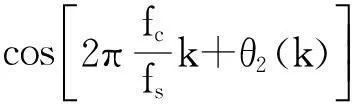

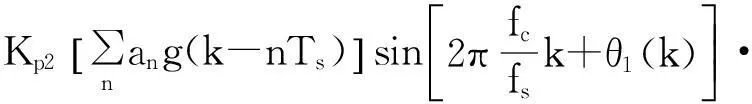

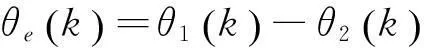

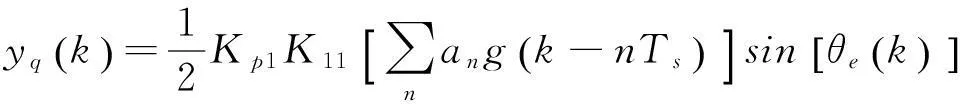

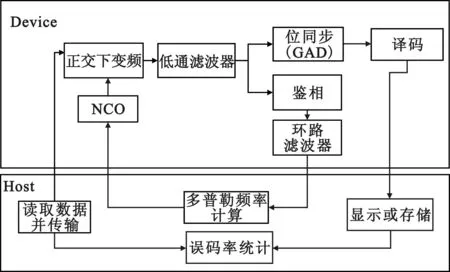

調相信號解調方法一般可分為相干解調和非相干解調[2]。相干解調需要恢復與輸入信號同頻同相的信號,而非相干解調只需提取同頻信號,雖然非相干解調實現方式簡單,但相干解調因其恢復的信號與輸入信號相位嚴格對齊,因此解調效果更好,應用更為廣泛。但調相信號在調制過程中抑制了載波分量,若要提取同頻同相的載波進行解調一般采用特殊設計的鎖相環[3]。如平方環法、Costas環[4]等。還可以根據相鄰碼元之間相位跳變情況采用差分解調方法[5],算法相對簡單,但其抗噪聲性能要明顯劣于相干解調。數字Costas環結構見圖1。

圖1 數字Costas環結構

以二進制數字調相信號為例,其信號經采樣后[6]:

(1)

(2)

(3)

(4)

式中,K11,K12為低通濾波器系數,經濾波后的I、Q兩路信號經相乘鑒相后,由環路濾波,可得:

(5)

式中,Kp為鑒相增益,Kd為環路增益,環路濾波器輸出為NCO的頻率控制字。

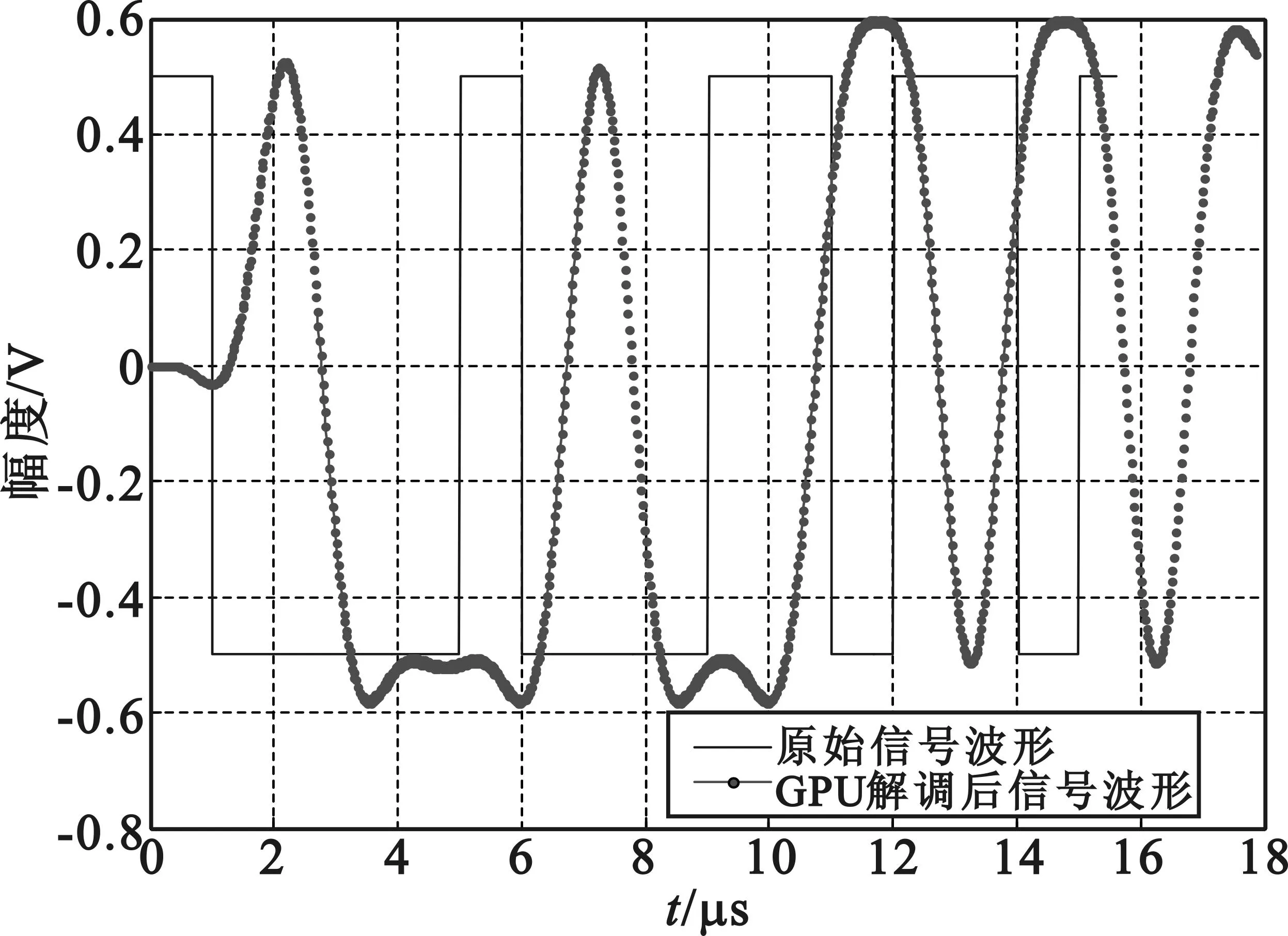

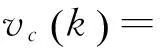

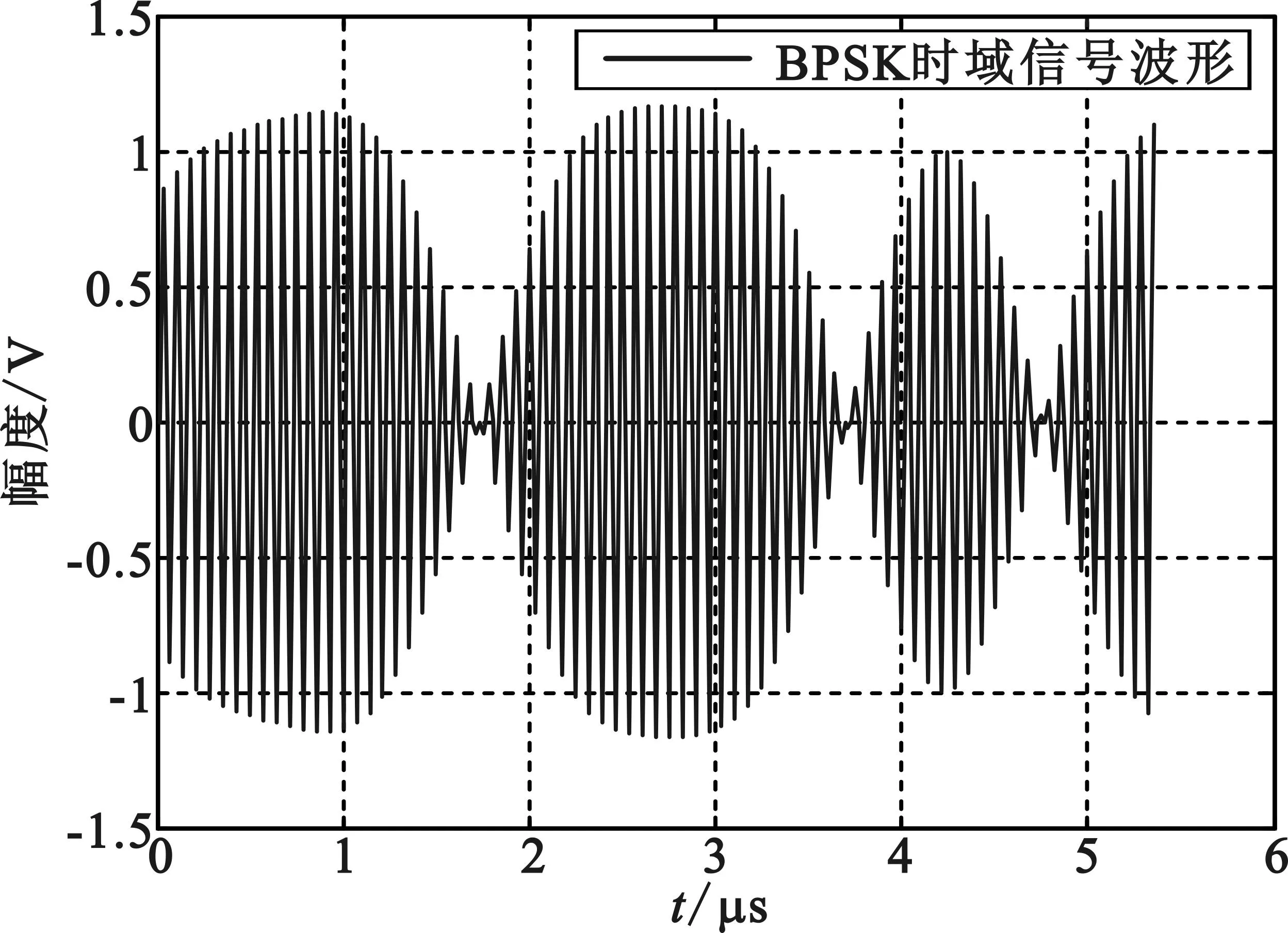

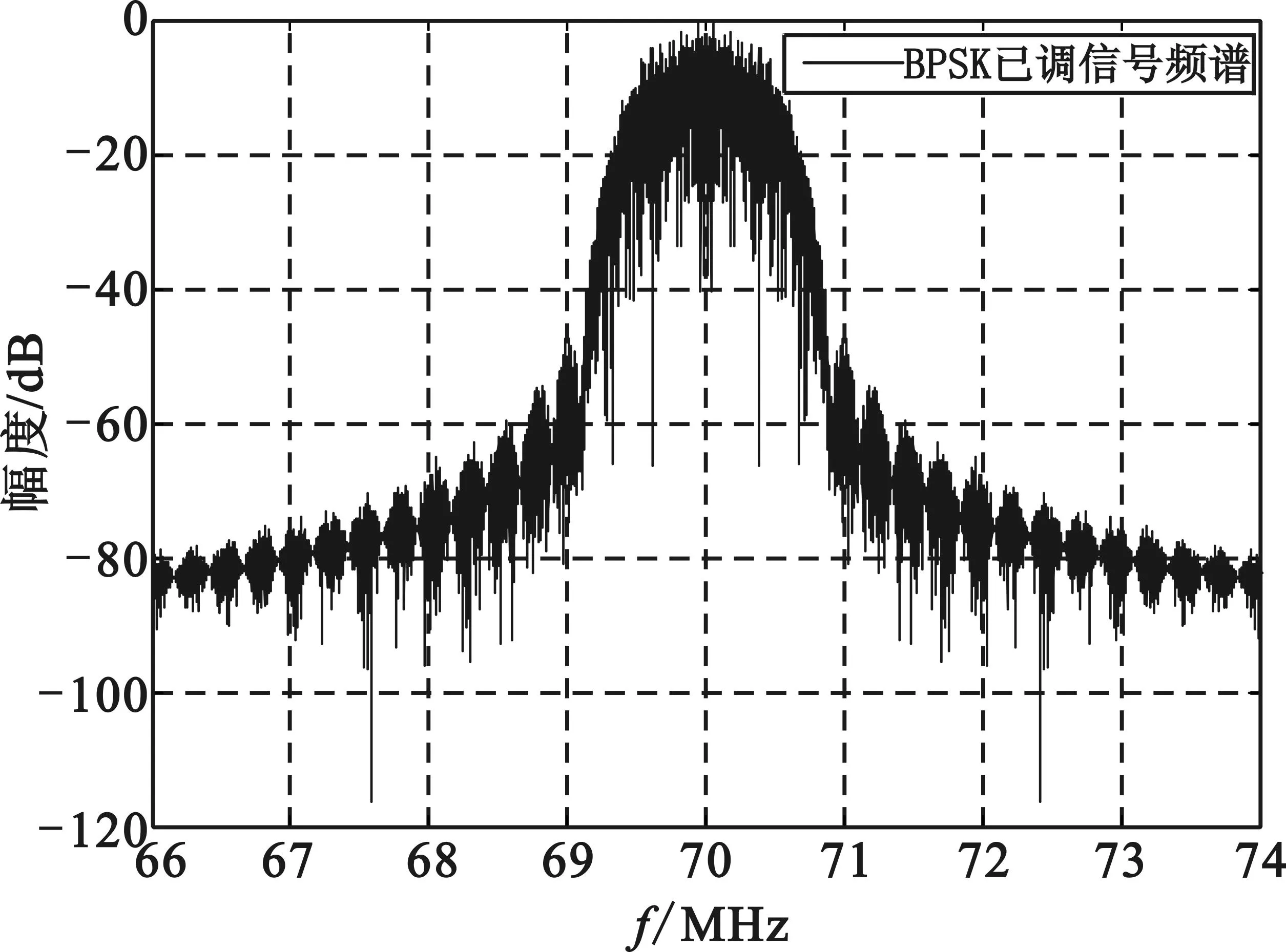

當環路鎖定后,提取出同頻同相的相干載波后,將其與輸入的已調信號直接相乘,并濾波輸出,即可得到基帶信號波形,如圖2所示,解調和鎖相環跟蹤如圖3所示。

圖2 數字調相信號時域波形及頻譜

圖3 解調結果及鎖相環路頻率跟蹤曲線

2基于CUDA的并行計算模型

分析Costas環結構,可知不僅I、Q兩路可以實現任務級的并行計算,其中的鑒相器、混頻器和濾波器還可以實現數據級的并行計算,因此,研究在特定并行計算平臺上的計算方法。

2.1CUDA

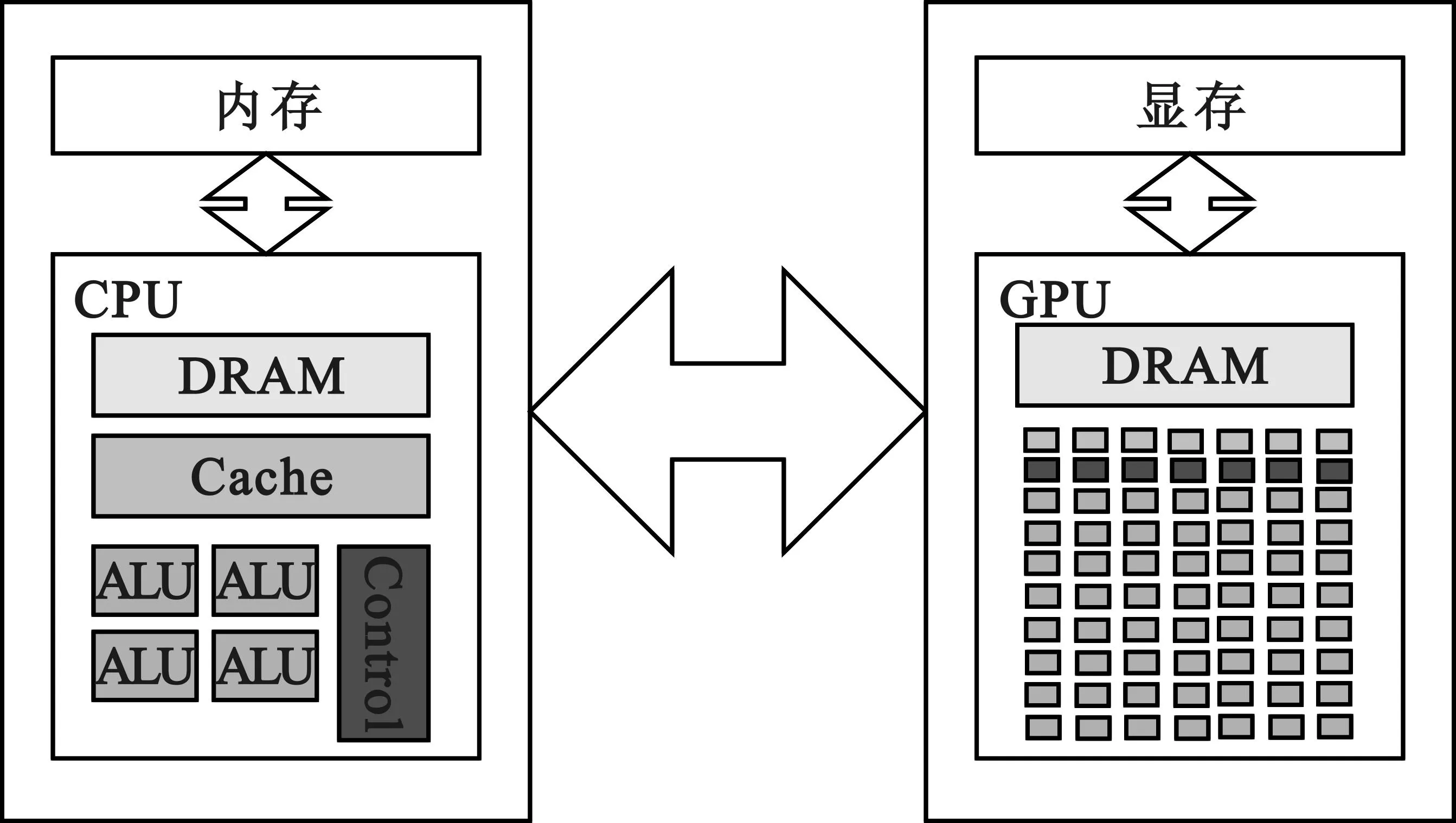

CUDA[7]是由NVIDIA公司推出的一種通用并行計算架構。起初是為加速圖像實時處理而設計的一種運行在GPU上的開發平臺,其充分運用了GPU的高存儲帶寬和超大規模的浮點計算單元,現在被廣泛應用于大型并行化問題,如氣象模擬、地震預報、分子計算等。CUDA硬件架構如圖4所示。

圖4 CPU和GPU結構對比

從圖4不難看出,GPU是特別為計算密集,高并行度計算設計的,因此將更多的片上資源用于計算而不是數據緩存和邏輯。特別地,從GPU結構分析,其非常適合處理SIMD(單指令多處理)并行問題,即同一程序在多個數據上并行執行的問題,而數字信號處理具備這種特征,所以在CUDA平臺非常適合進行數字信號處理。

2.2并行計算模型

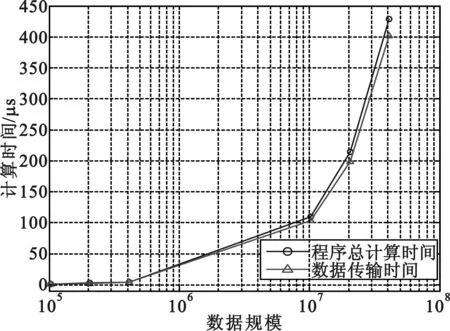

根據GPU的硬件設計特點,CUDA在并行算法設計層做出了較為細致的約束[8]。模型假設CUDA線程在物理上獨立的GPU上執行,GPU作為主機的協處理器,采取異構并行的模式,并行計算的內核程序在GPU上執行,程序的其它部分在CPU上執行。因為GPU設備不具備顯示功能,因此數據需要在顯存和內存之間由PCIe總線進行交互,受限于通用計算機的速度限制,在大規模數值計算中,數據傳輸時間占了程序大部分執行時間,圖5所示為不同數據規模下并行加的計算時間,在數據規模較小時,數據幾乎占了程序總執行時間99%以上,因此,只有在計算規模較大時,才能體現GPU計算的優勢。

圖5 并行求和運算時間對比

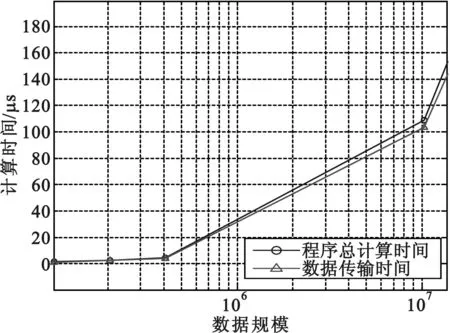

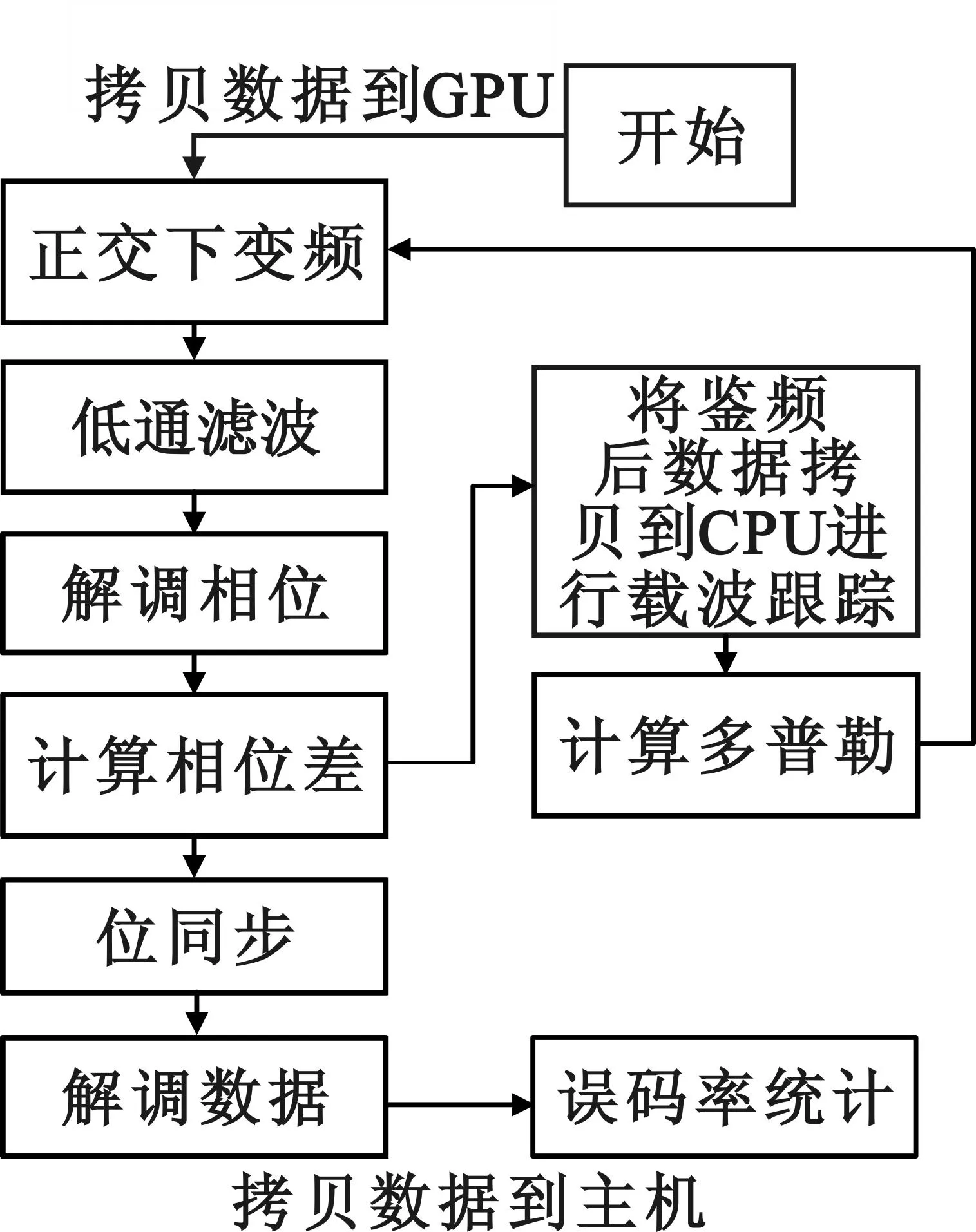

根據CUDA平臺這一特點,數字通信系統并行計算模型中,應盡量減少數據傳輸,充分發揮GPU高性能計算能力。如圖6所示,程序執行開始,將需要處理的數據全部轉至顯存,全部大規模計算由GPU完成,CPU和GPU在程序執行過程中,只進行少量數據傳遞,CPU只進行小規模的計算和數據監視和顯示功能。

圖6 基于GPU的數字通信并行計算模型

3數字調相信號并行解調程序設計

3.1數字調相信號解調算法結構

根據2.2節的并行計算模型和Costas環解調結構,數字調相信號并行解調算法[9-11]如圖7示。

圖7 基于CUDA的數字調相信號并行解調算法模型

中頻采樣數據從CPU讀取并傳輸到GPU,在GPU中完成數字正交下變頻、低通濾波、位同步、鑒相、環路濾波和譯碼;環路濾波后的相位誤差信號傳輸回CPU計算多普勒頻移,多普勒頻移再傳回GPU修正NCO輸出的正、余弦波形;GPU譯碼后的數據再傳回CPU進行顯示和存儲。見圖8。

圖8 算法流程

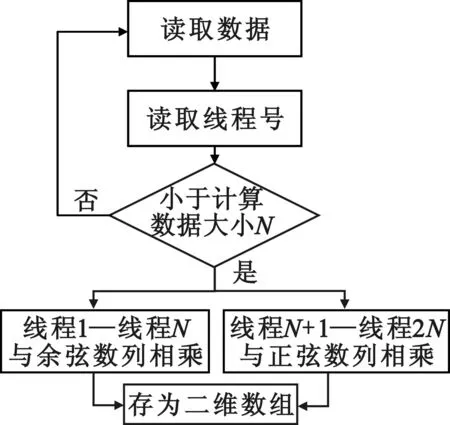

3.2混頻器設計

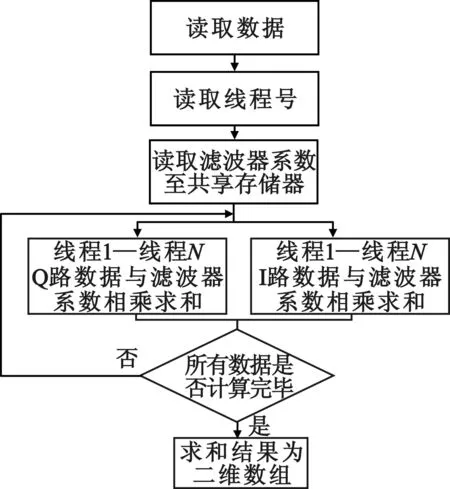

混頻器就是把信號從中頻搬移到基頻,是軟件無線電的核心,通常硬件上采用數控振蕩器(NCO)產生本地數字載波進行混頻。并行混頻時,對應數據點與對應相位的正弦和余弦波形采樣點做乘法,并行程序算法如圖9所示。

圖9 變頻器算法流程

混頻器偽代碼如下:

__global__ voidDownfreqKernel()

Begin

int tid = blockIdx.x * blockDim.x + threadIdx.x;

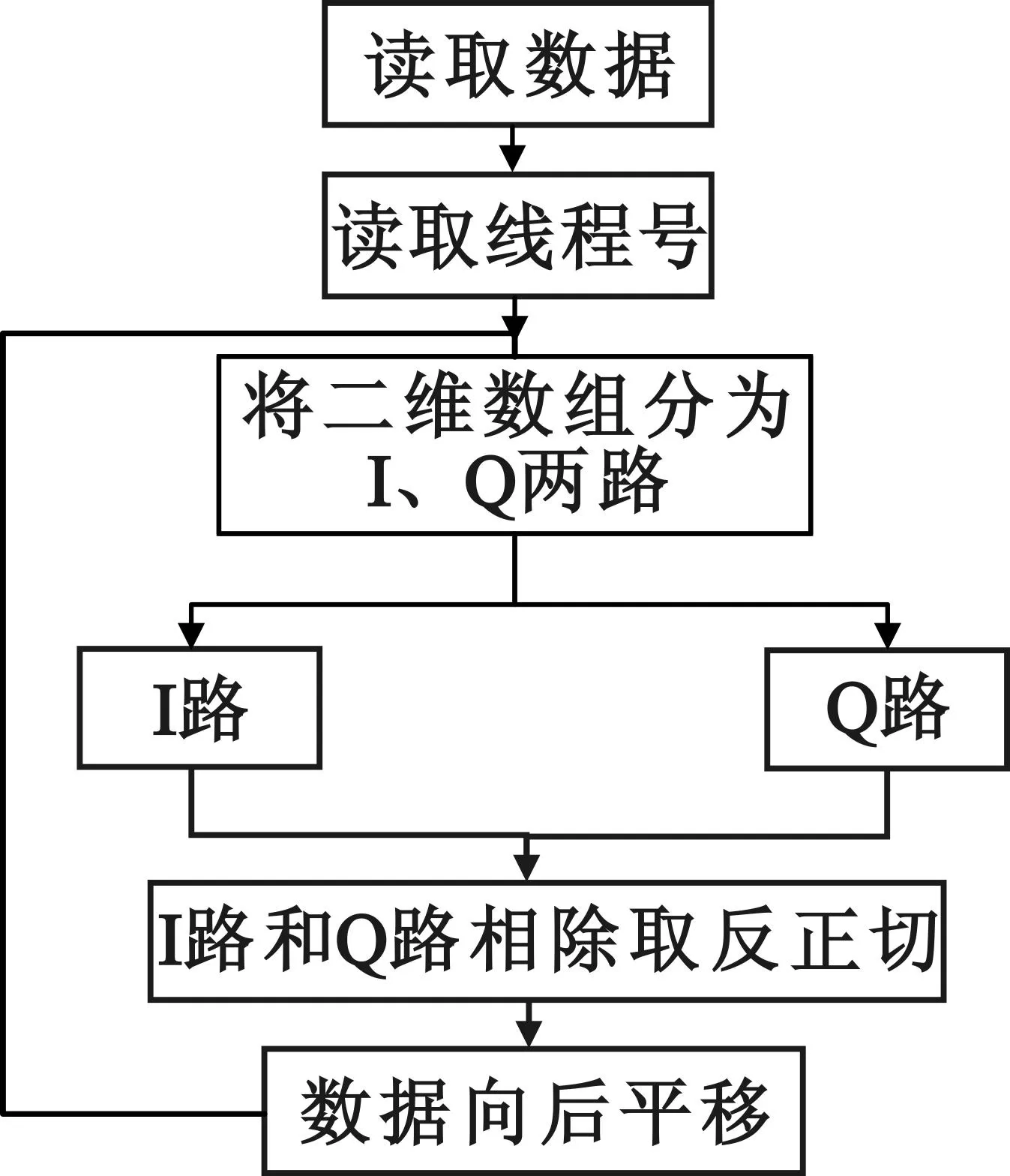

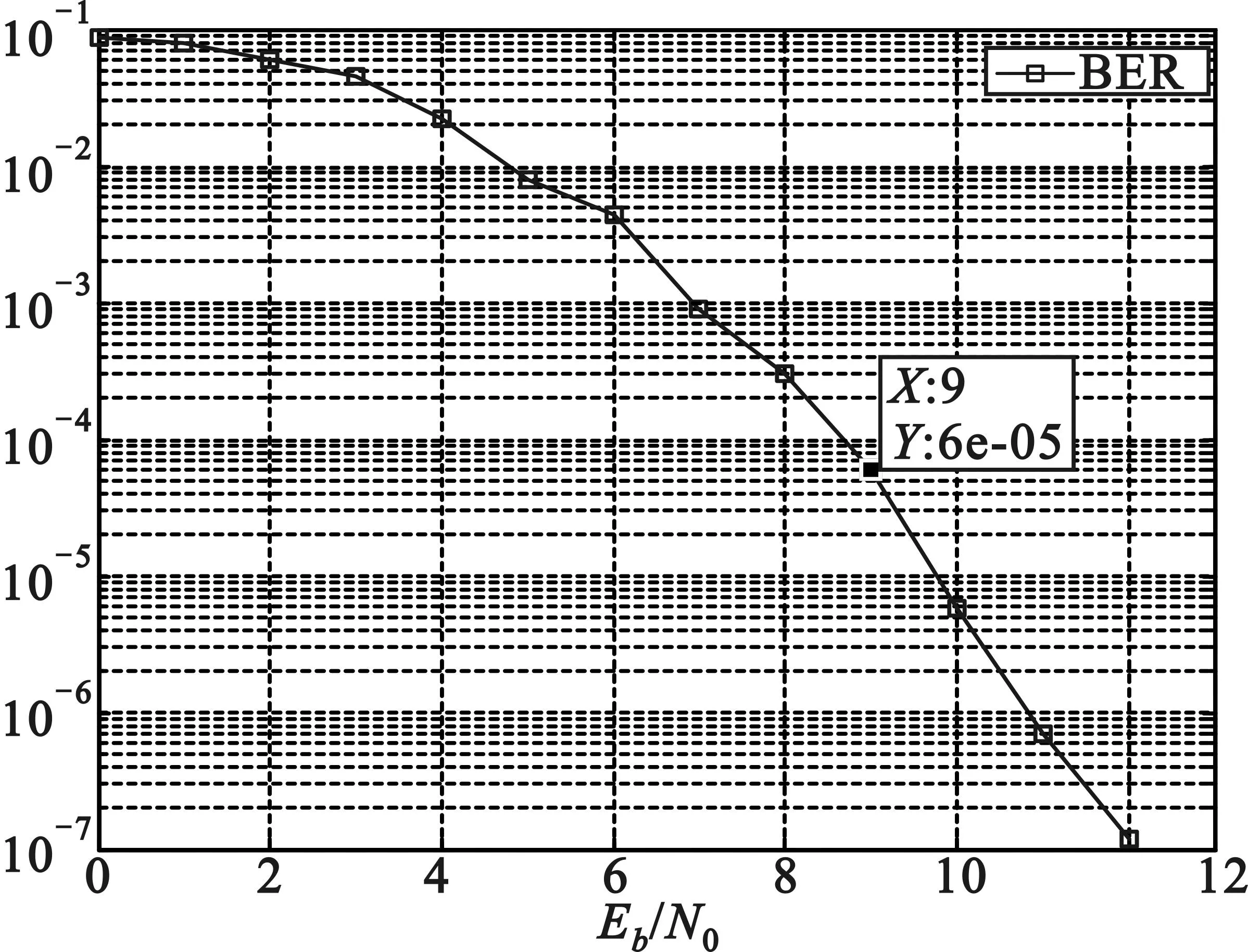

if (tid downfreq[tid].x = chandata[tid]*cos(2*PI*(fb+phasefd)); downfreq[tid].y = chandata[tid]*sin(2*PI*(fb+phasefd)); End 3.3濾波器設計 FIR濾波器以其良好的群延遲性被廣泛應用在數字通信系統中,其可以保證任意幅頻特性的同時具有嚴格的線性相頻特性,同時其具有有限長沖擊響應,算法如圖10所示。 圖10 濾波器算法流程 濾波器偽代碼如下: __global__ void GPUFilterKernel() Begin __shared__ float2 cache[]; inttid = threadIdx.x + blockIdx.x * blockDim.x; cache[threadIdx.x].x=signal[tid].x; cache[threadIdx.x].y=signal[tid].y; __syncthreads(); float sumx=(cache[threadIdx.x].x+ ……+cache[threadIdx.x+16].x)*f.a; float sumx=(cache[threadIdx.y].y+ ……+cache[threadIdx.x+16].x)*f.a; result[tid].x=sumx; result[tid].y=sumy; End 3.4鑒相器設計 鑒相器主要完成鑒別輸入信號相差的功能,是鎖相環路的關鍵,在并行程序設計中,主要依靠求解前后采樣點相差的辦法,算法如圖11所示。 圖11 鑒相器算法流程 鑒相器偽代碼如下: __global__ void ComputeSubphaseKernel() Begin inttid = threadIdx.x + blockIdx.x * blockDim.x; data[tid] = atan2(-src[tid].y,src[tid].x); data[tid] = src[tid+1]-src[sid]; if (data[tid]>PI) data[tid] -= 2*PI; else if (data[tid]<-PI) data[tid] += 2*PI; End 3.5測試結果 測試硬件平臺選用NIVIDIA Tesla K20顯卡,輸入數據1 ms模擬數據,計算時間在1.7 ms以內,如圖12所示,程序能夠正確解調原數據,在Eb/N0=9.6 dB時誤碼率可以達到10-5。 圖12 基于CUDA的BPSK信號并行解調結果 4結語 在通用計算機平臺上實現數字調相信號的接收解調,降低了系統設計、開發的難度和成本,軟件化的處理方式增加了系統的靈活性,通過加載不同的軟件,可以實現更多的功能。通過硬件的升級和重組,還可以進一步提高系統性能。可見基于通用計算機平臺,尤其是基于CUDA的數字信號處理是信號處理的一個重要發展方向,也是計算機應用的新趨勢和研究的新領域。 參考文獻: [1]王曉琴,黑勇.軟件無線電硬件體系結構研究[J].科學技術與工程,2006,16(13):1820-1824. WANG Xiao-qin,HEI Yong.A Study of Software Radio Hardware Architecture[J].Science Technology and Engineering,2006,16(13):1820-1824. [2]Sklar Bernard.Digital Communications[M].北京: 電子工業出版社,2006:538-542.Sklar Bernard.Digital Communications[M].Beijing: Publishing House of Electronics Industry,2006:538-542. [3]劉艷華.Costas環法BPSK信號解調的研究與實現[J].通信技術,2012,45(01):16-21. LIU Yan-hua.Research and Implementation of BPSK signal Demodulation based on Costas[J].Communications Technology.2012,45(01):16-21. [4]季仲梅,楊洪生,王大鳴等.通信中的同步技術及應用[M].北京:清華大學出版社,2008:111-117. JI Zhong-mei,YANG Hong-sheng,WANG Da-ming,et al.Synchronization Technology and Application in Communication[M].Beijing: Tsinghua University Press,2008:126-128. [5]方浩華,王躍林,徐會勤等.基于DSP的DPSK差分解調的實現與研究[J].移動通信,2003增刊:79-84. FANG Hao-hua,WANG Yue-lin,XU Hui-qin,et al.Research on DPSK Difference Demodulation based on the DSP Implementation[J].Mobile Communications,2003(Supplement.):79-83. [6]Riter S.An Optimum Phase Reference Detector for Fully Modulated Phase Shift Keyed Signal[C].IEEE AES-5,1969,4(7):11-17. [7]NVIDIA Corp.NVIDIA CUDA Programming Guide 5.0[S].http://www.nvidia.com/object/cuda_Develop.html. [8]陳國良,孫廣中,徐云等.并行算法研究方法學[J].計算機學報,2008,31(09):1493-1502. CHEN Guo-liang,SUN Guang-zhong,Xu Yun,et al.Methodology of Research on Parallel Algorithms[J].Chinese Journal of Computers,2008,31(09):1493-1502. [9]Core Mark T,Tan Harry H.BER for Optical Heterodyne DPSK Receivers Using Delay Demodulation and Integration Detection[J].IEEE Transactions on Communications,2002,50(1):1451-1459. [10]LI Gui-xin.,AN Zhi-qi.,YUAN Si-jie.Study on Software Demodulation of DQPSK Signal based on Digital Phase Measurement[J].Journal of Spacecraft TT&C Technology.2008,27(2): 1105-1110. [11]Mitra S K.Digital Signal Processing,A Computer-Based Approach[M].Second Edition,MeGraw-Hill Companies,Inc.,2001. Parallel Programming of PSK Signal Demodulation based on CUDA LIU Yan-du1,ZHENG Hai-xin1,WANG Xiao-ping2 (1.Equipment Academy,Beijing 101416,China;2.Unit 76160 of PLA,Guangzhou Guangdong 510000,China) Abstract:To implement digital communication receiving/demodulation on the general computer is an important research direction in the field of signal processing in recent years.Parallelism of the algorithm for BPSK signal demodulation with high real-time requirements is analyzed and implemented on the general computer.Based on the characteristics of "CPU + GPU" heterogeneous computing platform,the parallel computation model for digital phase modulation signal is proposed,and based on CUDA platform,the parallel-program modules of mixer,phase discriminator and filter are designed,thus to realize the BPSK signal demodulation.Experiment results show that the computing time ratio of 1:1.7,the BER of 10-5when SNR=9.6 dB could be reached,well-matched with those by special hardware demodulation,and in particular,the implementation method by general computer is more flexible,and easier for function extension. Key words:digital phase modulation signal; demodulation ; CUDA; parallel doi:10.3969/j.issn.1002-0802.2016.02.020 * 收稿日期:2015-09-10;修回日期:2015-12-20Received date:2015-09-10;Revised date:2015-12-20 中圖分類號:TN911.7 文獻標志碼:A 文章編號:1002-0802(2013)08-0227-06 作者簡介: 劉燕都(1986—),男,碩士研究生,主要研究方向為高速數字信號處理,航天測控技術; 鄭海昕(1974—),女,碩士,副教授,主要研究方向為航天測控技術,空間數據傳輸; 王小平(1987—),男,學士,主要研究方向為高速信號處理,空間信息傳輸。