PIN光電探測器用反外延片工藝研究

李 楊,李明達

(中國電子科技集團公司第四十六研究所 天津300220)

PIN光電探測器用反外延片工藝研究

李 楊,李明達

(中國電子科技集團公司第四十六研究所 天津300220)

創新性使用反外延法工藝,介紹了適用于制備近紅外波段PIN光電探測器的硅外延材料的研制工藝,在區熔單晶拋光片上進行重摻導電層和支撐層的外延層制備。通過對硅源流量與摻雜劑濃度的精確控制,實現了快速外延生長和高濃度摻雜。通過精細的后期加工工藝,將高阻區熔層加工為厚度和表面質量均滿足器件要求的有源層。結果顯示,采用反外延法工藝得到的反外延材料片應用到PIN光電二極管中,不僅節省器件制備中的工藝程序,而且大大提高了器件耐壓性。

PIN光電探測器 反外延片 重摻導電層 支撐層

0 引 言

光電探測器在軍事和國民經濟的各個領域有著廣泛用途,例如:在可見光或近紅外波段主要用于射線測量和探測、工業自動控制、光度計量等;在紅外波段主要用于導彈制導、紅外熱成像、紅外遙感等方面。通常禁帶寬度或雜質離化能合適的半導體材料都具有光電效應,但是制造實用性器件還要考慮性能、工藝、價格等因素。一般用于可見光波段的光電導探測器材料有CdS、CdSe、CdTe、Si、Ge等;近紅外波段有PbS、InGaAs、PbSe、InSb、Hg0.75Cd0.25Te等;大于8,μm的波段有Hg1-xCdxTe、PbxSn1-x、Te、Si摻雜、Ge摻雜等;其中,CdS、CdSe、PbS等材料可以制成多晶薄膜形式的光電導探測器。最普通的光電探測器為PIN光電二極管。其結構如圖1所示。

圖1 外加反向偏置電壓的PIN光電二極管的電路示意圖Fig.1Diagram of additional reverse bias voltage of PIN photodiode circuit

光電探測器的工作原理為光電效應,當一個入射光子能量大于或等于半導體的帶隙能量時,將激勵價帶上的一個電子吸收光子的能量而躍遷到導帶上,此過程產生自由的電子-空穴對。在光電二極管的PN結中間引入一層濃度很低的N型半導體,就可以增大耗盡區的寬度,達到減小擴散運動影響,提高響應速度的目的。由于這一摻入層的摻雜濃度低,近乎本征半導體,故稱I層,因此這種結構成為PIN光電二極管。I層較厚,幾乎占據了整個耗盡區。絕大部分的入射光在I層內被吸收并產生大量的電子-空穴對。在I層兩側是摻雜濃度很高的P型和N型半導體,P層和N層很薄,吸收入射光的比例很小。因而光產生電流中漂移分量占了主導地位,這就大大加快了響應速度。[1]

由于硅材料的物理特性,應用本征高阻硅外延片(電阻率>1,000,?·cm,厚度:50~100,μm)制備的PIN光電二極管主要應用于民品領域;近紅外探測器對硅材料要求極高——超高電阻率、超厚層,外延工藝無法實現。長期以來,器件研究單位均采用區熔單晶作基底,但是由于接觸電阻過大,器件性能受到極大的制約。

本文轉換設計思路,采用反外延工藝,即與普通的外延片用法相反,把外延層作為襯底,而把襯底作為制作器件PN結的區域。整個材料制備過程為:選用器件所需電阻率的區熔單晶為襯底,在高阻區熔襯底上利用外延工藝生長重摻導電層和支撐層,為器件制造提供電極及物理支撐層,利用減薄和機械化學拋光工藝將高阻區熔層加工為厚度、表面質量符合要求的有源層,為其提供N型反外延材料。其優點為:制作PN結的區域(區熔單晶襯底區域)電阻率可達到幾千?·cm,接近于絕緣體,并且厚度可通過后期加工至器件要求值,可大大提高器件的耐壓性,降低器件的插損;外延層作為基底層,需盡量降低串聯電阻,外延層濃度需在1018,cm-3以上,并且外延層要有一定厚度,防止碎片。

1 工藝實驗

1.1 外延設備

硅外延的沉積設備為意大利LPE公司生產的PE-3061D平板式外延爐,基本結構如圖2所示。該外延爐采用高頻感應的加熱方式,具有維護簡單、生產效率高的特點,是目前各外延制造企業主流的15.24~20.32,cm硅外延片的生產設備。此設備為單圈平板爐,每爐可生產8片15.24,cm外延片。

圖2 PE3061D平板式外延爐結構圖Fig.2 Plate-type epitaxial furnace structure of PE3061D

1.2 工藝技術

本文采用常壓外延工藝,反應室壓力維持在0.1,MPa。采用高純度三氯氫硅(SiHCl3)作為硅源,腔內反應化學式如下:

反應氣體H2經過純化器的純化,純度可以達到6,N以上,生長溫度保持在1,150,℃。

2 實驗結果及分析

在反外延材料片的制備過程中,面臨的難點有3個方面:①如何實現厚層外延片的快速生長;②如何得到低電阻率的重摻導電層;③如何對反外延片進行加工,使其厚度、表面質量符合要求。本文針對上述3個方面開展了大量實驗工作。

2.1 快速外延生長

根據外延生長機理,影響外延生長速率的因素主要有硅源濃度和外延生長溫度。[2-3]為了提高外延生長速率,從這兩方面著手試驗。首先為了提高硅源的濃度,嘗試4種不同硅源流量,記錄其生長速率。同時,適當提高外延反應溫度,以提高外延生長速率。從改變外延生長溫度和硅源流量著手,以不同的生長條件進行了13組實驗,生長速率結果及外延表面狀況如表1所示。

根據表1的前5組實驗測試結果,繪制出圖3所示的曲線。可以看出,在1,110,℃時,隨著硅源流量的增大,外延生長速率也隨著增加,當SiHCl3的流量增加到30,g/min前,生長速率增長最快;繼續增加SiHCl3流量至35,g/min后,增長趨緩。這是由于隨著硅源濃度的增加,外延反應的副產物HCl的濃度也增加,腐蝕作用增強,生長速率增長趨勢減緩。同時使用過大的硅源流量,因溫度固定,表面遷移速率過小,外延層結晶質量變差,外延層表面出現層錯。

表1 外延生長速率工藝試驗條件Tab.1 Test conditions for epitaxial growth rate process

圖3 硅源流量與生長速率關系曲線Fig.3 Relationship between the growth rate curves and silicon source traffic

但從上面結果來看,硅源流量過大時,因溫度過低,表面質量變差,出現霧狀表面缺陷。所以本文針對高SiHCl3流量的3種規格(30,g/min、35,g/min、40,g/min)相應提高工藝溫度,相應結果在表1中列出。當硅源流量一定時,升高溫度,生長速率增大,但溫度過高時,外延表面會出現滑移線等表面缺陷。當硅烷流量達到40,g/min,溫度升高至1,170,℃時,結晶質量仍然較差。

本文主要針對高速外延生長,從實驗結果發現,在35,g/min的硅源流量下,溫度控制在1,130~1,150,℃范圍生長出結晶質量較好的外延片,生長速率為2.27,μm/min。這也是研究中在生產重摻導電層和支撐層時最終采用的主工藝條件。

2.2 高濃度摻雜

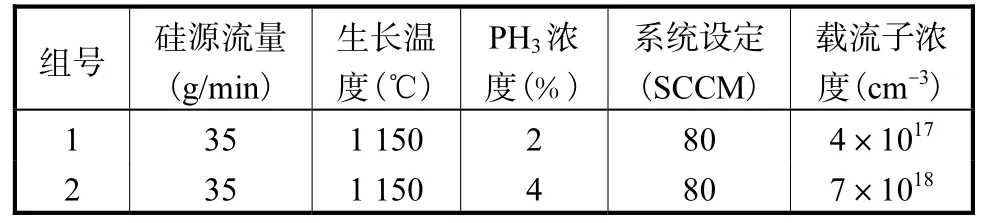

硅外延摻雜劑的摻入,受含摻雜劑氣體的輸入分壓、生長溫度和生長速率的影響[4-5],而輸入分壓是決定因素。本文所研制的PIN光電二極管用硅反外延材料,外延層摻雜濃度要求在4.7×1018,cm-3以上,屬高濃度摻雜。由于硅外延層的摻雜濃度受摻雜劑氣體的輸入分壓影響較大,因此從提高摻雜劑的輸入分壓入手。實驗選用了常規的磷烷做n型摻雜劑,先后采用含量為2%,和4%,的磷烷分別進行了實驗,結果如表2所示。發現當把系統設定在一個較高值,即采用4%,濃度的PH3時,載流子濃度為7×1018,cm-3,達到參數指標要求。

表2 外延生長不同磷烷濃度工藝試驗Tab.2Epitaxial growth process under different concentrations of phosphine

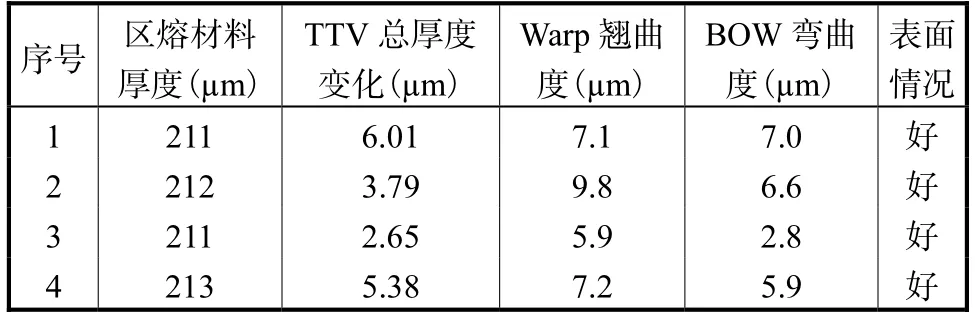

2.3 反外延片后期加工

使用外延工藝在區融襯底上得到重摻導電層和支撐層之后,研究人員對反外延片進行后道加工,使其厚度和表面質量滿足器件使用要求。采用減薄機對外延片進行減薄,之后通過機械化學拋光去除表面損傷層、優化幾何參數和表面質量。最終加工結果如表3所示。區熔材料厚度維持在(212±1)μm,總厚度變化、翹曲度、彎曲度都在10,μm以內,表面達到免洗水平。

表3 反外延片加工最終結果Tab.3 Anti-epitaxial wafer processing and the final result

3 結 論

通過增加反應原材料濃度和適當提高溫度的方法來提高外延生長速率,最終得到2.27,μm/min的生長速率,成功研制出超厚外延層的外延片。同時采用提高磷烷輸入分壓的方法,解決重摻導電層超高濃度摻雜的問題。最后對反外延片進行后期精細加工,使區熔層的表面質量達到較高水平。經過以上方案,成功研制出厚度為200,μm、摻雜濃度4.7×1018,cm-3以上的重摻導電層;厚度150,μm以上的支撐層。反外延片應用到PIN光電二極管中,不僅節省了器件制備中的工藝程序,而且大大提高了器件的耐壓性。

[1] 江利. 微波PIN二極管的設計與制備工藝研究[D].合肥:合肥工業大學,2005.

[2] 王鵬. 外延層的工藝控制與實際應用[D]. 天津:天津大學,2012.

[3] 甄可龍. 硅外延生長電阻率與厚度一致性的研究[D].天津:河北工業大學,2003.

[4] 張文清. 6英寸IGBT用硅外延材料制造工藝的設計與實現[D]. 南京:東南大學,2011.

[5] 郭銳. 毫米波雪崩管用硅外延材料的研究及應用[D].南京:東南大學,2010.

On Preparation Technology of PIN Photodetector with Anti-Epitaxial Wafer

LI Yang,LI Mingda

(The 46th Research Institute of China Electronics Technology Group Corporation,Tianjin 300220,China)

This paper introduces the research of silicon epitaxy material process applicable to the near infrared band PIN photodetector by using the anti-epitaxy method of process innovation ideas to carry out epitaxial layer preparation for heavy doped conductive layer and support layer on FZ monocrystalline polished wafer.Through a precise control of silicon source flow and dopant concentration,rapid epitaxial growth and high concentration of doping were achieved.By using elaborate post-processing technology,the high resistance zone melting layer thickness and surface processing for active layer quality can satisfy the requirements of the device.The results show that with the application of anti-epitaxial material to PIN photoelectric diode,not only can device preparation process be saved,but also voltage resistance of the device greatly improves.

PIN photodetector;anti-epitaxial wafer;heavy doped conductive layer;support layer

TN304

:A

:1006-8945(2016)04-0034-03

2016-03-11