基于SOC平臺(tái)的XMC模塊設(shè)計(jì)與實(shí)現(xiàn)

潘 波,李 彪(重慶金美通信有限責(zé)任公司,重慶 400030)

?

基于SOC平臺(tái)的XMC模塊設(shè)計(jì)與實(shí)現(xiàn)

潘 波,李 彪

(重慶金美通信有限責(zé)任公司,重慶400030)

摘 要:altera的cycloneV系列SOC FPGA內(nèi)嵌了一個(gè)雙核ARM Cotex-A9處理器,處理器部分與FPGA邏輯部分集成在一個(gè)芯片里面,提高了芯片的集成度,為設(shè)備的小型化設(shè)計(jì)提供了便利。XMC架構(gòu)作為VITA組織推薦的模塊架構(gòu),廣泛使用在VPX板卡上。首先介紹了altera的SOC平臺(tái)和基于VITA42標(biāo)準(zhǔn)的XMC模塊架構(gòu),然后通過(guò)擴(kuò)展處理器外設(shè),在處理器平臺(tái)上實(shí)現(xiàn)了linux操作系統(tǒng)并完成驅(qū)動(dòng)設(shè)計(jì),實(shí)現(xiàn)了基于該平臺(tái)的數(shù)據(jù)處理模塊,最后測(cè)試了模塊搭載的CPU性能和FPGA擴(kuò)展SerDes的性能。

關(guān)鍵詞:SOC技術(shù);XMC模塊;CycloneV芯片;VITA42標(biāo)準(zhǔn);Cotex-A9處理器;QuartusII工具

1 引 言

altera的cycloneV SOC FPGA是一個(gè)片上系統(tǒng),包含了硬核處理器系統(tǒng)(HPS)和FPGA邏輯系統(tǒng)。SOC FPGA在cycloneV中有SX、SE、ST三種系列[1]。HPS包含了一個(gè)雙核ARM Cotex-A9微處理器,F(xiàn)LASH存儲(chǔ)器控制器,SDRAM控制器,片上緩存,外設(shè)接口,調(diào)試接口,鎖相環(huán)等[2]。FPGA部分包含F(xiàn)PGA邏輯單元,控制單元,鎖相環(huán)單元,高速收發(fā)器,PCIe控制器等。

在VPX計(jì)算機(jī)系統(tǒng)中,外圍功能模塊通常采用XMC載板與模塊配合的方式實(shí)現(xiàn),其中載板主要提供接口功能[3],XMC模塊主要實(shí)現(xiàn)數(shù)據(jù)處理功能,不同功能的載板和XMC模塊可以組合成具有不同功能的VPX板卡。本設(shè)計(jì)將SOC FPGA的處理器部分和邏輯處理做成公用的XMC模塊提供給VPX系統(tǒng)使用。

2 原理框圖

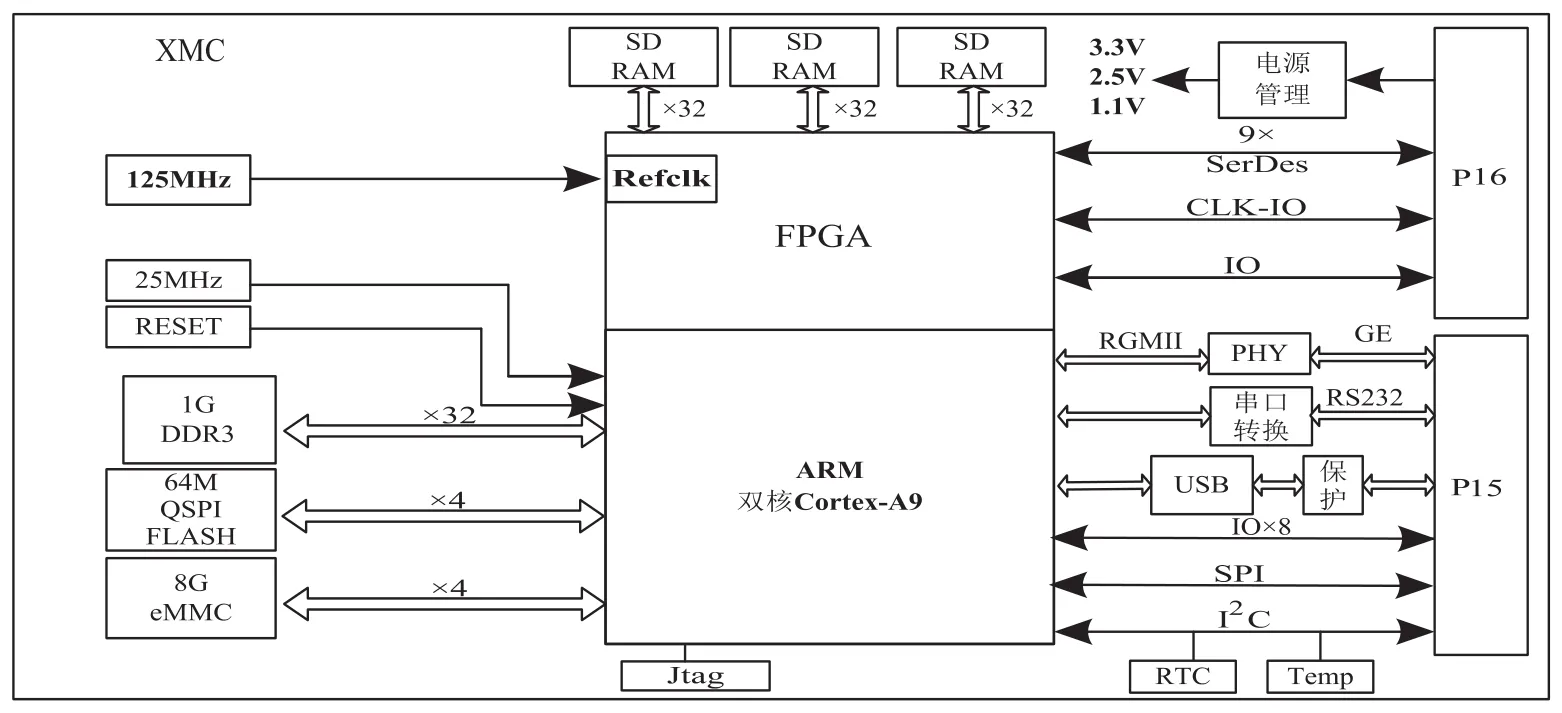

XMC模塊的原理框圖如圖1所示。

圖1 原理框圖

HPS處理器系統(tǒng),包含F(xiàn)PGA內(nèi)嵌的一個(gè)Cortex-A9雙核處理器核、1GByte DDR3內(nèi)存、64MByte QSPI FLASH存儲(chǔ)器、8G eMMC存儲(chǔ)器、時(shí)鐘、復(fù)位、調(diào)試接口等[4],并通過(guò)接口擴(kuò)展了如下外設(shè):

a)通過(guò)高通的AR8031以太網(wǎng)phy和以太網(wǎng)變壓器擴(kuò)展了1路10M/100M/1000M以太網(wǎng)接口;

b)通過(guò)MX3223擴(kuò)展了2路RS232串口;

c)通過(guò)USB3300 USB phy芯片擴(kuò)展了USB-OTG接口;

d)其他還擴(kuò)展了SPI、I2C、溫度測(cè)量、實(shí)時(shí)時(shí)鐘等。

FPGA內(nèi)嵌的ARM處理器情況如下:

a)Dual-core ARM 32bit Cortex-A9 MPCore processor;

b)4,000 MIPS(CPU頻率:800MHz);

c)每個(gè)核32KB L1 data caches和32KB L1 data caches;

d)512KB共享L2 cache;

e)浮點(diǎn)協(xié)處理器(VFP)。

使用FPGA的高速收發(fā)器SerDes擴(kuò)展4路千兆以太網(wǎng)接口對(duì)外,擴(kuò)展4路SGMII接口通過(guò)背板與機(jī)內(nèi)交換芯片連接,搭載三片32MByte的SDRAM用于以太網(wǎng)數(shù)據(jù)緩存,通過(guò)FPGA的I/O擴(kuò)展槽位信息。

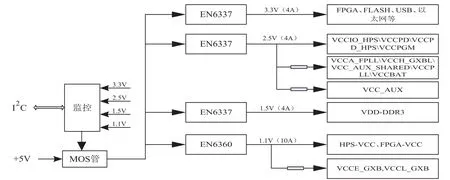

電源部分設(shè)計(jì)對(duì)該模塊非常重要,選用三片EN6337模塊產(chǎn)生3.3V、2.5V、1.5V,其中2.5V部分電源需要濾波后供電。使用電源模塊EN6360產(chǎn)生1.1V給HPS和FPGA內(nèi)核供電。其框圖如圖2所示。

圖2 電源框圖

3 啟動(dòng)過(guò)程

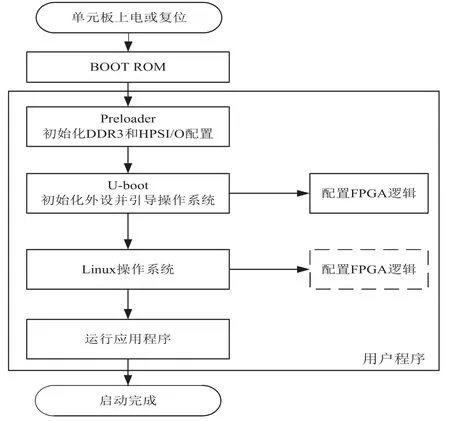

系統(tǒng)啟動(dòng)流程如圖3所示,啟動(dòng)流程如下:

a)單元板上電或者CPU復(fù)位后處理器開(kāi)始啟動(dòng)。

b)CPU從片上的BOOT ROM讀取啟動(dòng)代碼,這部分啟動(dòng)程序固化在芯片里面。啟動(dòng)代碼主要完成讀取啟動(dòng)模式管腳,然后從對(duì)應(yīng)的存儲(chǔ)器啟動(dòng)。

c)從QSPI FLASH的0x0地址啟動(dòng)Preloader程序,初始化DDR3內(nèi)存和HPS的I/O配置。

d)從QSPI FLASH的0x4000地址啟動(dòng)U-boot,初始化CPU外設(shè),比如:以太網(wǎng)接口、NAND FLASH、NOR FLASH等。

e)通過(guò)U-boot引導(dǎo)linux操作系統(tǒng),操作系統(tǒng)采用Linux3.10。

f)系統(tǒng)啟動(dòng)完畢后,引導(dǎo)應(yīng)用程序。

g)在Preloader、U-boot、linux操作系統(tǒng)里面都可以配置FPGA邏輯,第一次配置邏輯選擇在U-boot里面進(jìn)行,Linux操作系統(tǒng)用于動(dòng)態(tài)配置FPGA邏輯。

圖3 啟動(dòng)流程

4 XMC模塊設(shè)計(jì)

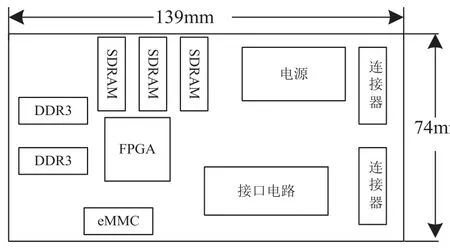

將上面所述的電路按照VITA42的標(biāo)準(zhǔn)制作成XMC模塊,模塊尺寸為:長(zhǎng)×寬= 139mm× 74mm[5]。PCB布局如圖4所示,F(xiàn)PGA在居中靠左的位置,它周邊主要有2片DDR3存儲(chǔ)器組合成1G內(nèi)存,3片單片32M的SDRAM存儲(chǔ)器,一個(gè)8G的eMMC大容量存儲(chǔ)器,1片SPI FLASH。其他地方主要分布有電源轉(zhuǎn)換,RS232接口轉(zhuǎn)換,以太網(wǎng)接口電路,USB接口電路等。

圖4 XMC模塊框圖

5 軟件系統(tǒng)搭建

采用altera公司提供的quartus II 13.1與Qsys圖形化開(kāi)發(fā)工具配合使用,搭建了硬件架構(gòu)與FPGA邏輯[6]。通過(guò)Qsys軟件可以圖形化設(shè)置DDR3內(nèi)存參數(shù),管理外設(shè)的管腳配置,處理器時(shí)鐘頻率設(shè)置等,根據(jù)設(shè)置,自動(dòng)生成preloader用于引導(dǎo)系統(tǒng)。在系統(tǒng)中搭建了一個(gè)avalone總線橋,掛載到HPS 的AXI總線上,將AXI總線引到FPGA邏輯里面,這樣CPU就可以方便的訪問(wèn)FPGA邏輯。

該平臺(tái)采用Linux3.10操作系統(tǒng),經(jīng)過(guò)定制化裁剪后運(yùn)用到模塊上[7]。Linux系統(tǒng)里面主要包含了Linux內(nèi)核,內(nèi)存管理系統(tǒng),F(xiàn)LASH驅(qū)動(dòng),千兆以太網(wǎng)驅(qū)動(dòng)及TCP/IP協(xié)議棧,標(biāo)準(zhǔn)的USB驅(qū)動(dòng)及協(xié)議棧,RS232驅(qū)動(dòng),SD卡驅(qū)動(dòng),SPI和I2C驅(qū)動(dòng)等。掛載了基于BusyBox架構(gòu)的嵌入式文件系統(tǒng),管理模塊上的QSPI FLASH和eMMC存儲(chǔ)器。

6 性能測(cè)試分析

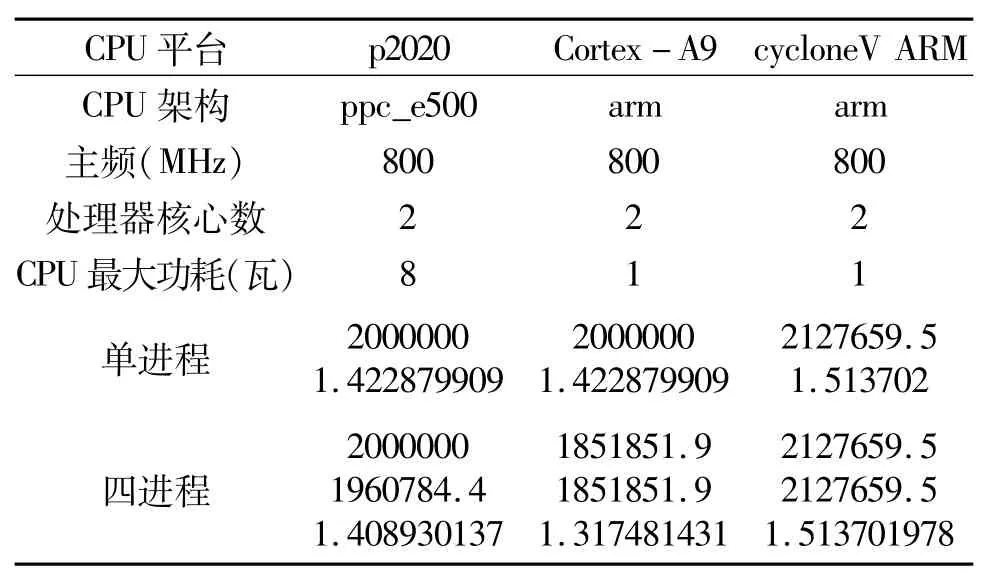

使用Dhrystone 2.1工具對(duì)處理器性能進(jìn)行測(cè)試[8]。該工具主要包含賦值,基本運(yùn)算(assignments),占總測(cè)試52(51%);控制語(yǔ)句(control statements),占總測(cè)試33(33%);函數(shù)(系統(tǒng)函數(shù)、用戶(hù)函數(shù))調(diào)用(procedure,function calls),占總測(cè)試17 (17%)。測(cè)試結(jié)果與常用的P2020和Cortex-A9處理器進(jìn)行對(duì)比。測(cè)試了每秒執(zhí)行的計(jì)算次數(shù);單位時(shí)鐘周期機(jī)器運(yùn)行的速度對(duì)應(yīng)“DMIPS/MHz”,計(jì)算方式為:機(jī)器運(yùn)行值/1757/機(jī)器CPU速度。

使用存儲(chǔ)器測(cè)試工具測(cè)試了eMMC和QSPI FLASH的寫(xiě)入速度。eMMC,write:4.76MB/s;QSPI FLASH,write:5.9MB/s。

經(jīng)過(guò)上面的對(duì)比測(cè)試可以看到cylcone5內(nèi)嵌的處理器與飛思卡爾的基于PowerPC架構(gòu)的P2020和基于ARM架構(gòu)的A9處理器處理性能相當(dāng)。

表1 測(cè)試數(shù)據(jù)

7 結(jié)束語(yǔ)

基于cycloneV的平臺(tái)既提供了較強(qiáng)的處理能力,也有豐富的FPGA處理資源,可以運(yùn)用到各類(lèi)對(duì)集成度要求較高的地方。

采用XMC模塊架構(gòu),主要運(yùn)用到VPX板卡上,也可以運(yùn)用到其他板卡上,作為數(shù)據(jù)處理平臺(tái)。

參考文獻(xiàn):

[1]Altera.Cyclone V Device Handbook[EB/OL].2013/www.alter.com.

[2]Altera.SoC FPGA ARM Cortex-A9 MPCore Processor Advance Information Brief[EB/OL].2013/www.alter.com.

[3]Ray Alderman.STANDARD FOR VITA 42.0[S].American:American National Standards,2008.

[4]李江濤.ARM Cortex-A9的NEON技術(shù)研究及應(yīng)用[J].單片機(jī)與嵌入式系統(tǒng)應(yīng)用,2013,13(3):46-49.LiJiangTao.Research and Utilization of NEON Technology Based on ARM Cortex-A9[J].Microcontrollers & Embedded Systems,2013,13(3):46-49.

[5]胡錦,彭成,譚明.基于VPX標(biāo)準(zhǔn)的PMC/XMC載板設(shè)計(jì)[J].計(jì)算機(jī)測(cè)量與控制,2010,18(8):1852-1855.HuJing,PengCheng,TanMing.Design of PMC/XMC Board Base on VPX Specification[J].COMPUTER MEASUREMENT & CONTROL,2010,18(8):1852-1855.

[6]王瑩.Xilinx可擴(kuò)展處理平臺(tái)[J].電子產(chǎn)品世界,2012,19(2):40-44.Wang Ying.expanded processor platform of Xilinx[J].Electronic Engineering & Product World,2012,19(2):40-44.

[7]劉娟花,厲謹(jǐn).基于FPGA的數(shù)字日歷設(shè)計(jì)[J].現(xiàn)代電子技術(shù),2014(3):15-18.LiuJuanHua,LiJing.Design of digital calendar based on FPGA[J].Modern Electronics Technique,2014,(3):15-18.

[8]張曉靜,華更新,劉鴻瑾.處理器測(cè)試方法研究與實(shí)現(xiàn)[J].現(xiàn)代電子技術(shù),2011,19(3):4-8.ZhangXiaoJing,HuaGengXin,LiuHongJing.Study and Implementation of Test Method[J].Practical Electronics,2014,(3):15-18.

Design and Implementation of XMC Module Based on SOC Platform

Pan Bo,Li Biao

(Chongqing Jinmei Communication Co.,Ltd.,Chongqing 400030,China)

Abstract:The dual-core ARM Cortex-A9 MPCore processor is integrated into the hard processor system of the Altera CycloneV FPGAs.Processor system is integrated with FPGA logic system on a chip so that the integration of chip can be enhanced,and it facilitates the design of miniaturization for equipment.As the recommended module structure of VITA,the XMC architecture is widely used in the VPX board.Firstly,this article introduces the Altera's SOC platform and the structure of XMC module based on the VITA42 standard.Then,the Linux operating system is realized and the driver design is accomplished on the processor platform by expanding processer peripherals.The data processing module based on the platform is realized.Finally,the performance of the CPU on module and SerDers interface extended by FPGA,is tested.

Key words:Technology of SOC;XMC module;CycloneV FPGA;Standard of VITA 42;ARM Cortex-A9 MPCore processor;Tools of quartus II

DOI:10.3969/j.issn.1002-2279.2016.02.006

中圖分類(lèi)號(hào):TP274

文獻(xiàn)標(biāo)識(shí)碼:A

文章編號(hào):1002-2279(2016)02-0017-03

作者簡(jiǎn)介:潘波(1984-),男,重慶市人,碩士研究生,主研方向:主要從事有線通信設(shè)備整機(jī)架構(gòu)研究。

收稿日期:2015-05-29