基于Nios II的導引頭電子艙信號群高速采集系統

秦文姬,李 力(西安工程大學計算機科學學院,西安 710048)

?

基于Nios II的導引頭電子艙信號群高速采集系統

秦文姬,李 力

(西安工程大學計算機科學學院,西安710048)

摘 要:導引頭電子艙是導彈探測、跟蹤目標的部件,是導彈系統的關鍵部分,因此電子艙產品使用前的調試和檢測至關重要。介紹了一種基于Nios II的導引頭電子艙信號群高速采集系統。該系統采用Cyclone II系列EP2C35芯片,以Nios II軟核為核心處理器,完成了對A/D轉換后的30路信號群的高速采集處理。與之前采用PCI總線方案相比,此方案簡化了硬件電路、減小了設備體積、降低了成本,可以滿足不同產品的各種邏輯電平、編碼裝定、參數預置及功能拓展升級的需求,提高了系統的可靠性和智能化分析處理實驗數據的水平。

關鍵詞:電子艙;Nios II軟核;片上可編程系統;SPI核;A/D轉換器ICL7135;數據采集

1 引 言

現有基于PCI總線的導引頭電子檢測臺是集光學、結構支持、機械驅動、電子控制及計算機測量為一體的光機電一體化測控系統設備。它的主要功能是對現有激光類導引頭產品進行生產調試和檢測驗收。但是,該類產品通常硬件電路設計復雜,設備體積大,成本較高。

本項目在原有基于PCI總線的導引頭電子艙檢測系統基礎上,對其控制器部分進行技術改造。本檢測系統的核心設計是在Altera公司Cyclone II系列FPGA芯片上,以Nios II軟核處理器為核心設計一個片上可編程系統(SOPC),代替原核心控制器件-2片8位單片機和CPLD,完成整個檢測系統的控制功能。介紹的基于Nios II的高速數據采集系統是該檢測系統的重要組成部分,主要功能是采集電子艙的響應輸出信號,以便檢驗電子艙是否滿足技術條件規定的指標。

電子艙的響應輸出模擬信號共30路,組成了一個龐大的信號群,數據采集系統需要對這30路信號群進行高速采集處理[1]。信息社會的發展,很大程度上取決于信息與信號處理技術的先進性[2]。一項很有發展前景的技術已經應用于電子產品的檢測中,這就是基于Nios II的SOPC(System On Programmable Chip)技術。Nios II是在Altera公司的FPGA器件上實現的一種32位處理器。Nios II CPU是一種采用流水線技術、單指令流和可配置的通用RISC處理器,它可以與用戶自定義邏輯結合成SOPC系統,被編譯并下載到Altera的可編程器件中去[3]。本系統以Nios II軟核CPU為核心,通過在FPGA上構建可編程片上系統SOPC,利用SOPC系統自定義外設接口,配合DMA技術,同時采用A/D轉換器ICL7135、SOPC系統自帶的FIFO芯片等器件,實現對電子艙信號群高速數據的采集工作。

2 系統結構與工作原理

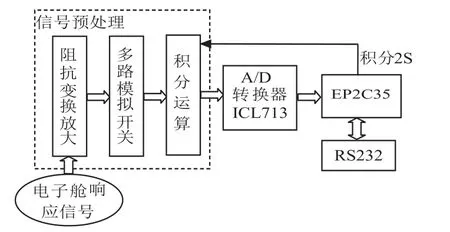

該系統包括信號預處理模塊、A/D轉換模塊、Nios系統電路板等部分,其結構框圖如圖1所示。

圖1 系統總體結構圖

為了能同步采集到電子艙的30路模擬信號,系統需要對信號進行預處理。系統將響應信號經過阻抗變換放大電路、模擬開關陣列和積分運算等電路后,在Nios II CPU的控制下使其按時輸出四組8路模擬信號。接下來將處理后的信號送給A/D轉換器ICL7135,Nios II CPU通過SPI核控制外圍A/D轉換器ICL7135完成數據采集工作。使用Nios系統自定義FIFO緩沖模塊將經過處理的數據緩存起來,DMA完成數據從FIFO到SDRAM的搬移工作,再通過RS-232接口將數據實時傳輸給上位機。

3 硬件電路設計

3.1基于Nios II的EP2C35電路板設計

3.1.1 Nios II處理器配置

選用的Cyclone II EP2C35是一款性能卓越、具有高速以太網接口而且可擴展性極強的優秀片上微控制器,片內集成了4個PLL、52 M4K RAM以及專用高速外設接口[4-5]。采用的Nios II CPU具有大容量窗口的寄存器堆、簡單完備的指令集、強大的尋址模式、較強的可擴展性、硬件輔助等特點。

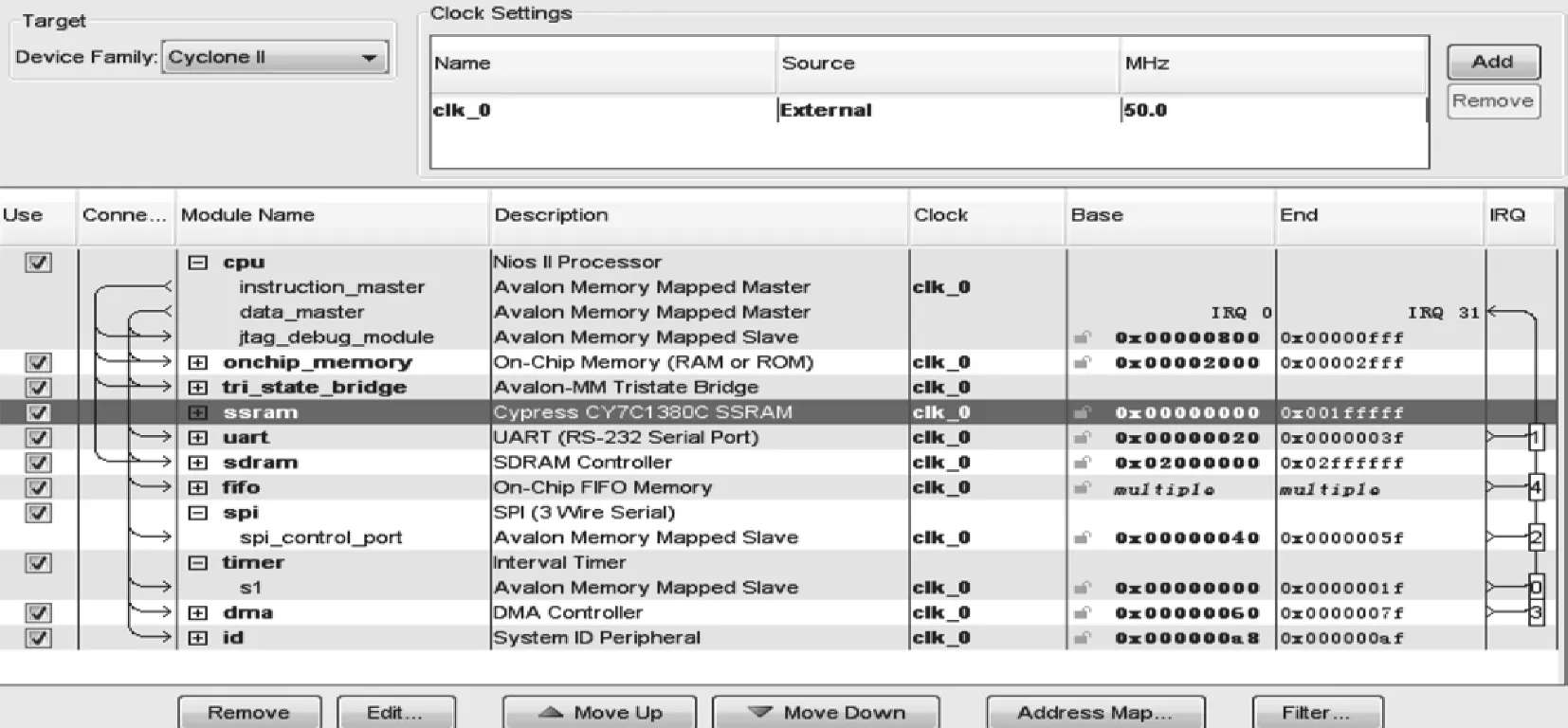

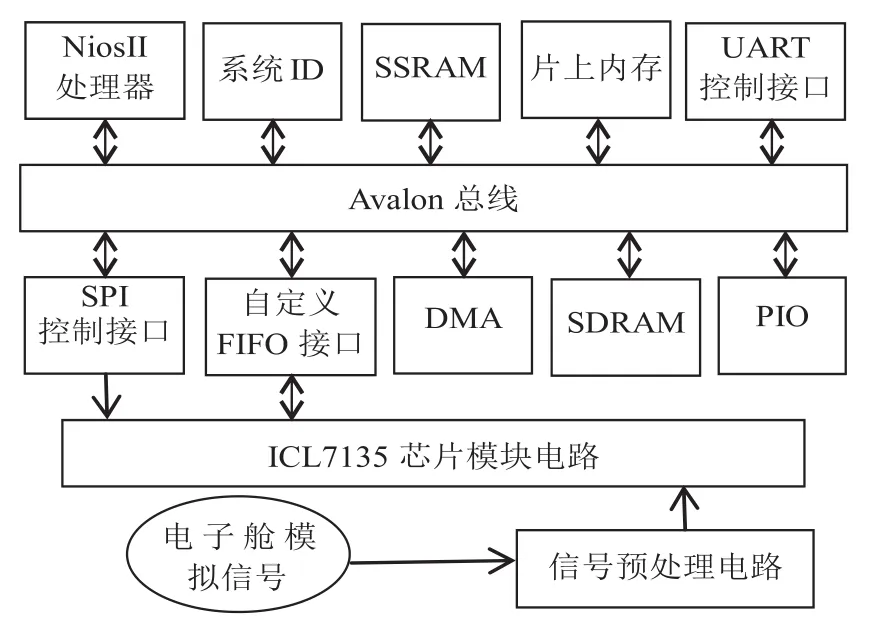

根據系統需求,SOPC系統需包括Nios II處理器、SSRAM、片上內存、SPI控制接口、自定義FIFO接口、用戶PIO、DMA、SDRAM控制器、UART通信接口等。因此,選取Nios II 32bit CPU、On-chip_ Memory、Tri _ state _ bridge、SSRAM、SPI Controller、Communication UART、Timer、DMA、FIFO、PIO和System ID等模塊,通過Quartus II自帶的SOPC Builder工具構成片上系統。Nios II CPU可以靈活地進行任務調度,配合Nios II IDE軟件編程環境,可以方便的對A/D采集芯片進行SPI總線配置。電子艙信號經過隔離放大等預處理后,在Nios CPU的控制下送入A/D轉換電路模塊完成采集工作,將經過處理的數據緩存到FIFO,DMA完成數據從FIFO到SDRAM的搬移工作。Nios II內核配置和CPU板工作原理框圖分別如圖2、圖3所示。

圖2 Nios II內核配置

圖3 CPU板工作原理框圖

3.1.2 SPI總線控制器模塊

SPI是SOPC Builder內部集成的嵌入式系統常用的工業標準串行協議,它可直接與各個廠家生產的多種標準外圍器件直接接口。該接口一般使用4根線:串行時鐘線(SCK)、主機輸入/從機輸出數據線MISO、主機輸出/從機輸入數據線MOSI和低電平有效的從機選擇線SS(有的SPI接口芯片帶有中斷信號線INT,有的SPI接口芯片沒有主機輸出/從機輸入數據線MOSI[6-8])。

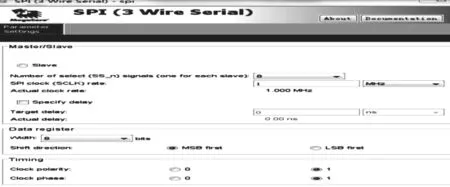

系統中使用SOPC Builder配置向導來指定SPI內核特性,SPI的配置如圖4所示。

(1)主/從配置(Master/Slave)

系統中SPI內核控制A/D轉換器完成數據采集,因此選項選擇主控制器模式。在此模式下,可選擇通用選擇信號(Generate Select Signals)、SPI時鐘頻率(SPI clock rate)和指定延時(Specify Delay)。

圖4 SPI配置選項

(2)通用選擇信號

該選項設置從設備的數目,取值范圍為1-132。SP主控制器內核為每個從控制器提供唯一的SS_n信號。本系統中,SPI核控制8路AD輸入,因此選項選擇8。

(3)SPI時鐘頻率

該選項設置主控制器和從控制器之間的SCLK頻率。SPI主控制內核通過Avalon_MM分頻產生SCLK。SCLK的實際頻率不可能精確地匹配所需的目標時鐘頻率,實際獲得的頻率值小于指定的目標值[9]。

由于A/D轉換器ICL7135支持的最高時鐘頻率為1MHz,本系統選用的時鐘頻率為1MHz。

3.2信號預處理模塊

由于系統采集對象是30路相關模擬信號,本設計采用多路模擬開關AD7502陣列作為預處理信號電路。AD7502是一種雙4通道多路開關芯片,依據兩個二進制地址線(A0,A1)和選通端(EN)的狀態來選擇8路輸入的兩路,分別與兩個輸出端相接通。本系統中30路信號共需要四片AD7502,在譯碼控制邏輯的控制下,這四片AD7502將同時選通8路相關信號。為了能夠并行采集到相關信號,在分配AD7502的引腳時,需要將這些相關信號分配在能夠同時被選通轉換的輸入通道上。

3.3A/D采集模塊

A/D采集模塊是數據采集系統的重要組成部分。由于系統的采集對象是30路相關模擬信號,為了滿足系統的高精度和高速要求,選用美國INTERSIL公司生產的4位雙積分A/D轉換器ICL7135。該芯片具有精度高(相當于14位A/D轉換器)、成本低、自動校零、自動極性輸出、自動量程控制信號輸出等特點,其最高轉換速率可達25次/秒。

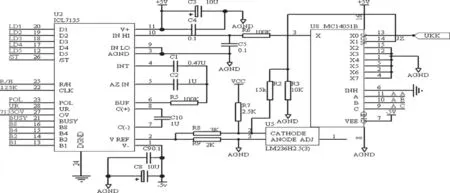

要采集的模擬量先經過多路模擬選擇開關MC4051芯片,由Nios II CPU通過SPI核控制8片ICL7135芯片完成數模轉換,并通過UART核與上位機通信,將數據傳回上位機。當“積分2秒”按鍵按下,待檢測的信號形成后,就發SB_TB信號來啟動A/D開始轉換。Nios CPU采用中斷方式讀取結果。A/D轉換結束后,由BUSY、STROBE和高位D5信號組成中斷信號,由CPU響應中斷來讀走轉換結果。模數轉換器ICL7135及其外圍電路如圖5所示。

圖5 模數轉換器ICL7135及其外圍電路

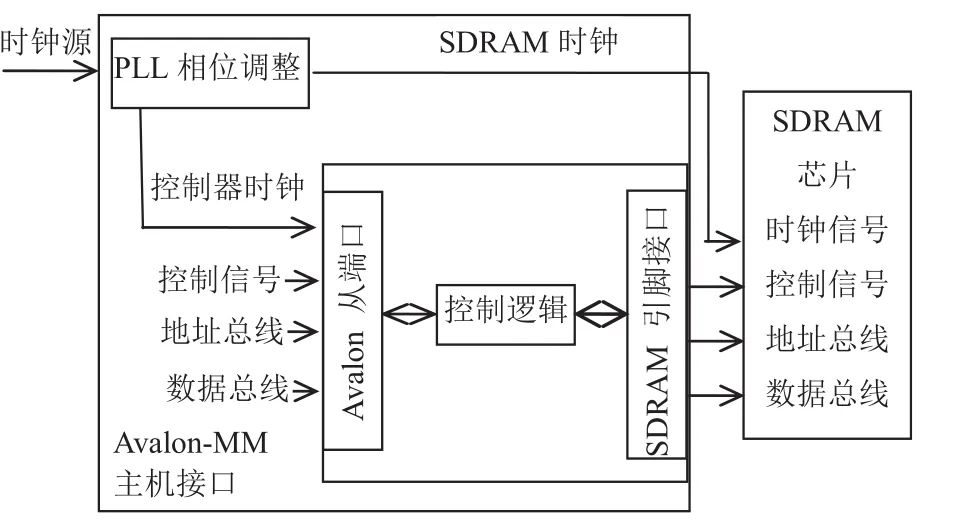

3.4SDRAM模塊

由于EP2C35芯片的內存容量不能滿足控制系統程序容量,因此需要外擴SDRAM作為運行存儲器。根據SDRAM一般用于大容量易失存儲器且成本較低的應用中的特點,因此將采集到的數據存儲在一片SDRAM存儲器中。Avalon總線接口的SDRAM控制器結構框圖如圖6所示。FPGA片內的SDRAM控制器IP核與外部SDRAM存儲器芯片之間的硬件接口,包括了時鐘接口(clk)、時鐘屏蔽接口(cke)、地址總線(addr)、塊選信號(ba)、片選信號(cs)、行選信號(ras)、列選信號(cas)、寫選通信號(we)、數據總線(dq)和數據字節屏蔽信號(dqm)。SDRAM控制器的IP核可通過不同的數據寬度來訪問SDRAM[9-10]。本系統中采用32位數據。

圖6 SDRAM控制器結構圖

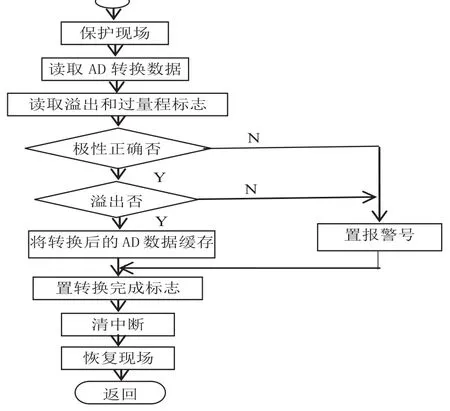

4 軟件設計

系統軟件設計是利用Altera公司的軟件集成開發工具Nios II IDE來完成,用C語言進行編程[11-12]。軟件設計主要包括嵌入式操作系統的移植、目標板底層驅動設計、A/D采集程序代碼編寫等部分,這里主要介紹關鍵的A/D采集程序。A/D采樣子程序流程圖如圖7所示。

圖7 A/D采樣子程序流程圖

5 結束語

系統采用Nios II處理器集成SOPC系統,有效解決了電子艙信號群數據的采集和存儲問題,較好地完成了電子艙信號群的高速采集工作。

設計采用了通用大規模集成電路和嵌入式技術,簡化了硬件電路、減小了設備體積、降低了成本,智能化程度更高。方案的硬件系統已通過了PCB加工及功能調試驗證。該方案穩定可行,程序操作性強,在數據采集以及其它方面具有一定的參考價值。

參考文獻:

[1]李薇,危建國.基于PCI總線的電子艙信號群高速采集系統[J].計測技術,2006,26(3):24-26.Li Wei,Wei Jianguo.The Electronic Cabin Signal Group High Speed Acquisition System Based on PCI Bus[J].Measurement technology,2006,26(3):24-26.

[2]劉政,劉富強.基于PCI總線的數據采集[J].中國科技信息,2005(11):12.Liu Zheng,Liu Fuqiang.Data Acquisition Based on PCI Bus[J].CHINA SCIENCE AND TECHNOLOGY INFORMATION,2005(11):12.

[3]劉書文,駱英.基于Nios II的超聲相控陣數據采集系統[J].儀表技術與傳感器,2014(6):72-75.LIU Shu-Wen,LUO Ying,WANG Zi-Ping.Data Acquisition System for Ultrasonic Phased Array System Based on Embedded NiosII[J].Instrument Technique and Sensor,2014(6):72-75.

[4]秦文姬,黃國兵.基于Nios II的蓄電池組在線監測系統的設計[J].微處理機,2011(6):73-76.QIN Wen-ji,HUANG Guo-bing.Design of Battery Online Monitor Unit Based on Nios II[J].MICROPROCESSORS,2011(6):73-76.

[5]趙宏陽,丁曉明.基于FPGA的高速多路視頻數據采集系統[J].單片機與嵌入式系統,2012(7):56-59.Zhao Hongyang,Ding Xiaoming.Acquisition System for High-speed Multi-channel Video Data Based on FPGA [J].Microcontrollers &Embedded Systems,2012(7):56-59.

[6]劉培洲,高天德,夏彥澤,等.基于Nios 1I的以太網數據采集平臺設計[J].計算機與數字工程,2014,42 (9):1733-1736.LIU Peizhou,GAO Tiande,XIA Yanze et al.Ethernet Data Collection Platform Design Based on NiosⅡ[J].Computer &Digital Engineering,2014,42(9):1733-1736.

[7]Alter Corporation.NiosII Hardware Development Tutoria [EB/OL].(2013-03-05)[2015-02-20]http://www.doc88.com/p-256253727166.html.

[8]李萍,凌力.基于Nios II的數據采集系統設計與實現[J].艦船電子工程,2012,32(1):74-76.Li Ping,Ling Li.Design and Implementation of Data Acquisition System Based on Nios II[J].Ship Electronic Engineering,2012,32(1):74-76.

[9]赫建國,倪德克,鄭燕.基于Nios II內核的FPGA電路設計[M].北京:電子工業出版社,2010.He Jianguo,Ni Deke,Zheng Yan.FPGA circuit design based on Nios II[M].Beijing:Publishing House of Electronics Industry,2010.

[10]陳偉軍,陶純匡.基于Nios II的CCD采集系統的設計[J].單片機與嵌入式系統應用,2012(8):58-61.Chen Weijun,Tao Chunkuang.Design of CCD Acquisition System Based on NiosII[J].Microcontrollers & Embedded Systems,2012(8):58-61.

[11]張燕,任安虎.基于SOPC數據采集與控制系統的設計[J].電子設計工程,2012,20(12):184-185.ZHANG Yan,REN An-hu.Design of data acquisition and control system based on SOPC[J].Electronic Design Engineering,2012,20(12):184-185.

[12]蔡偉綱.Nios II軟件架構解析[M].西安:西安電子科技大學出版社,2007.Cai Weigang.Nios II software architecture Analysis [M].Xi’an:Xi'an University of Electronic Science and Technology Press,2007.

A High Speed Acquisition System Based on Nios II for the Electronic Cabin Signal Group

Qin Wenji,Li Li

(Institute of Computer,Xi’an Polytechnical University,Xi’an 710048,China)

Abstract:As a key part of the missile system,the electronic cabin can detect and track the target missile,and it is required to be debugged and tested before using.A high speed data acquisition system based on Nios II is designed and realized for the electronic cabin signal group in this paper.Using cyclone series EP2C35 chip and Nios II as core processor,the system can process the signals converted by A/D and complete the high speed data acquisition.Compared with the previous PCI bus program,this system has some advantages,such as simplifying the hardware circuit,reducing equipment size and costs,adapting to a variety of different products' logic level,coding stapling and satisfying needs of presetting parameters and functional expansion upgrade.And it improves the level of reliability and intelligent analysis of experimental data processing system.

Key words:Electronic cabin;Nios II soft core;SOPC;SPI core;A/D converter ICL7135;Data acquisition

DOI:10.3969/j.issn.1002-2279.2016.02.019

中圖分類號:TP368.1

文獻標識碼:A

文章編號:1002-2279(2016)02-0073-04

基金項目:?2014年陜西省大學生創新創業訓練計劃項目(1240)

作者簡介:秦文姬(1981-),女,山西省臨縣人,講師,碩士研究生,主研方向:計算機測控、嵌入式系統應用。

收稿日期:2015-04-28