熱成像傳感器動靜態成像系統設計

李金龍, 王喆垚

(清華大學 微電子研究所,北京 100084)

?

熱成像傳感器動靜態成像系統設計

李金龍, 王喆垚

(清華大學 微電子研究所,北京 100084)

摘要:為測試研究室開發的熱成像傳感器性能與成像質量,設計了成像傳感器動靜態成像與圖像算法驗證系統。系統能夠捕獲成像傳感器靜態圖像,并能實時成像,具有通用性。數據的采集和處理應用FPGA+DSP開發板實現。數據傳輸基于CY7C68013芯片以塊同步數據傳輸方式,實現了無縫同步方式高速傳輸。基于VS2010編程環境和開源機器視覺庫編寫了接收、存儲以及處理圖像數據應用程序平臺。測試表明:系統能夠以40 Mbyte/s速率數據傳輸,用于實驗室開發的熱成像傳感器工作良好。

關鍵詞:實時; 圖像采集; 同步傳輸; 成像系統

0引言

熱成像圖像與可見光成像圖像不同,分辨率低,器件噪聲大,相關性強,辨識度低。目前關于新開發成像傳感器驗證基本是靜態成像的獲取,有關實時成像質量和動態處理算法驗證應用不足,通用性差,成像質量驗證環節與板級成像系統開發環節脫離,且傳感器原始成像圖像需要做很多算法研究和處理才能真正成像。因此,為實時、快捷地對一種成像傳感器成像質量觀測和針對其成像進行算法研究,為板級成像系統研發做鋪墊,設計一種模塊化、通用型陣列成像及其算法驗證系統平臺非常有意義。

陣列傳感器成像系統設計,主要分三個方面:數據獲取與預處理、數據傳輸、圖像處理。主流數據獲取方案有嵌入式和非嵌入式兩種,前者主要是基于現場可編程門陣列(FPGA)建立以處理器為核心的可編程片上系統(SOPC)[1,2]。盡管系統搭建設計簡單,但要兼顧控制與處理,處理速率受限,而且芯片和外設資源有限,不適合實時成像與圖像算法的驗證。后者主要是基于數字信號處理器(DSP)或者FPGA+DSP分立架構的成像采集架構[3]。在數據傳輸方面,外設部件互連標準( PCI)總線[4]和通用串行總線(USB)[5]傳輸是論文中出現的兩種方式。相比前兩者,后者簡單方便、傳輸速率高及通用性好。數據處理通常在PC上實現,大致分為虛擬儀器實現和編程實現兩種[6]。相比虛擬儀器實現,編程設計實現后期處理數據靈活,針對性好。在整體系統組成和實現方面,有針對已有成像傳感器和設計用傳感器成像系統實現[7~9],通用性和配置性較差,平臺性設計不足。基于這樣的需要,本文設計了熱成像傳感器成像質量動態驗證和圖像算法研究的系統。

1硬件系統解決方案

硬件系統主要包括:陣列傳感器、DSP+FPGA開發板(以下簡稱“開發板”)、CY7C68013芯片以及PC,結構如圖1。

圖1 硬件系統框架Fig 1 Framework of hardware system

其中,長方形方框的部分是成像傳感器高速采集處理成像系統,用于成像傳感器圖像數據的獲取、成像分析和動靜態圖像處理算法驗證。FPGA作為圖像實時采集系統主體與DSP之間互聯足夠數量的IO口。FPGA負責與傳感器接口,負責與CY7C68013芯片、LCD接口與驅動,負責與DSP的通信。DSP能對FPGA外圍設備和IO口的使用。

FPGA配置有兩個大小均為8MB的數據存儲器SRAM和一個大小512 kB的程序存儲器EEPROM。DSP配置有一個4M的16位的程序存儲器FLASH和一個4M的32位的數據存儲器SDRAM。FPGA采用EP2C70F672C8,其門數資源非常豐富,其現場可配置性非常適合信號處理和控制。DSP采用德州儀器的高速浮點型處理器TMS320C6713B,主頻可選配為225/300 MHz,具有強大的并行數字信號處理能力。

開發板與電腦之間數據傳輸采用CY7C68013芯片,該芯片將USB2.0收發器,SIE(串行接口引擎),增強型8051微控制器以及GPIF(可編程外設接口)集成到一個芯片中,功耗低,功能全[5]。該芯片支持全速12 Mbps和高速480 Mbps傳輸,能夠滿足系統數據傳輸速率的要求。

實時圖像的接收和處理需要較高的運算速度和大的運算量,需要應用雙線程乃至多線程。PC上集成了豐富的軟硬件系統資源,適合多線程程序的開發,方便對圖像獲取和實時成像,便捷作為傳感器成像進行處理算法研究,適合作為成像傳感器成像質量驗證平臺。

2系統軟件設計與實現

開發板與傳感器接口采用硬件語言進行模塊化設計,具有現場可配置性,適用于不同成像傳感器成像開發。開發板與CY7C68013芯片之間控制依據芯片固件程序設計為同步Bulk塊傳輸接口。固件程序將芯片配置為設備與PC進行數據傳輸。固件程序、USB設備驅動程序和應用程序根據圖像分辨率大小進行參數化設計,可根據圖像傳感器尺寸大小和行數據多少進行參數調整。

2.1傳感器數據采集與USB傳輸接口

本文對實驗室開發分辨率為160×120雙通道熱成像傳感器和一種的CMOS傳感器(用于系統驗證)進行了傳感器接口與CY7C68013芯片接口程序模塊設計。兩者僅在對傳感器時序產生與控制模塊有區別,其它完全相同。熱成像傳感器芯片要實現和CMOS傳感器一樣的數據采集,并進一步實現成像,除了芯片中各部分電路按逐行讀出控制設計時序工作外,還要設計芯片讀出電路輸出一些時序信號,如像素同步時鐘信號、行同步信號、幀同步信號等。

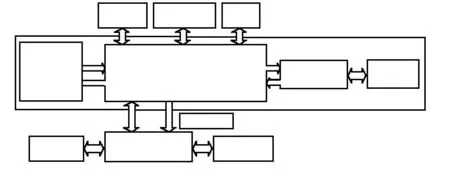

熱成像傳感器時序與控制模塊程序產生時序控制信號有時鐘clk、重置rst、行選時序WLPLUS(即行輸出有效信號)、行像素控制積分INTEG,ADC使能脈沖ADCEN,ADC數據轉移至鎖存器的脈沖CTRANS、列選時鐘BLPLUS、計數BLADD(該信號用于邏輯分析儀測試像素讀取同步性)以及其他一些讀出電路邏輯控制信號。熱成像傳感器讀出控制如下:每一行數據開始前,INTEG信號對行像素讀出單元積分放大器清零,然后對象元積分(INTEG高清零,低電平象元單元電流積分轉為模擬電壓)。積分放大器積分最后20個周期,ADCEN為高使能ADC進行D/A轉換。D/A轉換完畢,CTRANS為高電平5個時鐘周期將一行象元數據轉至鎖存器。數據轉移至鎖存器后,WLPLUS為高,120個BLPLUS周期對一整行像素數據逐一讀取。熱成像傳感器芯片會產生幀同步時鐘信號。依據芯片讀出電路工作原理,為保持同步性,將WLPLUS,PCLK(采集時鐘反相,時鐘上升沿芯片數據有效)分別作為采集控制信號作為行同步信號、像素采集同步信號輸出,與幀同步信號應用于數據采集。熱成像傳感器采集模塊產生的時序控制信號如圖2。

圖2 熱成像傳感器數據采集時序Fig 2 Data acquisition timing of thermal imaging sensor

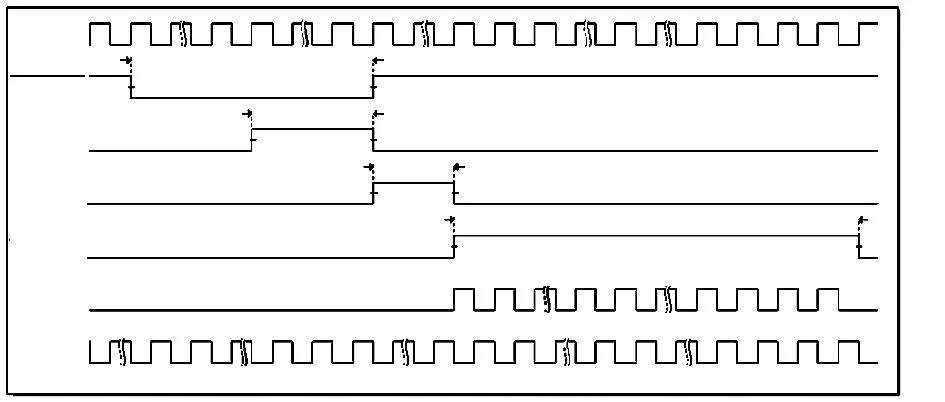

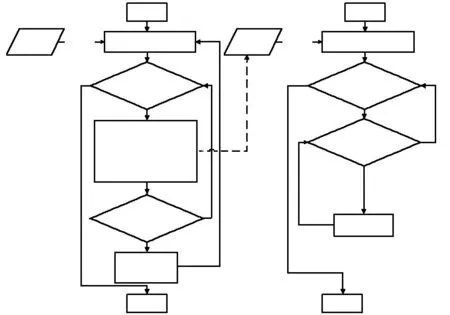

模塊硬件語言程序配置FPGA內部數據采集與傳輸結構如圖3。

圖3 FPGA內部數據采集與傳輸模塊結構Fig 3 Structure of data acquisition and transmissionmodules in FPGA

該模塊中,傳感陣列輸出的場信號、行信號、像素時鐘、CY7C68013芯片使能接收信號以及8位有效像素數據為模塊輸入信號,芯片使能寫與控制信號、同步數據輸出信號、場中斷信號、時序控制信號、同步時鐘信號為輸出信號。其中場信號用于通知一幀數據開始和作為上傳數據信號觸發CY7C68013芯片中斷,行信號和觸發信號用于向USB寫數據使能,傳感器像素輸出時鐘為CY7C68013芯片同步時鐘信號,處理模塊輸出數據接CY7C68013芯片低8位數據線。由于固件程序將CY7C68013芯片控制引腳配置為高電平有效,其它接口設置為低電平信號。

2.2固件程序與驅動程序

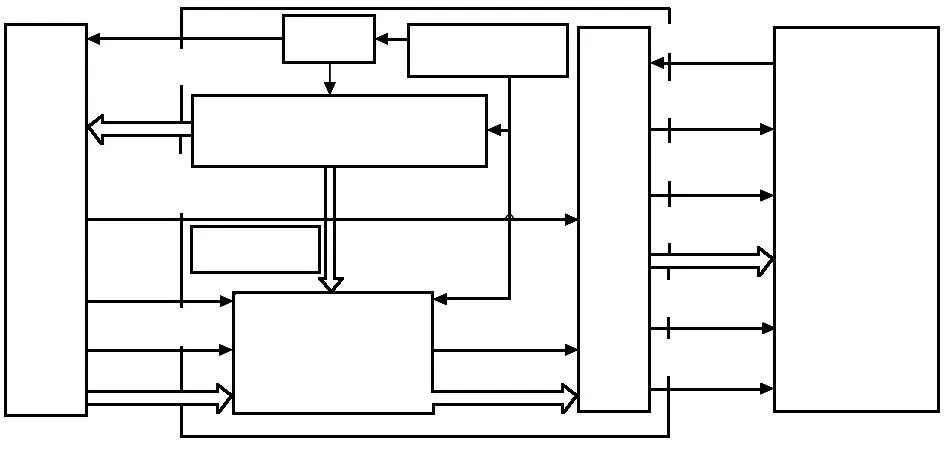

芯片公司為CY7C68013芯片提供固件編程框架,用戶只需在程序框架下根據實現目標設計自己的固件程序,該程序框架是一個自循環主程序框架和調用子程序。子程序有4個用戶函數和一個中斷處理函數:TD_Poll(),芯片配置函數TD_Init(),掛起函數 TD_Suspend(),喚醒函數TD_Resume()以及ISR_EXTR0()。固件程序流程如圖4。

圖4 固件程序框架流程Fig 4 Framework flow chart of firmware program

根據成像傳感器數據非連續、數據量大、要求速率高的特點,編寫固件程序時有針對性地對芯片初始化函數,并設計中斷處理函數。芯片配置函數,將CY7C68013芯片配置為8位Bulk同步設備模式高速傳輸。中斷函數收到場信號變化觸發響應中斷,設置數據接收允許。該設計能夠使固件程序實現辨別圖像開始和幀頻控制傳輸。修改中斷函數可以得到不同幀頻的圖像數據接收。驅動程序是固件程序和用戶應用程序之間的橋梁。驅動程序是在提供框架的基礎上對相關參數和設備描述進行修改完成。

2.3上位機應用程序

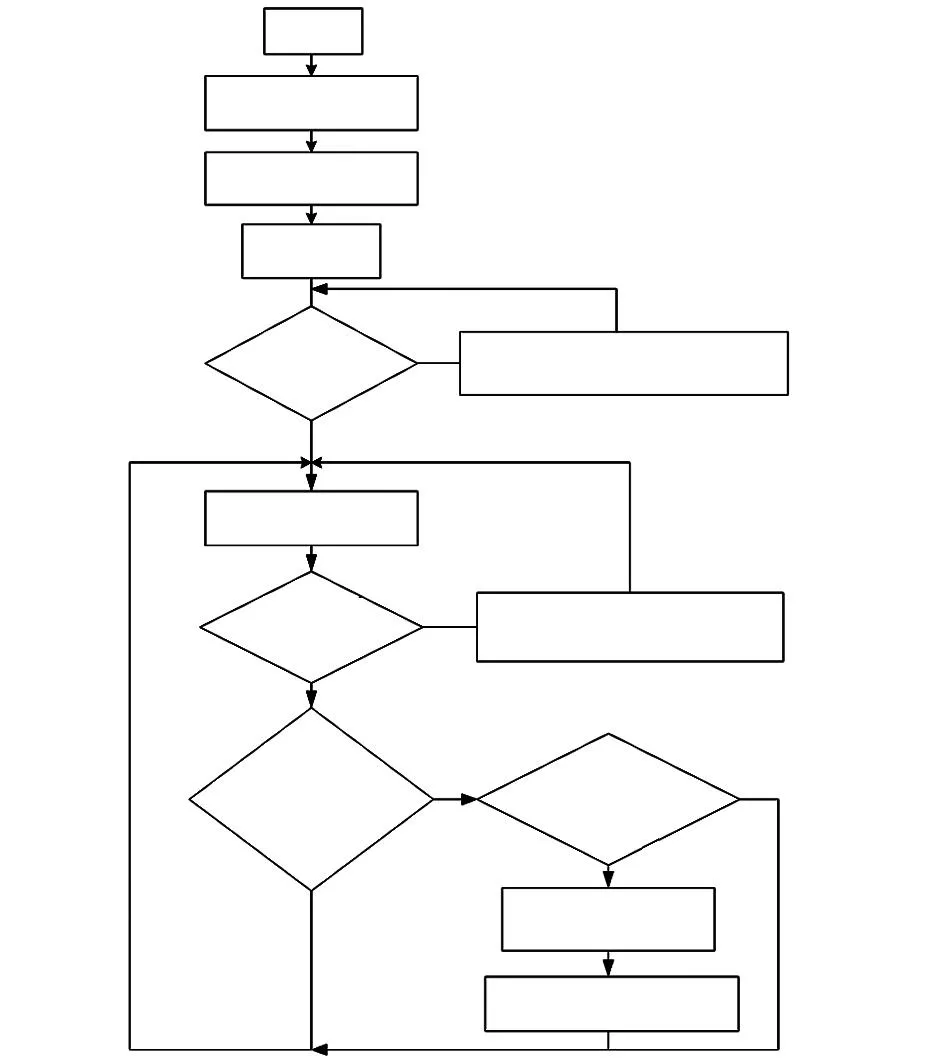

上位機程序設計是在添加并配置開源機器視覺庫的VS2010軟件開發環境上編寫的面向用戶的應用程序。為解決實時圖像采集和處理顯示,程序設計采用雙線程。首先MFC程序響應用戶開始消息啟動雙線程。圖像數據的接收基于提供的API(應用程序編程接口)庫,系統時間片輪到數據接收線程,程序異步接收USB設備上傳的數據。每接收一幀圖像存入申請的內存隊列,然后隊列指針+1,同時將接收的一幀圖像數據傳遞給處理顯示線程,設置顯示線程Flag為真,使能顯示。時間片輪到圖像處理和顯示線程時,顯示線程對圖像數據處理然后顯示在位圖控件上。兩個線程交替進行。應用程序響應終止消息,則程序釋放申請內存和其他資源,程序流程如圖5。

圖5 采集與處理程序流程圖Fig 5 Flow chart of collection and processing program

應用程序根據圖像傳感器分辨率大小設置異步等待時間和內存隊列每一塊內存大小,保證了應用程序采集與處理顯示準確穩定。應用程序將顯示在圖像顯示控件上的圖像以位圖形式保存。應用程序實現了圖像的高速實時接收和圖像處理顯示,支持熱成像傳感器靜態和動態圖像處理算法的研究。

3系統測試與結果

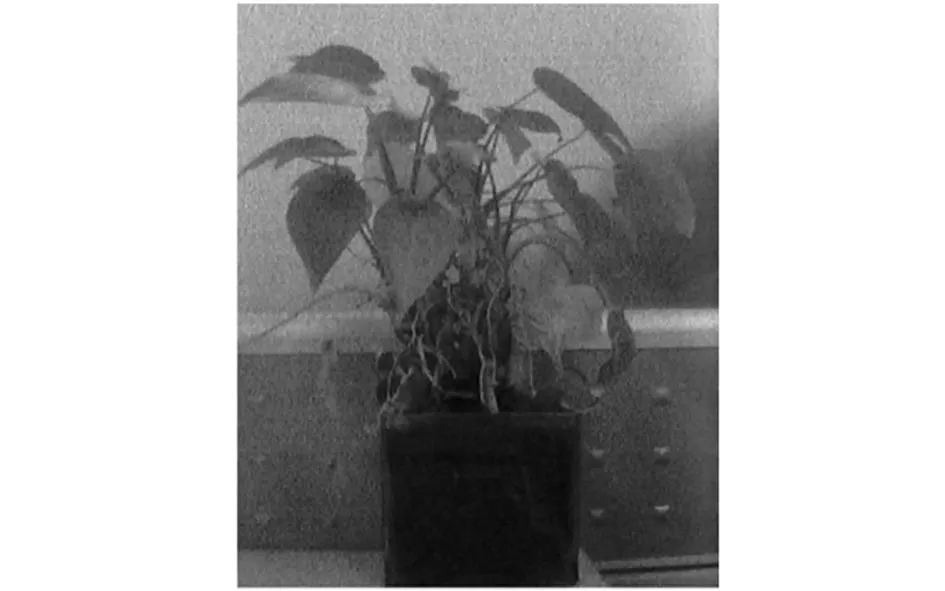

對系統進行測試,在FPGA模塊內產生40 MHz的同步時鐘、8位循環加法計數器輸出數據以及傳輸協議信號給CY7C68013芯片,上位機程序能夠實時接收并以40 Mbyte/s的速率保存數據。用帶有簡易鏡頭的CMOS傳感器對系統傳輸速率和穩定性進行測試。系統能夠以30 fps的速率穩定實現對圖像數據采集與處理顯示,CMOS傳感器獲得圖像如圖6。

圖6 系統捕獲CMOS傳感器圖像Fig 6 Image of CMOS sensor captured by system

系統應用于課題組開發的熱成像傳感器,獲取熱成像傳感器陣列原始圖像數據顯示如圖7。圖像大小為120×80(單通道),是對熱成像傳感器成像數據顯示。

圖7 系統獲取熱成像傳感器的圖像Fig 7 Image of thermal imaging sensor acquired by system

系統數據獲取、成像、芯片圖像數據獲取正常,為下一階段對熱成像傳感器安裝光學系統后的圖像失效元補償、非均勻矯正與增強算法研究與系統開發提供了系統平臺。

4結論

相比傳統對開發傳感器功能和性能的測試,本文設計的傳感器成像質量和圖像算法實時驗證系統方案有著實時觀測性、采集速率可調節性以及通用性的特點。該平臺實現了成像傳感器數據采集,靜態圖像捕獲和動態圖像實時顯示,并且支持對被測試傳感器原始圖像處理算法研究。系統方案設計簡潔高效,能夠作為新開發圖像傳感器成像特點和圖像算法研究系統平臺,在軟硬件設計方面為下一步圖像傳感器成像儀樣機設計工作做了一定鋪墊。

參考文獻:

[1]Lu Y Y,Wang J Z,Chang F W.Development of infrared real-time imaging system based on SOPC[C]∥The 2008 International Conference on Embedded Software and Systems,IEEE Computer Society,2008:63-68.

[2]Liu G,Li J,Ma H.Study of real-time infrared image enhancement algorithm based on FPGA[C]∥The 2009 International Confe-rence on Mechatronics and Automation,IEEE,2009:1882-1886.

[3]Wei H.Designing and development of multi-DSP real-time image processing system based on FPGA[C]∥The 2011 International Conference on Computer Science and Network Technology,IEEE,2011:1263-1265.

[4]Zhao Y,Liu J M,Zhang Q.Research of high speed sampling and processing of dynamic arc image[C]∥2008 International Confe-rence on Wavelet Analysis and Pattern Recognition,IEEE,2008:183-187.

[5]向文芳,邢濤,曹紅兵,等.高速數據采集系統的USB接口設計[J].計算機測量與控制,2011,19(10):2567-2570.

[6]Zhang N,Lü J,Zhou Y,et al.Research on infrared imaging system of UIRFPA based on virtual instrument[C]∥The 10th International Conference on Electronic Measurement & Instruments.IEEE,2011:117-120.

[7]Li H,Zhang S C,Han C,et al.A near infrared imaging detection system based on davinci Platform[C]∥The 9th International Conference on Electronic Measurement & Instruments,IEEE,2009:4—154-4—159.

[8]Oren Dayakc.A low-cost uncooled infrared detector array and its camera electronics[D].AnKara:Middle East Technical University of Turkey,2011.

[9]Wang J,Peng L,Wei L.Design and implementation of a real-time image processing system with modularization and extendibi-lity[C]∥2008 International Conference on Audio,Language and Image Processing,IEEE,2008:798-802.

Design of dynamic and static states imaging system for thermal imaging sensor

LI Jin-long, WANG Zhe-yao

(Institute of Microelectronics,Tsinghua University,Beijing 100084,China)

Abstract:In order to test performance and imaging quality of the developed thermal imaging sensor,dynamic and static states imaging and image algorithm testing system is designed.The system can capture static image of imaging sensor and real-time imaging,and it has versatility.The board of FPGA + DSP is responsible for data acquisition and processing.By bulk synchronous data transmission mode based on CY7C68013 chip,seamless synchronization high-speed transmission of data is realized.An application program platform is developed to receive,save and process image data based on VS2010 programming environment and open source machine vision library.Test result shows that the system can transmit data at the speed of 40 Mbyte/s and the thermal imaging sensor for lab works well.

Key words:real-time; image acquisition; synchronous transmission; imaging system

DOI:10.13873/J.1000—9787(2016)03—0092—04

收稿日期:2015—07—02

中圖分類號:TN 362

文獻標識碼:A

文章編號:1000—9787(2016)03—0092—04

作者簡介:

李金龍(1989-),男,河南杞縣人,碩士研究生,主要從事熱成像傳感器陣列成像系統與成像算法研究。