基于FPGA的HDB3編碼和解碼器的設計與實現

吳光輝,殷嚴剛,姜 愉

(1.廣西移動欽州分公司;2.廣西師范大學;3.欽州學院)

基于FPGA的HDB3編碼和解碼器的設計與實現

吳光輝1,殷嚴剛2,姜 愉3

(1.廣西移動欽州分公司;2.廣西師范大學;3.欽州學院)

本人通過對HDB3編解碼原理進行分析和研究,提出一種基于FPGA的HDB3編解碼方法,并通過硬件描述語言構建了其編譯碼模型,使用EDA 技術實現仿真,驗證了其設計的有效性,其功能符合HDB 3編譯碼的要求。

HDB3編解碼;FPGA;Verilog HDL;Quartus II

0 引言

HDB3 碼 (high density bipolar),即三階高密度雙極性碼,是AMI碼 (alternate mark inversion, 雙極性傳號交替反轉碼)的改進型。HDB3 碼可以由專用集成電路及相應匹配的外圍中小規模集成芯片來實現, 但集成程度不高,不易升級和維護,用FPGA 設計HDB3編解碼器,能將 HDB3 編解碼和通信系統中的其它電路(如復接和分接電路)集成在一個 FPGA芯片上,克服了分立硬件電路帶來的抗干擾差和不易調整等缺陷。

(3)為了使脈沖序列仍不含直流分量,則必須使相鄰的破壞點 V脈沖極性交替。

(4)為了保證前面兩條件成立,必須使相鄰的破壞點之間有奇數個“ 1” 碼。 如果原序列中破壞點之間的“ 1” 碼為偶數,則必須補為奇數,即將破壞節中的第一個“ 0” 碼變為“ 1” ,用 B脈沖表示。 這時破壞節變為“ B00V” 形式。 B脈沖極性與前一“ 1” 脈沖極性相反,而 B脈沖極性和 V脈沖極性相同。

1.2 HDB3碼譯碼

1 HDB3碼編譯碼原理

1.1 HDB3碼編碼

HDB3 碼是一種 AMI 碼的改進型,它的編碼原理可簡述為,在消息的二進制代碼序列中:

(1)當連“ 0” 碼的個數不大于 3 時,HDB3 編碼規律與AMI 碼相同,即“ 1” 碼變為“ +1”、“ - 1” 交替脈沖。

(2)當代碼序列中出現4個連“ 0” 碼或超過4個連“ 0”碼時,把連“ 0” 段按 4 個“ 0” 分節,即“0000” ,并使第 4 個“ 0”碼變為“ 1”碼,用 V脈沖表示。這樣可以消除長連“ 0” 現象。為了便于識別V脈沖,使 V脈沖極性與前一個“ 1” 脈沖極性相同。這樣就破壞了 AMI 碼極性交替的規律,所以 V 脈沖為破壞脈沖,把 V 脈沖和前 3 個連“ 0” 稱為破壞節“ 000V” 。

雖然 HDB3 碼的編碼規則比較復雜,但譯碼卻比較簡單。從上述原理看出: 每一個破壞符號 V總是與前一非 0 符號同極性(包括 B在內)。 這就是說,從收到的符號序列中可以容易地找到破壞點 V, 于是也斷定 V符號及其前面的 3 個符號必是連0 符號,從而恢復 4 個連 0 碼,再將所有- 1 變成+1 后便得到原消息代碼。

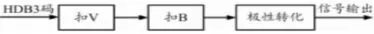

2 HDB3碼編碼模塊設計

其編碼過程 :首先插入V碼 ,然后插入B碼,最后是單雙極性變換。如果按照編碼規則的順序設計,應該首先進行單雙極性變換在完成插 V 和插 B 后,還需根據編碼規則變換當前 B 碼之后的非零碼的極性,這需要大量的寄存器來保存當前數據的狀態.導致電路非常復雜占用大量的FPGA內部邏輯單元 實現難度大 且成本高.

圖1 HDB3碼編碼模塊設計框圖

2.1 插V過程

V碼產生單元的功能實際上就是對消息代碼里的四連0串的檢測,當出現四個連0串的時候,把第四個0碼變換成V碼,而在其他情況下,則保持消息代碼的原樣輸出。為了為以后的編碼過程提供方便,將原信號中的一位碼元用2位二進制傳輸碼表示,在進行加V碼時,同一用“11”標識之,原l碼用“01”標識,0碼用“00”標識。輸入的代碼經插V操作后全部轉換成了雙相碼。

2.2 插B過程

B碼產生單元的功能是保證附加V碼后的序列不破壞“極性交替反轉”形成的無直流特性,當相鄰兩個V碼之間有偶數個非0碼時,則把后一個V碼之前的第1個非0碼后面的0碼變換成B碼。

2.3 單雙極性變換

根據HDB3的編碼規則,我們可以知道,V碼的極性是正負交替的,余下的1碼和B碼看成為一體且是正負交替的,同時滿足V碼的極性與前面的非零碼極性一致。由此我們可以將其分別進行極性變換來實現。

3 HDB3碼譯碼模塊設計

每一個破壞符號V 總是與前一非0 符號同極性,從收到的符號序列中可以容易地找到破壞點V,于是也斷定V 符號及其前面的3 個符號必是連0 符號,從而恢復4 個連0 碼,再將所有-1,+1 變成1后便得到原消息代碼。根據以上解碼原理HDB3 的解碼步驟可分為三步:(1) 扣 V;(2) 扣 B; (3)極性轉換HDB3解碼模塊的設計框圖如圖2

圖2 HDB3碼解碼模塊設計框圖

3.1 扣V過程

即檢測信號中的 10001 或-1000-1 串,如果檢測到 則把10001 或-1000-1 變為 10000 或-10000。具體操作是:我們定義一個10位寄存器 dffa [9:0] 用它來檢測信號中的 “10001”或“-1000-1” 一旦檢測到將他們的值分別變為“10000”或“-10000”

3.2 扣B碼過程

即檢測信號中的 1001 或-100-1 串,若檢測到則把 1001或-100-1 變為 0000,

具體操作是:我們定義一個8位寄存器 dffb[7:0] 用這個寄存器來檢測 “1001“或 “-100-1”一旦檢測到 將他們的值都變為“0000”

3.3 極性轉換

由于前面來的信號中有 01 和11 即 +1 和 -1 而實際情況是數字電路中只有0 和 1 所以要進行極性轉換把雙極性信號變為單極性信號使信號中只含有 0 和 1。算法為:如果輸入的是00,則輸出0。否則輸出1。

圖3 編碼模塊波形仿真圖

圖4 解碼模塊波形仿真圖

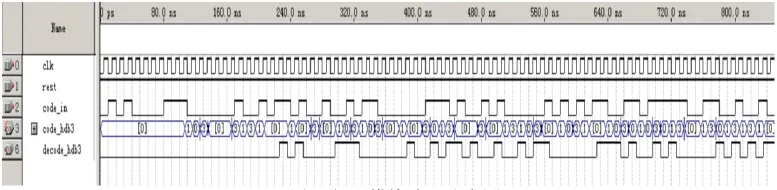

4 仿真分析

利用ALTERA 公司的Quartus II 開發軟件實現具體設計,其主要步驟如下: 在QII中建立工程,及Verilog HDL.v源文件,輸入代碼后進行編譯。然后再建立波形仿真文件對實驗結果進行仿真。仿真正確后可進行引腳綁定,同過下載器燒寫到FPGA芯片中觀察實驗效果。

4.1 編碼模塊仿真分析

對HDB3編碼模塊進行仿真驗證,圖3是仿真波形圖。輸入的二進制代碼為 1010110000011000010101000010000000 000000 ,Code_in是二進制代碼信息輸入。下面進行輸出的分析。

out_v是插v之后的輸出。out_b是插入b之后的輸出。Code_hdb3碼是經過極性變換后的HDB3碼輸出,從圖中可以看出:“01”為正電平,“11”為負電平,“00”為0電平,從波形可看出1和b碼實現了正負電平交替,而v碼與前面的最近的非零碼極性相同。符合HDB3編碼規則。

4.2 解碼模塊仿真分析

圖4中code_in是一串偽隨機序列二進制碼,在經過編碼模塊編碼后輸出,code_hdb3即為HDB3碼輸出,然后再經過解碼模塊得到解碼輸出,decode_hdb3即為解碼后的輸出。從圖中可以看出,輸出波形與輸入波形完全相同。

5 結論

本文所設計的HDB3 編解碼模塊簡單實用,利用FPGA 實現HDB3 編解碼功能具有很強的靈活性 可以集成到不同的通信系統中 提高系統設計的速度。本文提供了一種利用現代EDA技術,以ACEX系列FPGA芯片EPlK30為硬件平臺,以Quartus II為軟件平臺,以Verilog HDL,為開發工具,適合于FPGA實現的HDB3編譯碼器的設計方案。并從整個從NRZ 碼到HDB3碼的編碼過程以及解碼過程作了一個詳細的分析。且實驗結果符合預期, 有很好的應用遠景。

[1] 韓德紅,孫筱萌,張顯才. 基于FPGA的HDB3編解碼器的設計與實現. 空 軍雷達學院學報.2010.8第24卷第4期

[2] 吳海濤,陳英俊, 梁迎春. 基于FPGA的HDB3編解碼器設計.微計算機信息, 2008 , 24( 6 2) : 236 – 238

[3] 段吉海 黃智偉.基于 CPLD/FPGA 的數字通信系統建模與設計[M].北京 電子工業出版社 2004

[4] 朱勤為,唐 寧,趙明劍. 利用FPGA 實現HDB3編解碼功能.電子設計工程2009 年 12 月

[5] 基于EDA技術的HDB3編碼器的設計與實現 中國百科網

The Design and Realization of HDB3 encoder and decoder based on FPGA

Wu Guanghui1,Yin Yangang2,Jiang Yu3

(1.Guangxi mobile Qinzhou branch;2.Guangxi Normal University;3.Qinzhou University)

I analysis and study of the principles of HDB3 code,propose a method of HDB3 codec based on FPGA.And Through hardware description language to build the model of codec.Using EDA technology to realize the simulation,I Verify the effectiveness of the design. Its features correspond HDB3 codec requirements

HDB3 code;FPGA;Verilog HDL;Quartus II