基于FPGA的振動監測系統設計與實現

韓 旗,蔡 萍

(1.海軍駐上海七〇四所軍事代表室,上海 200031;2.上海交通大學,上海 200240)

基于FPGA的振動監測系統設計與實現

韓 旗1,蔡 萍2

(1.海軍駐上海七〇四所軍事代表室,上海 200031;2.上海交通大學,上海 200240)

針對長時間持續監控設備或結構振動的需求,基于FPGA技術構建了一個多通道振動監測系統,論文詳細介紹了監測系統的硬件構成,FPGA的固件設計及基于USB接口的數據傳輸的實現。系統已在實際工況下運行,可靠性良好,并具有良好的可擴展性。

振動監測;FPGA;flash存儲;USB傳輸

0 引言

振動和噪聲對儀器設備和人體生理或心理產生的影響愈來愈受到重視。船舶航行時產生的噪聲和振動會給船上設備儀器的正常運行和乘員的舒適性帶來影響;大型工業設備的振動噪聲不僅影響操作工人的聽力,嚴重時甚至導致心血管系統和消化系統的疾病;鐵/輕軌/高架公路等設施的振動則會嚴重影響周圍居民的日常生活。

為了對結構進行減振設計或進行客觀定量的環境振動噪聲評估,需要對振動進行長期的數據采集。對于長期監測、無人值守且電磁環境惡劣的使用環境,需要設計一種具有高可靠性的振動監測系統進行數據采集和數據保存。普遍采用的單片機或其它基于程序運行機制工作的控制器抗電磁干擾較差、長期穩定性不能保證。為此,本文提出了一種基于FPGA的三軸振動監測系統方案,并進行了實現。

1 系統構成

環境振動測量通常需要實現多點或多軸的振動數據采集[1],要求系統能夠在無人監守的情況下長期穩定工作。長時間監測要求系統具有較大的數據存儲容量,并提供時間指針。FPGA通過硬件實現所需功能,具有各模塊獨立運行、并行處理數據、方便擴展、無中斷等待,以及進程互相干擾等特性,非常適合于電磁環境惡劣、需要長期穩定運行的場合。

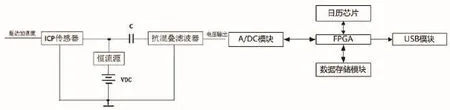

本設計兼顧成本和速度,選用了Altera公司的EP3C16芯片作為控制器。作為cyclone系列的中端產品,EP3C16的運行速度最高可達50M/s,片內RAM 516Kbits,邏輯單元15K,滿足多路振動數據采集系統數據緩存和對模數轉換芯片、時鐘芯片和數據存儲芯片等的操作要求,系統構成如圖1所示。

圖1 通用振動監測系統構成

ICP(Integrated Circuit Piezoelectric)傳感器為內置集成電路的壓電式振動加速度傳感器。內置的集成電路將原來的高阻抗輸出轉換為低阻抗輸出,從而大大提高了系統的抗干擾能力。ICP傳感器由恒流源供電,其輸出電壓的交流分量與振動加速度成正比,通過隔直電容C輸出到抗混疊濾波器。抗混疊濾波器用于濾除高于 1/2采樣頻率的頻譜成分,以避免采樣信號混疊[2]。通過FPGA控制對振動信號進行多通道高速采樣,并讀取時間信息,保存于NAND flash芯片中。定期將保存的數據通過USB協議進行數據轉存。

A/DC芯片AD7656具有高達250K/s的采樣率,16bit分辨力,能夠同時對6路輸入信號進行采樣;數據存儲模塊H27UBG8T2BTR具有復用的8位數據總線和地址總線,存儲容量4GB,FPGA通過I2C與日歷芯片 PCF8563接口,獲得時間指針。通過USB接口芯片CY7C68013A將數據傳輸到上位機進行數據分析。

2 固件設計

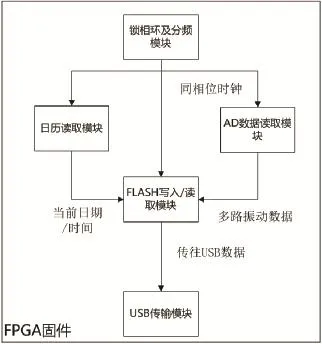

FPGA內部的程序以VHDL語言進行編寫,通過模塊化設計,使各項任務并行、獨立運行。固件設計各模塊如圖2所示。

系統使用50M的外部時鐘,通過FPGA內部鎖相環電路保證時鐘信號相位一致,通過分頻獲得各個模塊需要的時鐘頻率;日歷讀取模塊通過普通IO口模擬100KHz的I2C協議,實現對日期的讀取;A/DC數據讀取模塊在振動數據采集時驅動AD7656芯片采樣于10KHz下工作,而在休眠及數據傳輸模式時自動休眠,等待時鐘喚醒。flash寫入/讀取模塊根據工作模式的設定[4],分別啟動對應模塊,獲得數據后存儲入flash或者讀取flash數據后傳輸到USB傳輸模塊。以下按照模塊分別進行介紹。

1)日歷讀取模塊

PCF8563在 I2C總線上的器件寫入從地址為0xA2 H,讀取從地址為0xA3 H,其02h至08h子寄存器分別存儲從秒到年7段BCD碼時間信息,在系統掉電情況下通過電池供電,正常上電時則由電源供電以保證時間信息的完整。

圖2 FPGA固件模塊

該模塊以正常IO口模擬I2c接口,由定時器觸發后從子寄存器中依序讀回秒/分鐘/小時/日/月/年信息,傳遞到存儲模塊中,用于標識此次數據測量開始的時間。

2)A/DC數據讀取模塊

系統使用的AD7656由管腳Convert上升沿觸發采樣,經過轉換時間Tconv后芯片busy管腳由高電平拉低,而后讀取模塊選中AD芯片片選信號,對讀取管腳(rd)輸入下降沿時AD芯片的數據輸出口逐通道輸出采樣通道1~6的信號。該模塊的仿真時序輸出如圖3所示。

圖3 AD數據讀取模塊輸出仿真

3)flash寫入/讀取模塊

flash模塊到FPGA的IO口定義及其到flash芯片的連接如圖4所示。

flash芯片 H27UBG8T2BTR 通過管腳addr/data[7..0]復用 8位的地址總線/命令總線/數據總線,因此在讀寫過程中均需要較為嚴格的時序要求。在管腳的上升沿,根據ALE/CLE這兩個管腳的高電平,8位總線上的數據寫入flash芯片的地址寄存器/命令寄存器;在寫入寄存器過程中管腳表明芯片當前是否處于可操作狀態,在操作時需要檢查其為低電平時方可進行下一步操作,避免命令字同地址/數據的混淆,這將導致后續數據出現大面積的失效。在尋址過程中,共需要5個數據周期來完成地址的輸入。

在系統設計中,單次采集三路16位數據,合計48位,而日歷數據經過處理后長度也為48位,為了數據地址的連續性,使用每個page中的前8190個字節,共計存儲1365組數據(或日歷),而芯片能夠存儲1365*256*2048組數據。

H27UBG8T2BTR芯片在上電過程中默認被設置為讀取頁面模式,以避免在上電時電壓的波動造成不可預計的擦除和寫入操作;因此在擦除和寫入模式下,需要發送FF h重置命令字以重置運行模式。

讀寫H27UBG8T2BTR的流程通過VHDL的狀態機實現,該有限狀態機的輸出基于當前狀態及當前輸入情況確定。對FLASH芯片的操作有三種工作模式,在上電初始化時讀取IO口信息確定,分別如下所示:

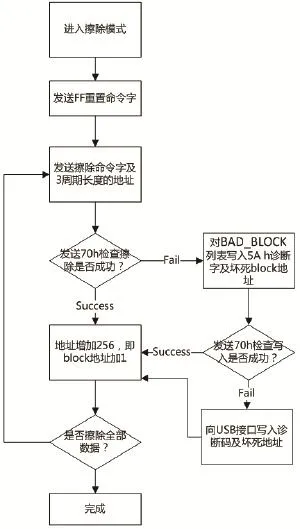

1)擦除flash:flash擦除頁面原有數據后,使頁面內所有數據位均為‘1’后方能進行寫入,且一次寫入后必須擦除后方能重寫。擦除flash的狀態機如圖5所示,從block 0開始擦除,由于芯片存在壞死的存儲塊,這些存儲塊在擦除過程中無法被全部重置為‘1’狀態,需要對壞死存儲塊進行檢查并記錄。芯片由硬件保證第一個存儲塊必定是完好的,故而在存儲塊0上建立壞死存儲塊列表。在擦除過程中設計了USB診斷功能,可以通過系統設計的USB接口獲得芯片中的壞死存儲塊地址。

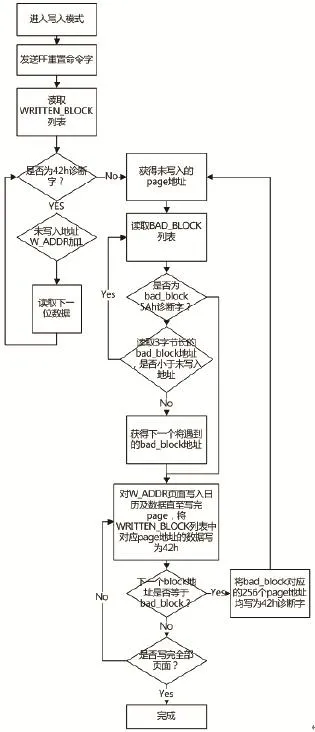

2)將日期信息和A/DC數據寫入flash;寫入flash狀態機如圖6所示,在上電后需要讀取壞死存儲塊列表,避免在壞死存儲塊上寫入引起的數據丟失問題,同時為避免重復寫入已使用的存儲塊,在存儲塊0上建立已寫存儲塊列表,存儲寫過的頁面地址及存儲塊地址。在上電過程中,讀取已寫存儲塊列表直至數據為未寫入狀態,即可獲知未使用頁面地址。當寫入地址達到壞死存儲塊時,將該存儲塊內的256個頁面地址標記為已寫存儲塊列表中,而后讀取下一個壞死存儲塊地址,繼續數據記錄。

3)讀取數據,并傳輸到USB傳輸模塊讀取數據及傳輸狀態機,則讀取已寫存儲塊及壞死存儲塊列表,將有效頁面內數據全部傳輸到USB模塊的緩沖區內,經USB傳輸到電腦。

圖5 擦除FLASH狀態機圖

圖6 寫入狀態機

圖7 USB模塊仿真輸出

4)USB傳輸模塊

用于實現USB傳輸的CYTC68013芯片是一個帶增強型MCS51內核和USB接口的單片機,完全遵從USB2.0協議,可提供高達480Mbps的傳輸率;內部集成鎖相環,最高可使51內核工作在48MHz;對外提供兩個串口,可以方便地與外部通信;片內擁有8KB的RAM,可完全滿足系統每次傳輸數據的需要。本系統中,CY7C68013A芯片工作于異步時鐘SLAVE FIFO模式[5],該芯片內部使用內嵌的FX2微處理器來實現USB協議層的配置,FPGA通過8位數據線與芯片內部的FIFO連接。本系統中,令芯片內部的4KB FIFO全部用于上傳振動數據。USB傳輸模塊仿真輸出如圖7所示,檢查CY7C68013A片上FIFO未滿的標志管腳后將需傳輸的數據傳遞到數據總線上,以上升沿觸發SLWR管腳將數據寫入FIFO,而后由FX2處理器將數據傳輸至上位機。

3 結束語

本研究實現的基于FPGA的三軸振動監測系統能夠對六路信號以 10Ksamples/second進行同步采樣,在偶發的掉電情況下能夠正常恢復工作,繼續記錄振動信號。作為存儲媒介的NAND FLASH能夠保證數據有效性,采集完成后通過USB 2.0接口將數據傳輸到上位機,進行后續分析。使用結果表明本系統具有在電磁干擾環境下長期穩定工作的能力,適用于對各種結構和設備的振動進行長期監測的場合。

[1]閻潔.基于DSP和CPLD的船舶振動監測系統的研究[D].天津大學,2005.

[2]宗赤.基于加速度傳感器的船舶振動檢測系統設計[J].電子產品世界,2011(4):46-47.

[3]李海鴻,朱元清,陳蓓.實時時鐘芯片 PCF8563及其應用[J].國外電子測量技術,2002(5):29-31.

[4]李慶誠,孫明達.基于NAND型閃存的嵌入式文件系統設計[J].計算機應用研究,2006(4):231-233+239.

[5]扈嘯,張玘,張連超.USB2.0控制器CY7C68013特點與應用[J].單片機與嵌入式系統應用,2002(10):48-50+54.

Design and Realization of Vibration Monitoring System Based on FPGA

Han Qi1,Cai Ping2

(1.Navy Representation Office at No.704 Research Institute,Shanghai 200031,China; 2.Shanghai Jiao Tong University,Shanghai 200240,China)

In order to monitor the environment vibration in a long period of time,a vibration monitoring system with multi-channel based on FPGA technology is developed.The hardware implement is introduced in detail.The firmware design and the data transmission via USB are realized.The monitoring system has already been in use in the real field and has satisfied reliability as well as good expansibility.

vibration monitoring; FPGA; flash storing; USB transmitting

U665.13

A DOIⅹ10.14141/j.31-1981.2015.06.011

韓旗(1970-)男,碩士,高級工程師,研究方向:船舶機電設備。