基于FPGA和CY7C68013A的數據采集系統

陶庭興

摘 要:為了解決計算機和基于FPGA的數據采集系統的數據傳輸速率的問題,本文設計一種基于CY7C68013A芯片的USB2.0接口方案,設計采用FPGA為主控芯片,實現對USB芯片的控制。介紹了該系統的硬件設計以及軟件工作流程。實驗表明:FPGA通過USB接口實現了高速可靠的數據傳輸。

關鍵詞:FPGA;USB2.0;CY7C68013A;數據傳輸

由于USB接口的高速、即插即用,易于擴展等特點其得到廣泛應用。USB2.0高速模式下,數據傳輸速率可達480Mbps[1-2],是目前電腦中的標準擴展接口。本系統設計的目的在于基于FPGA控制多路數據采集系統和計算機之間提供一個高速通信接口。

1 系統硬件設計

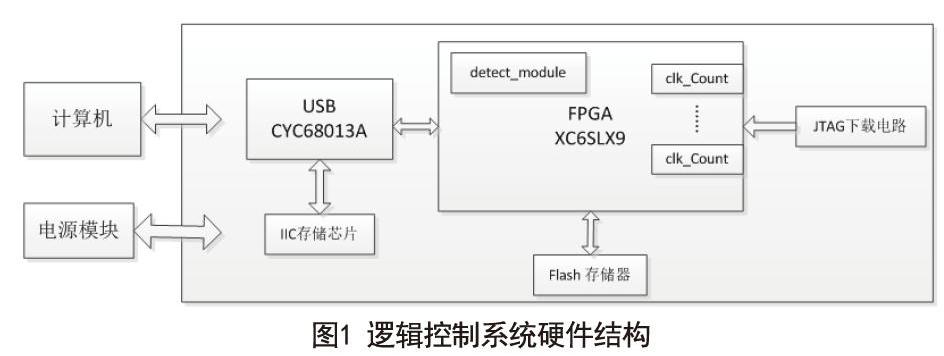

1.1 邏輯控制系統硬件結構

邏輯控制系統的硬件結構如圖1所示,其中電源模塊負責電壓的轉換以及給整個系統各部分供電。FPGA控制模塊包括FPGA最小系統板構成的主控板控制的多達10路的數據采集系統。控制系統完成多路高速數據采集、數據處理、數據通信等功能。其中detec_module 用來讀取DMD輸出的同步信號,clk_Count 讀取探測器的電脈沖信號。其外圍設備有程序燒寫電路的設計,儲存程序的外部Flash芯片的電路設計以及邏輯電平的輸出以及邏輯電平的檢測。

USB控制器用來實現FPGA和計算機之間的高速數據傳輸。USB接收到計算機發送的指令后,執行相應的操作[3],并將采集到的數據通過USB上傳到上位機進行存儲。其中IIC存儲芯片用來存儲程序,避免因掉電而丟失。

1.2 FPGA和USB控制器

本系統所使用的FPGA芯片是Xilinx公司的Spartan6系列的FPGA,型號為XC6SLX9[4-5]。XC6SLX9具有2個時鐘單元,多達9152個邏輯單元,可配置邏輯塊90Kb,具有576Kb塊存儲RAM,能夠滿足本系統的要求。

USB控制器則使用的是Cypress公司的EZ-USB FX2LP系列的CYC68013A。CY7C68013A 是一款集成增強型的 8051 內核、USB 2.0 收發器和 SIE(智能串行接口引擎)的芯片。通用可編程接口GPIF和Slave FIFO是CY7C68013A與外設的兩種接口方式,本系統采用得是Slave FIFO模式[6]。外部邏輯在Slave FIFO模式下可以對CY7C68013A內部多個緩沖區進行讀操作或寫操作而不需要CY7C68013A 的CPU干預,因而可以達到很高的傳輸速率。

2 系統軟件設計

2.1 CYC68013A固件設計

固件是固化在USB接口芯片里面的一段程序,其作用是控制硬件來完成預期的設備功能。Cypress公司為用戶提供了一套功能十分強大的開發包,整個固件的編譯和調試都是在Keil uVision4環境中進行的[7-10]。

其中固件里TD_Init()主要完成對CY7C68013A的初始化,USB啟動以后會調用一次。程序里對TD_Init()函數中相關寄存器進行配置,使其工作與同步Slave FIFO模式下即可。此時時鐘仍然由USB外部晶振提供,上電后系統還需要進行狀態切換才能使之工作在外部時鐘模式下,具體操作在TD_Poll()函數中完成。程序編寫完成后,對工程進行編譯鏈接,最終生成對應的.IIC文件,通過官方固件開發軟件下載到CY7C68013A芯片的外部IIC存儲芯片。

2.2 Verilog 程序設計

該FPGA系統包含兩個功能性的子模塊,如下圖所示:

DMD每輸出一個上升沿,TTL_P 電平拉高一個時鐘周期,然后拉低。Start_Countx 為模塊啟動信號。當 Start_Countx 為 1 時。探測器每來一個脈沖,Countx_Data 加 1;當 Start_Countx 為 0 時,Countx_Data 為 始終為0。

上電之后系統處于接收指令的狀態,當USB接收到相應的指令并且FPGA讀取完畢之后,

當檢測到TTL_P的高電平,讀取Countx_Data的值先存入緩沖區當中,等待發送。隨后拉低 Start_Countx,清空 Countx_Data。接著拉高 Start_Countx,重新計數。接著開始發送緩沖區中的數據,發送完畢之后,再次處于檢測TTL_P的電平。

USB時鐘由FPGA提供,FPGA的50MHz時鐘分頻而出的25MHz的時鐘。在slave FIFO模式下,每2個時鐘周期即可完成一個字節數據的寫入。USB接收的數據格式為Cx(2)+標號(4)+脈沖個數(4)(括號里為字節數),其中標號在TTL_P為高電平時會自動加 1。每個clk_Count模塊上傳的數據總個數為10個字節,USB可以傳輸在DMD脈沖信號的最短周期內(100us)傳輸2500 Bytes的數據,理論上可以外接250路clk_Count模塊,考慮到模塊之間的延遲、FPGA外部引腳數的限制以及實際項目中的需求,本系統只做10路即可。

3 結束語

本系統最終實現了通過FPGA和USB 2.0接口芯片CY7C68013A來完成脈沖個數的采集以及傳輸,實現了預期的目標。實際測試表明,本系統的通信接口最高速率達到了100Mbps,并且數據高速穩定可靠。不足之處在于CY7C68013A 的同步Slave FIFO 模式下進行數據傳輸,一共有 16 根數據總線,所以USB的通信速率可進一步提高。

參考文獻

[1]關云飛. 基于FPGA的差動像散離焦信號的檢測和處理技術[D].哈爾濱工程大學,2012.

[2]關珊珊. 基于FPGA的圖像顯示技術研究[D].南京航空航天大學,2012.

[3]溫新民. 基于ARM的伺服控制器在竹節紗裝置中的應用研究[D].上海交通大學,2010.

[4]張丹紅,潘鋒. 基于USB2.0總線的高速數據采集系統設計[J]. 傳感器世界,2009,04:42-45.

[5]魯林,劉文怡,王浩. 基于FPGA的微型數字存儲系統設計[J]. 電子設計工程,2009,09:1-2+5.

[6]羅進. FPGA在高速多通道光纖光柵解調儀表中的應用[D].武漢郵電科學研究院,2012.

[8]羅向東. 基于FPGA與CY7C68013A的USB接口系統設計[J]. 科技廣場,2010,06:96-98.

[9]張聰,張濤. 基于USB3.0設備控制器的固件設計[J]. 電子器件,2013,03:383-388.

[10]張惠民. 基于GY7C68013A芯片的數據采集裝置研究[D].太原科技大學,2008.

[11]韋偉. 基于USB2.0的CCD相機系統的設計與實現[D].南京理工大學,2009.

[12]周玉龍. 基于FPGA的高速數據傳輸及存儲系統設計與實現[D].電子科技大學,2010.