電流饋電式半橋熒光燈鎮流器的建模及設計

王青松, 程明

(東南大學電氣工程學院,江蘇南京210096)

電流饋電式半橋熒光燈鎮流器的建模及設計

王青松, 程明

(東南大學電氣工程學院,江蘇南京210096)

針對電流饋電式半橋熒光燈電子鎮流器的產品設計過程無理論可循、僅僅依靠工程經驗試湊參數的問題,探討了鎮流器穩態運行時影響燈管壽命的關鍵因素,基于等效分析法和相量法建立了拓撲的等效模型并推導了相關公式,提出了電路中關鍵元件參數的理論計算方法。在不改變電路拓撲的情況下,通過優化設計電路參數,可在保證系統原有性能的基礎上進一步減小燈電流的波峰系數(crest factor,CF),通過仿真及實驗驗證了所建模型及理論計算的準確性,最后通過對比說明經建模后得出的新參數使得燈電流的CF低于原設計,從而有效緩解燈電流對燈管壽命的影響,提高了系統的可靠性。

拓撲建模;參數設計;熒光燈;電子鎮流器;電流饋電式;波峰系數

0 引 言

熒光燈[1]因高效節能正在取代傳統的白熾燈,在國民經濟的各行各業獲得了廣泛應用。電子鎮流器[2-4]作為熒光燈的驅動器,其性能的優劣不僅直接影響熒光燈的照明效果,而且影響熒光燈的壽命。當前,電流饋電式半橋熒光燈電子鎮流器以其成本低以及安全的隔離輸出等優勢被國內外眾多廠商所采用[5]。然而,隨著大量產品投放市場,電子鎮流失效所導致的燈具損壞問題日益凸顯,失效的元件主要是主開關管、續流電容和磁元件等。更為嚴重的是,電子鎮流器參數設計不合理還會影響燈管使用壽命,導致使用成本增加,出現了熒光燈“省電不省錢”現象,這在一定程度上阻礙了熒光燈及電子鎮流器的推廣使用。有關廠商雖然對產品不斷進行改進,但始終沒能從根本上解決這一問題。究其原因,目前主要依靠經驗來設計選擇電路參數,缺少深人的理論分析和精細的設計。國內已見有關該拓撲的介紹文獻[1],但國內外還未見有關建模的文獻。因此,深人研究并構建該拓撲的數學模型、分析其工作模式,從而進行電路的優化設計,顯得迫在眉睫。

本文以驅動F32T8[6-7]燈管的無預熱型電子鎮流器的主拓撲[8]為研究對象,對其進行理論建模和仿真分析,并進行了實驗驗證。在此基礎上,給出了關鍵參數的計算公式,為下一步實現對該拓撲的優化改進奠定了理論基礎。

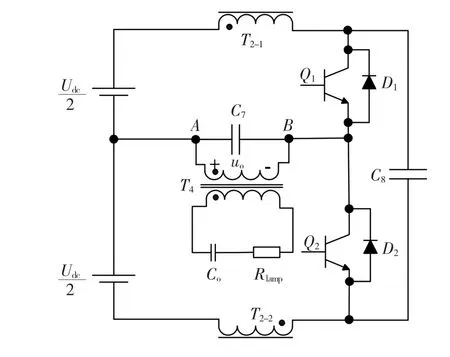

1 拓撲主電路介紹

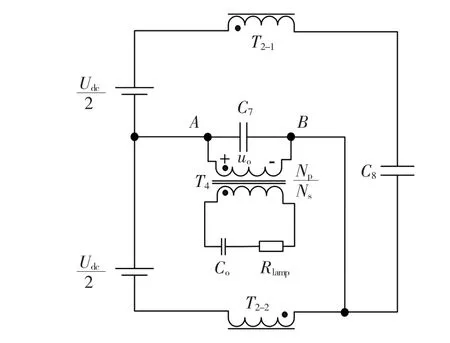

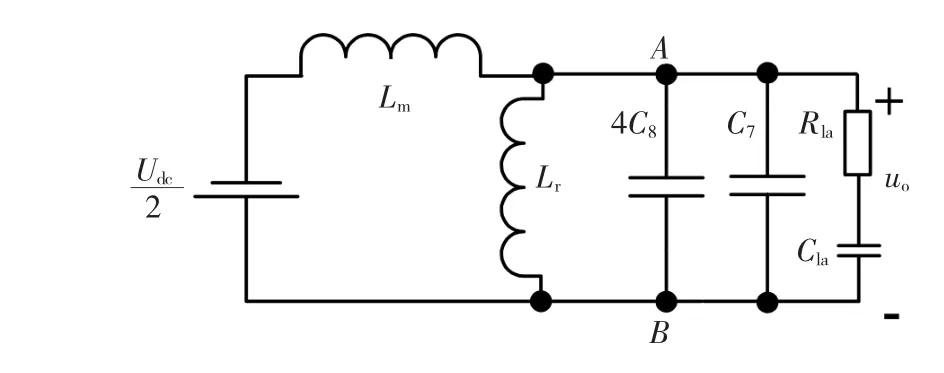

如圖1所示為電流饋電式半橋主拓撲,T2是饋流電感,共兩個繞組,激磁電感量為Lm,匝比為1:1; T4為輸出變壓器,原邊電感量為Lr,原邊匝數為Np,與電容C7并聯,一組副邊繞組與電容Co和燈負載(Rlamp)的串聯組合并聯,匝數為Ns;D1、D2分別與Q1、Q2并聯,主要作用是續流;C8與兩個開關管并聯,也起緩沖續流作用,整個電路的具體工作過程詳見參考文獻[1],本文沿用參考文獻[1]中元件的符號,比如T2、T4、C7、C8等。

圖1 電流饋電式半橋拓撲圖Fig.1 Topology of current fed half bridge

2 穩態運行時影響燈管壽命的因素

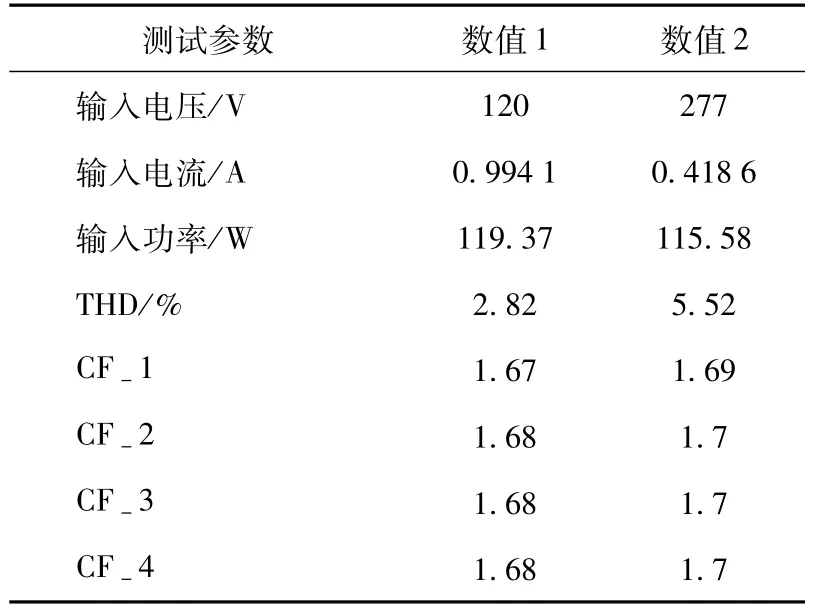

當電子鎮流器穩態運行時,影響燈管壽命的主要因素是燈電流波峰系數(crest factor,CF)。CF定義為燈電流的峰峰值的一半再除以有效值。如果燈電流中沒有高次諧波,那么CF應該等于或略大于1.414。UL935標準強制規定CF值小于1.7。實際設計電路時必須留有余量,CF的理論值一般設計在1.65以下,否則燈電流的毛刺會使得峰峰值增大而導致CF值超出1.7,這種問題特別會出現在帶多種負載的電子鎮流器中。以文中所舉4燈F32T8并聯負載為例,測得現有投人北美市場的一款鎮流器的參數如表1。

表1 現有電子鎮流器工作參數值Table 1 Performances of existing electric ballasts

由表1可知,當輸人電壓為277V時,每個燈的CF都接近1.7,這種設計顯然會影響到燈管的使用壽命。

3 等效模型的建立

主電路是典型的并聯諧振電路。T4原邊繞組與C7等電容組成了并聯Tank,電路工作在準諧振狀態,能量通過T4的副邊傳遞給燈負載。直流母線電壓Udc經過T2后轉換成電流輸人Tank,不斷補充Tank在工作過程中的能量損耗,使得振蕩能不停地維持下去[1]。本文的分析基于如下假設:T2和T4都是全藕合變壓器,原邊激磁電感量分別為Lm和Lr,且Lm?Lr。若將D1和Q1視為半橋電路的上橋臂,D2和Q2視為下橋臂,則任意時刻上、下橋臂同時只能有一組處于通態,否則將會引起短路故障。因而,建模的思路可以基于上、下橋臂的錯時導通建立分階段的等效電路模型。本文中下橋臂導通且上橋臂關斷定義為階段1,上橋臂導通且下橋臂關斷則定義為階段2。

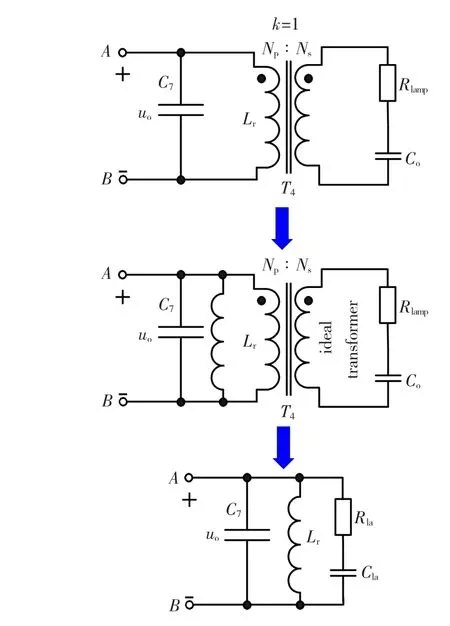

3.1 Rlamp與Co的等效

對圖1中節點A和B之間的電路進行等效,利用全藕合變壓器的特性將變壓器T4副邊所帶的負載Co和Rlamp這算到原邊,等效過程如圖2。

圖2 Rlamp與Co的等效過程Fig.2 Equivalent circuit of Rlampand Co

圖2 中

3.2 階段1等效電路模型的建立

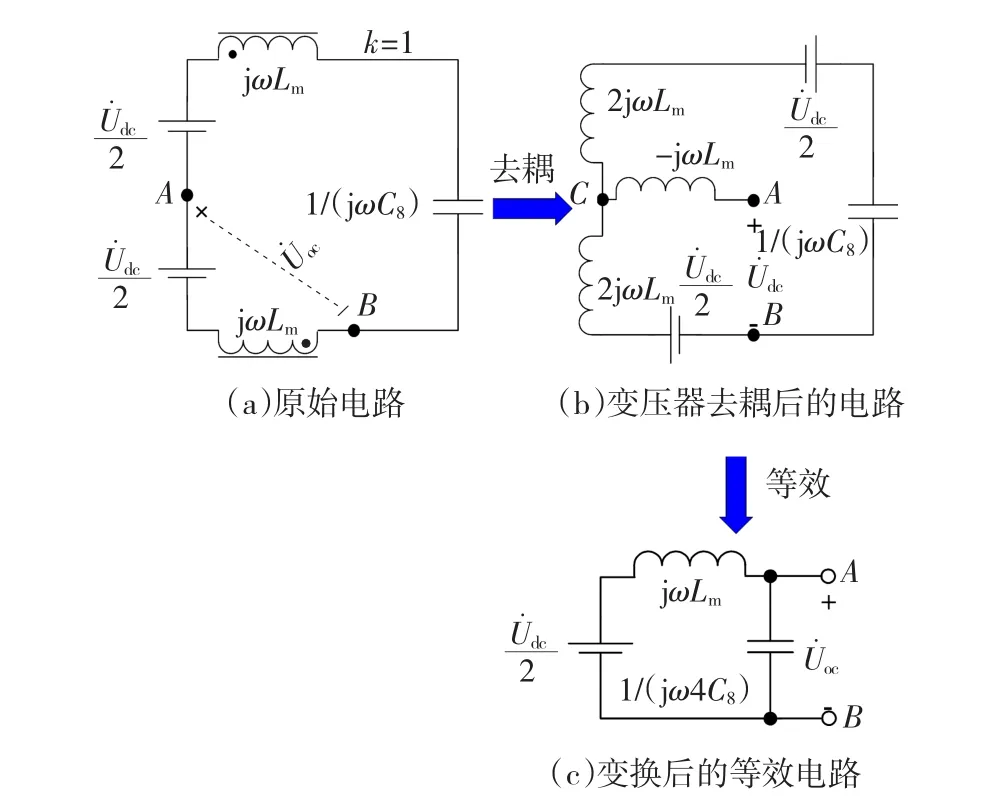

階段1的電路模型如圖3,上臂關斷且下臂導通。以下利用等效的思想建立除3.1所示電路之外的等效電路模型(主要包括電源、T2、Q1、Q2、D1、D2和C8)。利用相量分析法建模,具體過程如圖4,其中U·oc為AB端口的開路電壓相量,設此時AB端口的等效戴維南阻抗為Z0。

圖3 階段1的情形Fig.3 Scenario of phase1

圖4 階段1時關鍵元件的等效相量模型等效過程Fig.4 Equivalent phasor model of key com ponents at phase1

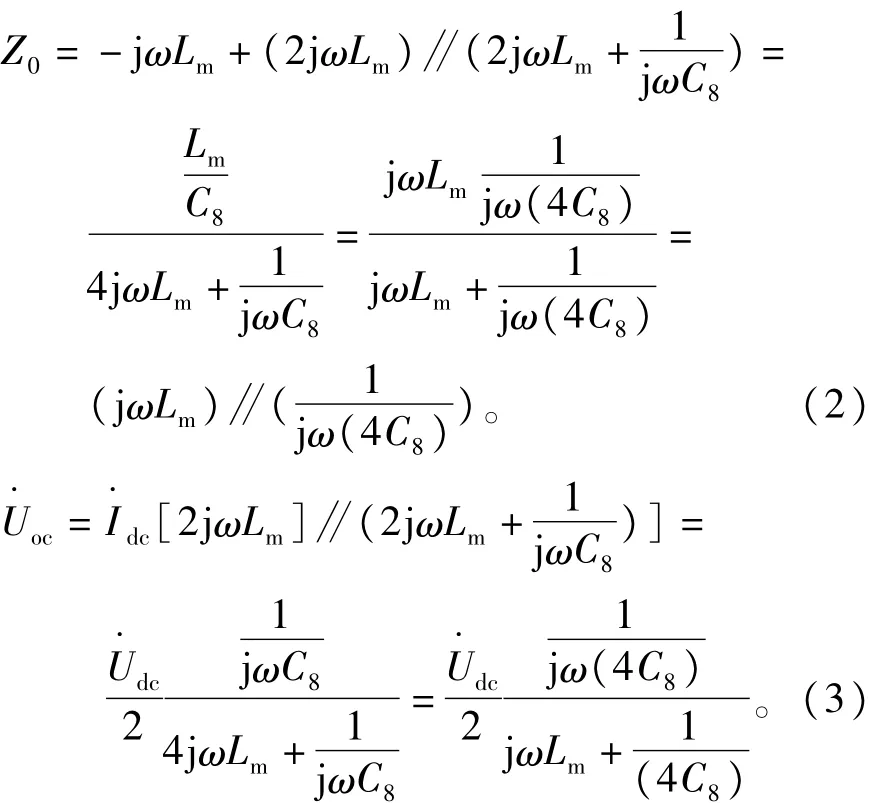

圖4 (b)中,可以計算出AB端的等效戴維南阻抗和開路電壓分別如式(2)和式(3)。

同理可以計算出圖4(c)中AB端的開路電壓和等效阻抗,結果與圖4(b)完全一致,根據等效的定義可以看出圖4(b)與圖4(c)的電路相互等效。故可得出階段1的等效電路模型如圖5所示。

圖5 階段1的等效電路模型Fig.5 Equivalent circuit of phase 1

3.3 階段2等效電路模型的建立

同理可得階段2等效電路模型如圖6所示。

圖6 階段2的等效電路模型Fig.6 Equivalent circuit of phase 2

3.4 整個主電路拓撲的等效電路模型

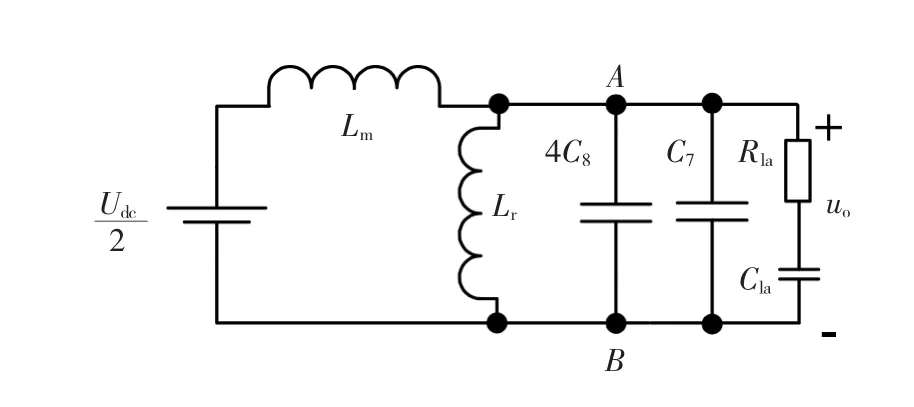

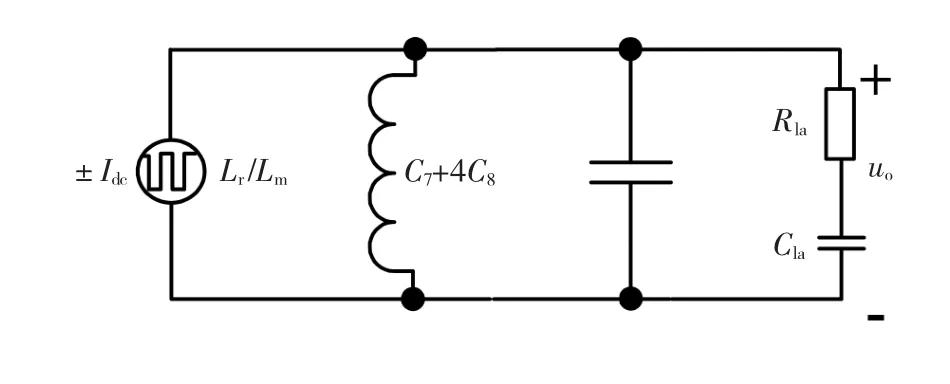

當T2的激磁電感量Lm足夠大時,電壓源經過大電感之后轉換成電流注人Tank,利用諾頓定理對圖5和圖6中的電路進一步化簡可得階段1和階段2總的電路模型如圖7。

圖7 電流饋電式半橋拓撲的等效電路模型Fig.7 Equivalent circuit of current fed half bridge topology

3.5 關鍵參數計算

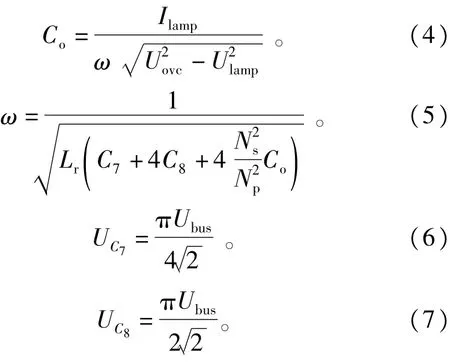

根據所建模型可以得出電路參數的計算公式如式(4)~式(7)。

以4燈F32T8并聯負載為例,設計要求:總負載功率Plamp為110W,電路工作頻率f為42 kHz,變壓器T4副邊輸出電壓有效值Uovc為587 V。已知: Lm//Lr≈Lr;前級PFC輸出Udc為460 V;燈的特性曲線顯示當Ilamp為183mA時,燈電壓Ulamp約為150 V,此時單燈功率約為27.5W。假設每個燈的工作狀態相同,根據經驗首先作如下設計:T4副邊與原邊的匝比為2.3;C和C的值分別選為4.7 nF和1 nF,78鎮流電容值為1.2 nF。根據式(4)~式(7)可算出Lr及關鍵元件電壓理論上的有效值:Lr=408μH, UC7RMS=255 V,UC8RMS=511 V。

3.6 模型仿真及實驗驗證

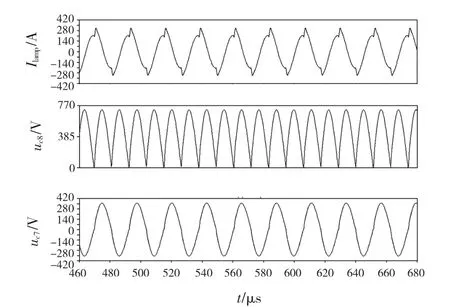

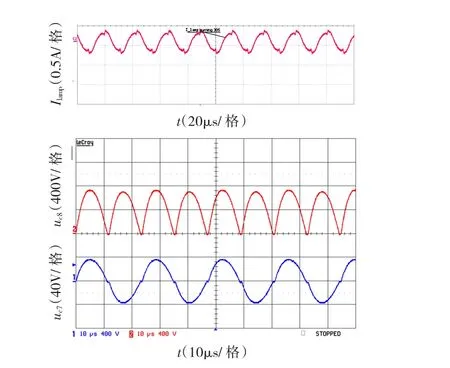

基于上述參數的仿真結果如圖8。C7和C8的電壓有效值分別為255 V和511 V,與理論計算一致,燈電流的有效值為188 mA,仿真結果比理論值大了5mA,其主要原因是仿真電路中用純電阻代替了實際的燈負載。圖9的實驗結果也與理論計算值相當。仿真與實驗結果驗證了本文所建模型的準確性。

圖8 穩態時電容C7、C8電壓以及燈電流仿真波形Fig.8 Simulation waveform s of voltage on C7and C8and lam p current

圖9 穩態時燈電流以及電容C8、C7電壓實驗波形Fig.9 Experimentalwaveform s of lam p current and voltage on C8and C7

3.7 拓撲建模前后的CF值對比

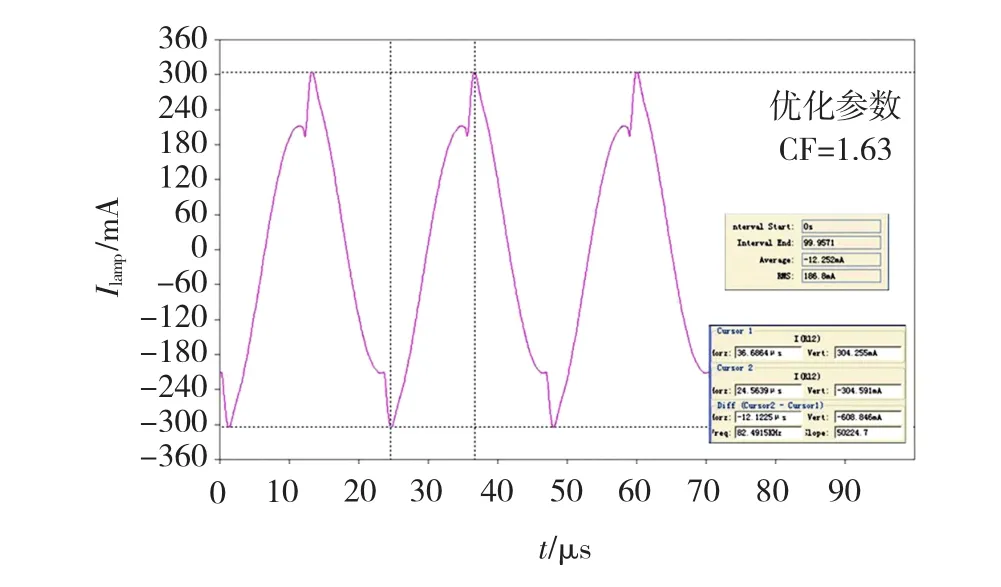

在相同的條件下,參數的重新設計主要是針對T4原邊電感量Lr所進行的。原設計的Lr根據經驗選取值為385μH,重新設計的參數為408μH。當然,匝比不變的情況下,T4副邊的電感量也隨之變化。圖10是原設計中燈電流的CF值,圖11是拓撲建模后的CF值。

圖10 原設計中燈電流的CF值Fig.10 CF value of lamp current in existing design

圖11 拓撲建模后的CF值Fig.11 CF value of lamp current after topology modeling

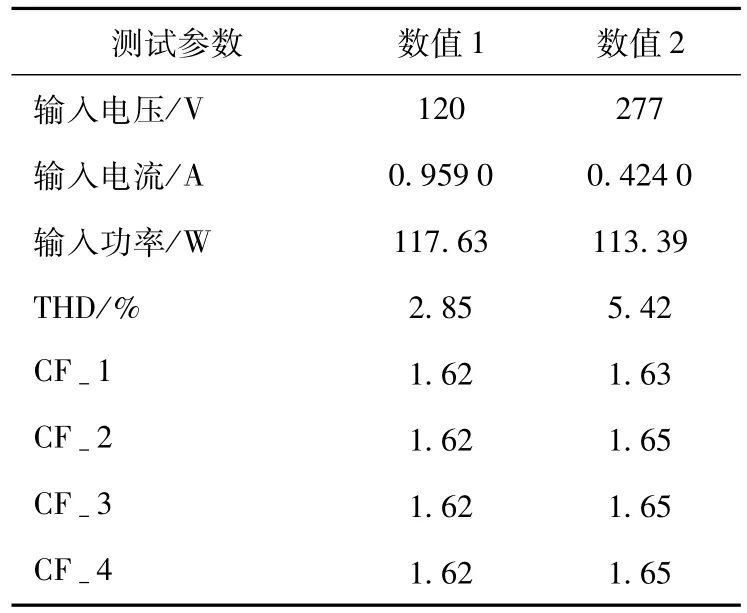

由圖10和圖11可知,原設計中的CF值為1.67,而拓撲建模后的CF值為1.63。前者的裕量很小,只要稍微有點干擾,燈管實際工作時的CF就會達到或超過1.7,而后者明顯小于經驗值1.65,滿足要求,實驗結果如表2,與仿真結果一致,這樣的CF值可以有效緩解燈管壽命短的問題。

表2 拓撲建模后的電子鎮流器工作參數值Table 2 Performances of electric ballasts after topology modeling

注意,表2中的Crest Factor-1~4分別表示4個燈管的CF值,每個燈管的測量順序是隨機的。

4 結 論

本文深人研究了傳統的電流饋電式拓撲結構。文中運用正弦穩態電路的阻抗變換法、變壓器理論、相量法[6]等相關知識,采用階段分析法對拓撲建立了等效工作模型,在此基礎上得出了主電路中關鍵元件的參數計算方法,最后通過仿真及實驗驗證了所建模型和參數計算方法的準確性,通過參數的重新設計降低了燈電流的CF,能在一定程度上延長燈管的使用壽命。本文的成果對于深人理解電流饋電式拓撲有很大幫助,為進一步研究和利用此拓撲提供了理論依據,并為實現對此拓撲的優化改進奠定了堅實的基礎。

[1] 陳丹江,張偉.熒光燈模型綜述[J].照明工程學報,2007,18 (2):20-24. CHEN Danjiang,ZHANG Wei.Summary of fluorescent lamp models[J].China Illuminating Engineering Journal,2007,18 (2):20-24.

[2] 楊世光.熒光燈電子鎮流器的新進展[J].照明工程學報,2004,15(1):43-45. YANG Shiguang.New development of electronic ballast for fluorescent lamps[J].China Illuminating Engineering Journal,2004,15(1):43-45.

[3] LASKAIL,ENJETIP N,PITEL I J.White-noise modulation of high-frequency high-intensity discharge lamp ballasts[J].IEEE Transactions on Industry Applications,1998,34(3):597.

[4] CHENG C A,LIANG T J,CHUANG CM,etal.A novelmethod of using second-order lamp model to design dimmable fluorescent lamps electronic ballast[C]//2001 IEEE IECON annual conference,Nov./Dec.,2001,Denver,USA.2001,2:1033-1037.

[5] 王青松,胡冰新,劉景夏,等.一種電流饋電式半橋拓撲的研究[J].解放軍理工大學學報:自然科學版,2013,14(5):490 -493. WANG Qingsong,HU Bingxin,LIU Jingxia,et al.Current fed half bridge topology[J].Journal of PLA Univrsity of Science and Technology:Natural Science Editon,2013,14(5):490-493.

[6] CERVIM,SEIDEL A R,BISOGNO F E,etal.Fluorescent lamp model based on the equivalent variation[C]//2002 IEEE IASannual meeting,Oct.,2002,Pittsburgh,USA.2002,1:680 -684.

[7] SUN M,HESTERMAN B L.PSpice high-frequency dynamic fluorescent lamp model[J].IEEE Transactions on Industry Applications,1998,13(2):261-272.

[8] STEIGERWALD R L.A comparison of half-bridge resonant converter topologies[J].IEEE Transactions on Power Electronics,1988,3(2):174-182.

[9] DIAZ F J,AZCONDO F J,CASANUEVA R,et al.Digital control of a low-frequency square-wave electronic ballastwith resonant ignition[J].IEEE Transactions on Industrial Electronics,2008,55(9):3180-3191.

[10] YAN W,TAM E,HUIS Y R.A semi-theoretical fluorescent lampmodel for time-domain transientand steady-state simulations[J].IEEE Transactions on Power Electronics,2007,22(6): 2106-2115.

[11] LIN R L,WANG Z Q.2.56-MHz self-oscillating electronic ballastwith constant-lamp current control formetal halide lamp[J]. IEEE Transactions on Power Electronics,2007,22(3):839 -844.

[12] DEMORAISA S,FARIASV J,DEFREITASLC,etal.A high power factor ballast using a single switch with both power stages integrated[J].IEEE Transactions on Power Electronics,2006,21(2):524-531.

[13] CHEN M R.The standard requirements and current development of American-style fluorescent lamp electronic ballast[J].Journal of China Light&Lighting,2008,2:34-38.

(編輯:劉琳琳)

M odeling and parameter optim ization of current fed half bridge topology in fluorescent lam p electronic ballast

WANG Qing-song, CHENG Ming

(School of Electrical Engineering,Southeast University,Nanjing 210096,China)

To solve the issue that there is no theoretical guidance during product design for electric ballasts using current fed half bridge topologies,the key factor to lamp life at stable state was discussed first.Topologymodeling was introduced and relevant formulaswere provided based on equivalent analysis and phasormethod.And then an equivalent circuitmodel was set up and method for parameter selection of key componentswas given.Without any change of the topology,the crest fact(CF)of lamp current was reduced by parameter optimization of the key components.The accuracy of the model and the method was validated by simulative and experimentalwaveforms.Finally,a comparison was done to verify that lamp life can be raised effectively through parametermodification of themain circuit based on topologymodeling.

topologymodeling;parameter design;fluorescent lamp;electronic ballast;current fed;crest factor

10.15938/j.emc.2015.09.006

TM 923.61

A

1007-449X(2015)09-0040-06

2014-01-20

國家自然科學基金(51320105002);教育部博士點基金(20120092130008)

王青松(1982—),男,博士研究生,研究方向為電子鎮流器、電流型多電平、新能源發電控制技術等;程 明(1960—),男,教授,博士生導師,研究方向為電機與控制、新能源發電、電動汽車等。

王青松