基于以太網(wǎng)的加速度傳感器數(shù)據(jù)采集傳輸系統(tǒng)設(shè)計(jì)*

鄒 坤,石云波,焦佳偉,趙 赟,賀 婷

(1.中北大學(xué),山西 太原030051;2.蘇州中盛納米科技有限公司,江蘇 蘇州215123;3.電子測(cè)試技術(shù)國(guó)防重點(diǎn)實(shí)驗(yàn)室,山西 太原030051)

0 引 言

對(duì)于大量的數(shù)據(jù)進(jìn)行采集、傳輸、處理和存儲(chǔ),采用串口方式已經(jīng)不能滿(mǎn)足系統(tǒng)的需求,通過(guò)串口傳輸步進(jìn)速度比較慢,而且傳輸模式單一,誤碼率比較高,不能適應(yīng)越開(kāi)越快的工業(yè)和軍事的發(fā)展。而以太網(wǎng)不僅兼容性好,通信速度快,傳輸距離遠(yuǎn)而且利于上位機(jī)交互,在上位機(jī)軟件中也有成熟的以太網(wǎng)接口函數(shù)[1]。

本文提出了一種基于以太網(wǎng)的加速度傳感器數(shù)據(jù)采集傳輸系統(tǒng)設(shè)計(jì)方案,采用FPGA 為主控芯片,完成了數(shù)據(jù)的接收轉(zhuǎn)換成數(shù)據(jù)幀進(jìn)行傳輸[2]。采用AD7667 做為高速A/D 轉(zhuǎn)換芯片。AD7667 作為一個(gè)16 位的高速A/D 轉(zhuǎn)換芯片,由一個(gè)單一的5 V 供電,內(nèi)部包含一個(gè)高速16 位采樣A/D 轉(zhuǎn)換器,并且具有低功耗應(yīng)用的電源減少模式(impulse 模式)。

W5300 是一種0.18 μm CMOS 工藝的單芯片器件,內(nèi)部集成10/100 M 以太網(wǎng)控制器,MAC 和TCP/IP 協(xié)議棧。W5300 使用方便、穩(wěn)定可靠,廣泛應(yīng)用于高性能、低成本的Internet 嵌入式領(lǐng)域。通過(guò)一個(gè)集成有TCP/IP 協(xié)議和10/100M 的以太網(wǎng)MAC 和PHY 的單芯片可以非常簡(jiǎn)單和快捷地實(shí)現(xiàn)Internet 連接。

1 系統(tǒng)硬件設(shè)計(jì)

1.1 硬件總體結(jié)構(gòu)

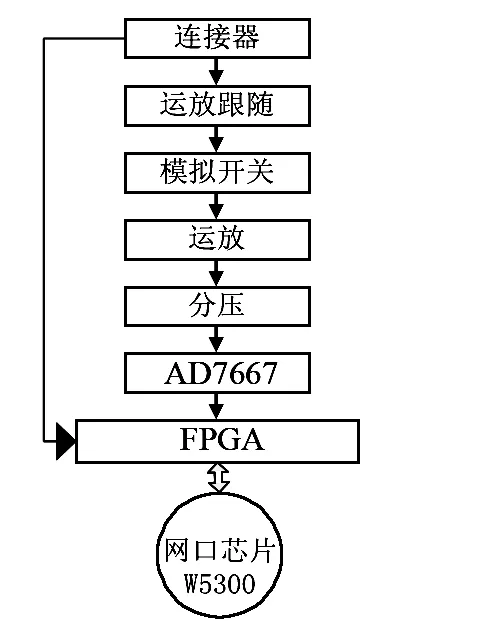

加速度傳感器數(shù)據(jù)采集傳輸系統(tǒng)的硬件總體框圖如圖1所示。主要采用了連接器、運(yùn)放跟隨、模擬開(kāi)關(guān),AD 控制模塊AD7667,F(xiàn)PGA 主控芯片和以太網(wǎng)數(shù)據(jù)傳輸模塊W5300。

FPGA 芯片在該系統(tǒng)中主要完成對(duì)采集到的信號(hào)進(jìn)行預(yù)處理控制、數(shù)據(jù)接收,控制A/D 轉(zhuǎn)換芯片把模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào),并且按照自定義的幀格式通過(guò)網(wǎng)線(xiàn)傳輸?shù)接?jì)算機(jī)。

W5300 網(wǎng)口芯片是處理主機(jī)訪(fǎng)問(wèn)網(wǎng)絡(luò)媒體的操作,把來(lái)自FPGA 的數(shù)據(jù)包封裝成幀,在編碼成信號(hào),發(fā)送到網(wǎng)絡(luò)上。W5300 內(nèi)部集成了TCP/IP 內(nèi)核和微控制器,使其能滿(mǎn)足高速通信的需求。

圖1 硬件總體框圖Fig 1 Overall block diagram of hardware

1.2 A/D 轉(zhuǎn)換電路設(shè)計(jì)

A/D 轉(zhuǎn)換器是采集傳輸系統(tǒng)電路部分的核心,在整個(gè)系統(tǒng)中有不可或缺的地位。高精度、低功耗的ADC 是數(shù)據(jù)高效采集的保證。AD7667 具有非常高的采樣率模式,用于異步應(yīng)用的快速模式和為了低功耗應(yīng)用的電源減少模式(Impulse 模式)。

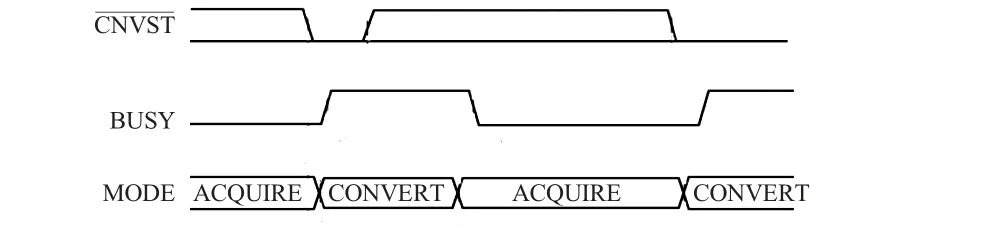

在Impulse 模式下,可以自動(dòng)進(jìn)行初始化轉(zhuǎn)換。根據(jù)時(shí)序圖2 所示,在BUSY 低的時(shí)候也保持低電平,這時(shí)AD7667 為控制采集階段,并自動(dòng)啟動(dòng)一個(gè)新的轉(zhuǎn)換。通過(guò)保持為低電平,AD7667 通過(guò)自身使轉(zhuǎn)換進(jìn)程運(yùn)行。需要指出的是,當(dāng)BUSY 變低的時(shí)候模擬輸入必須保持不變。另外,在上電時(shí),一旦要啟動(dòng)轉(zhuǎn)換過(guò)程就要變低。在這種模式下,AD7667 可以超過(guò)Impulse 模式下的666kSPS 的運(yùn)行速度的限制而稍微更快一些。

圖2 AD7667 基本轉(zhuǎn)換時(shí)序Fig 2 Basic conversion timing of AD7667

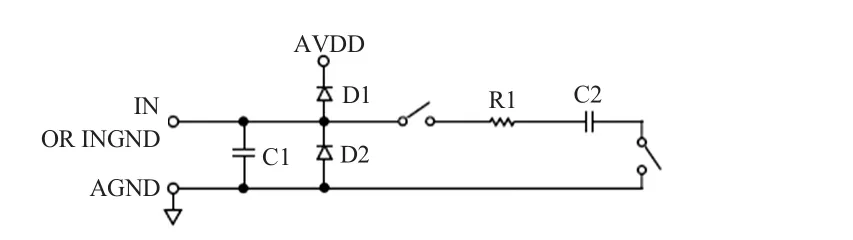

AD7667 的等效模擬輸入電路圖如圖3 所示,兩個(gè)二極管D1,D2 為模擬輸入端IN 和INGND 提供ESD 保護(hù)。在采樣階段,模擬輸入IN 的阻抗可以建模為由電容器C1 和由電阻器R1 串聯(lián)形成的網(wǎng)絡(luò)和C2 組成的并行連接。C1是主要引腳電容器,R1 的阻值為168Ω,是一個(gè)由一些串行電阻器組成的集總元件。C2 的電容值為60 pF,主要是A/D 轉(zhuǎn)換芯片的采樣電容器。在轉(zhuǎn)換過(guò)程中,開(kāi)關(guān)被打開(kāi),輸入阻抗被限制到C1。R1 和C2 組成了單極的低通濾波器,從而降低不良疊效應(yīng),限制了噪音[3]。

圖3 等效模擬輸入電路Fig 3 Equivalent analog input circuit

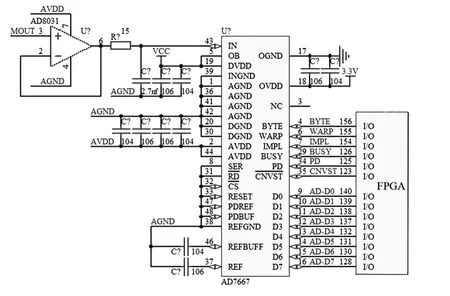

其與FPGA 的電路連接圖如圖4 所示。

圖4 A/D 轉(zhuǎn)換連接圖設(shè)計(jì)Fig 4 Design of A/D converting connection circuit

1.3 以太網(wǎng)傳輸接口設(shè)計(jì)

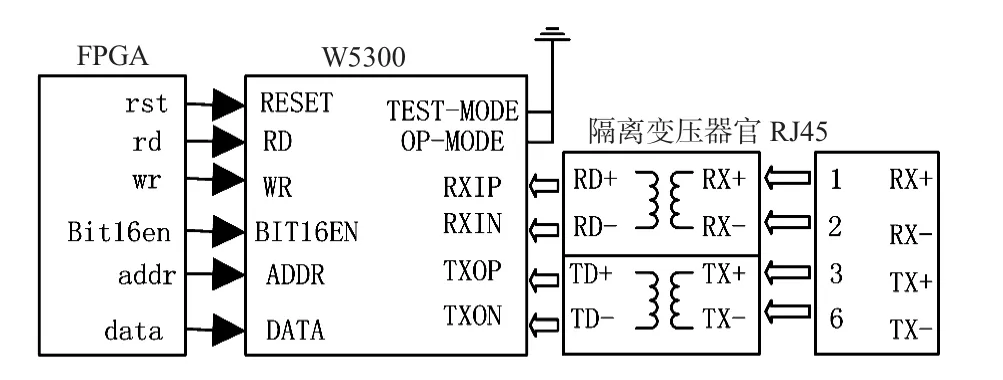

以太網(wǎng)的設(shè)計(jì)主要是通過(guò)FPGA 設(shè)置BIT16EN 信號(hào)為高電平,實(shí)現(xiàn)W5300 的16 位數(shù)據(jù)總線(xiàn)工作模式,采用直接尋址方式。為了提高數(shù)據(jù)傳輸?shù)目乖肼暷芰蛿?shù)據(jù)的穩(wěn)定性、傳輸距離等問(wèn)題,W5300 和RJ45 之間采用網(wǎng)絡(luò)隔離變壓器進(jìn)行連接,提高了以太網(wǎng)高頻的要求,同時(shí)有效地保護(hù)了接口電路[4]。W5300 網(wǎng)絡(luò)接口的主要硬件連接原理圖如圖5。

圖5 以太網(wǎng)接口設(shè)計(jì)原理圖Fig 5 Principle diagram of ethernet interface diagram

2 系統(tǒng)軟件設(shè)計(jì)

VC++是一種集成開(kāi)發(fā)環(huán)境,提供了MFC 類(lèi)庫(kù)。MFC是微軟公司對(duì)大部分標(biāo)準(zhǔn)的Win32 API 函數(shù)的封裝,提供了圖形環(huán)境應(yīng)用程序的框架和創(chuàng)建應(yīng)用程序的組件。MFC操作系統(tǒng)界面簡(jiǎn)潔,占用資源少,操作方便,軟件本身提供基于傳輸層TCP 和UDP 協(xié)議的網(wǎng)絡(luò)通信接口。所以,采用MFC 進(jìn)行上位機(jī)軟件設(shè)計(jì)。

2.1 數(shù)據(jù)通信

在數(shù)據(jù)采集傳輸系統(tǒng)的軟件設(shè)計(jì)中,采用以太網(wǎng)進(jìn)行通信,為了減少通信的誤碼率提高通信的成功率與準(zhǔn)確率,采用TCP/IP 通信協(xié)議進(jìn)行以太網(wǎng)數(shù)據(jù)通信,由于傳輸速度較快,因?yàn)椴捎肬DP 的傳輸方式,為了保證數(shù)據(jù)傳輸?shù)目煽啃裕?],制定了相應(yīng)的數(shù)據(jù)幀格式,保證了數(shù)據(jù)的有效性。

數(shù)據(jù)幀格式主要由數(shù)據(jù)包的幀頭、數(shù)據(jù)包大小、數(shù)據(jù)內(nèi)容、校驗(yàn)和、幀尾五個(gè)部分構(gòu)成。

W5300 即為發(fā)送端,其IP 地址是172.0.0.100,PC 作為接收端的IP 地址是172.0.0.200,網(wǎng)絡(luò)連接成功以后就可以進(jìn)行數(shù)據(jù)的收發(fā)。上位機(jī)對(duì)網(wǎng)絡(luò)進(jìn)行設(shè)置,包括目標(biāo)IP 地址、端口號(hào)、接收和發(fā)送緩沖區(qū)大小、分配各Socket 的工作模式[6]。

2.2 數(shù)據(jù)協(xié)議分析

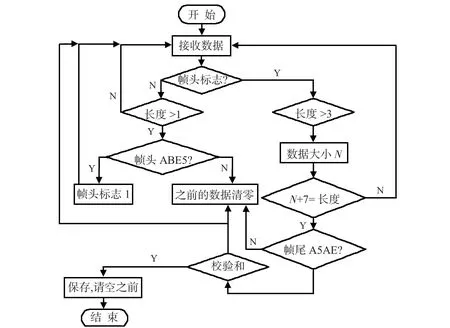

根據(jù)接收到的數(shù)據(jù),上位機(jī)進(jìn)行實(shí)時(shí)的協(xié)議分析。通過(guò)讀取接收緩沖區(qū)中的數(shù)據(jù),對(duì)接收到的字符串進(jìn)行處理。協(xié)議分析流程圖如圖6 所示。

圖6 通信協(xié)議分析流程圖Fig 6 Flow chart of communication protocol analysis

3 試驗(yàn)與結(jié)果

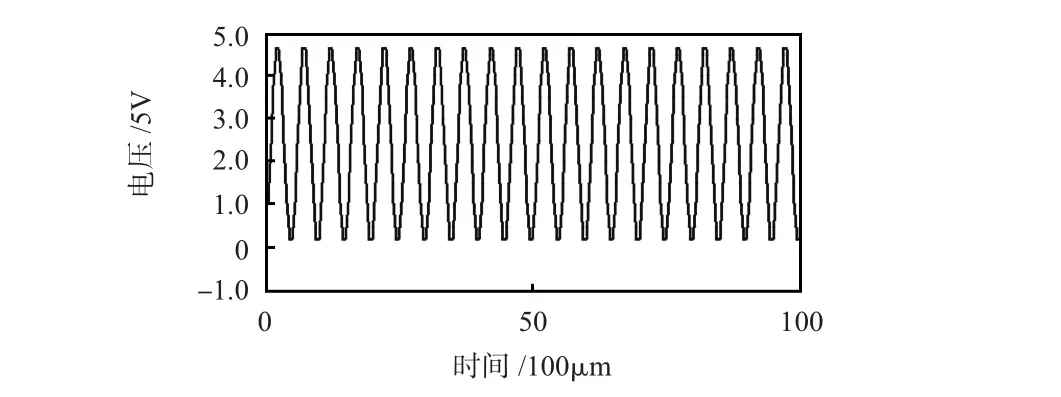

試驗(yàn)在溫度、濕度、振動(dòng)三綜合試驗(yàn)平臺(tái)上,對(duì)標(biāo)準(zhǔn)傳感器進(jìn)行數(shù)據(jù)采集。在溫度為20 ℃,濕度為10%RH,加速度為5 gn,振動(dòng)頻率為2 kHz 的條件下進(jìn)行正弦掃頻試驗(yàn),波形圖如圖7 所示。

在正弦掃頻試驗(yàn)時(shí),輸出電壓是0~5 V 的正弦波,采用標(biāo)準(zhǔn)傳感器采集數(shù)據(jù)傳輸給上位機(jī),雖然有外界影響因素,但是通過(guò)采樣值利用最小二乘法擬合顯示效果比較良好,與振動(dòng)臺(tái)顯示出的波形幾乎一致。經(jīng)過(guò)分析,本系統(tǒng)的數(shù)據(jù)采集系統(tǒng)對(duì)MEMS 加速度傳感器的數(shù)據(jù)能精確地顯示、采集,能滿(mǎn)足軍事、工業(yè)等遠(yuǎn)程數(shù)據(jù)通信系統(tǒng)的需求。

圖7 數(shù)據(jù)采集波形圖Fig 7 Data acquisition waveforms

4 結(jié)束語(yǔ)

本試驗(yàn)利用FPGA 作為主控芯片獲取存儲(chǔ)數(shù)據(jù),通過(guò)選用AD7667 進(jìn)行A/D 轉(zhuǎn)換,利用W5300 使FPGA 與網(wǎng)口進(jìn)行數(shù)據(jù)傳輸,基于網(wǎng)口與電腦的連接利用上位機(jī)軟件對(duì)數(shù)據(jù)進(jìn)行處理。使用以太網(wǎng)的傳輸方式,提高通信的效率。FPGA 芯片的選擇和AD7667 與W5300 的搭配,提高了數(shù)據(jù)傳輸存儲(chǔ)的效率,減小了電路板體積,上位機(jī)進(jìn)行數(shù)據(jù)處理提高了運(yùn)算速度,對(duì)于傳感器的標(biāo)定有較高的參考價(jià)值。

[1] 侯俊杰.深入淺出MFC[M].2 版.武漢:華中科技大學(xué)出版社,2001.

[2] 孫 文.多通道數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[D].長(zhǎng)沙:湖南大學(xué),2013.

[3] 孟祥嬌,張會(huì)新,崔永俊,等.基于FPGA 和AD7667 的16 路采編傳輸系統(tǒng)設(shè)計(jì)[J].自動(dòng)化與儀表,2012,27(11):5-7.

[4] 張 勇,甄國(guó)涌,王麗莉,等.基于W5300 的以太網(wǎng)數(shù)據(jù)傳輸硬件設(shè)計(jì)及優(yōu)化[J].化工自動(dòng)化及儀表,2011,38(8):1-3.

[5] 方 寧.基于以太網(wǎng)的遠(yuǎn)程數(shù)據(jù)采集與數(shù)據(jù)傳輸[D].成都:電子科技大學(xué),2005.

[6] 陳 峰.實(shí)時(shí)信號(hào)數(shù)據(jù)采集系統(tǒng)的研究與設(shè)計(jì)[D].上海:上海交通大學(xué),2010.