基于FPGA 的軟硬件協同實時紙病圖像處理系統*

齊 璐,周 強,王志強

(陜西科技大學 電氣與信息工程學院,陜西 西安710021)

0 引 言

隨著現場可編程門陣列(FPGA)制造工藝和集成技術的不斷發展,利用FPGA 來設計數字硬件系統越來越能體現它在圖像處理中的強大優勢。以往PC 作為圖像處理系統,在高速實驗等對速度要求較高的應用場合中無法滿足實際需求;采用FPGA+數字信號處理器(DSP)相結合的系統[1],方法結構較為復雜,且成本較高,容易造成資源的浪費;若以FPGA 作為核心芯片,因FPGA 本身只適合做一些大數據量,且算法簡單的運算不適合做復雜的運算,這樣的局限性使得它只能實現一些簡單的圖像預處理算法,并沒有在FPGA 中實現完整的圖像算法結構;還有不少方案采用可編程片上系統(SOPC)來完成圖像處理,但都僅僅是將SOPC 當作一個CPU 來使用[2],所有的運算都是在SOPC中實現,并沒有體現出FPGA 的并行運算的特點,無法滿足系統實時性。

針對PC,FPGA+DSP,FPGA,SOPC 等在紙病圖像處理上的不足,本文提出了一種FPGA+SOPC 相結合的紙病圖像處理系統,利用各自優勢來達到實時的紙病圖像處理。紙病圖像從獲取到識別過程最關鍵的在于速度上能否滿足要求。紙病圖像由CCD 相機獲取,FPGA 芯片采用Altera公司的Cyclone IV 系列,用來將采集到的圖片信息進行存儲、處理和顯示。將適合硬件模塊完成的運算用Verilog HDL 編寫,讓硬件模塊能快速實現相對應的功能,如圖像濾波、圖像邊緣檢測等;而對于較為復雜的運算,如流程判斷、圖像識別等運算則交給SOPC 采用C/C++語言實現。最終滿足了紙病圖像處理的快速性和穩定性。

1 系統整體結構

系統整體結構主要由五部分構成,如圖1 所示,分別為CCD 相機、FPGA 芯片、同步動態隨機存取存儲器(SDRAM)芯片、數/模轉換器(DAC)芯片及液晶顯示器(LCD)。其中,CCD 相機選用DALSA 公司的Spyder3 系列的線陣相機;DDR2 SDRAM 采用MT47H64M16 芯片,該芯片的總存儲量達到1GB,SDRAM 采用IS42S16160B;FPGA 芯片采用Cyclone IV 系列芯片LCD 采用的是計算機的顯示屏。

圖1 系統結構整體框圖Fig 1 Overall block diagram of system structure

紙病圖像采集是FPGA 上的SOPC 通過系統總線控制圖像采集模塊,圖像采集模塊再控制CCD 相機來實現的,將采集到的數據存儲在外部存儲器DDR2 SDRAM 中,然后SOPC 對圖像處理算法進行判斷和分類,將適合硬件完成處理的步驟通過總線將相應的參數和命令發送給對應的硬件模塊,硬件模塊在完成相應的處理后再通過總線反饋結束信號給SOPC。對于不適合硬件處理的算法則交給SOPC,由SOPC 利用其內部的CPU 進行運算,這兩部分運算是相互獨立、互不依賴的,實現了模塊間的并行加速。在整個紙病圖像處理系統中,SOPC 一直按照這樣的方法來處理,直到處理結束,處理完成后的圖像通過LCD 顯示出來,以便人工進行圖像判斷,對算法進行改進和優化,以滿足實際的應用要求[3]。

2 基于FPGA 的軟硬件協同紙病圖像處理系統

紙病圖像處理過程可以分為圖像預處理、特征提取和紙病辨識三部分,本系統將FPGA 的軟硬件相結合使用,圖像預處理的工作仍然由FPGA 的Verilog HDL 來描述與執行,特征提取與紙病辨識則由FPGA 上的SOPC 完成,計算機只承擔紙病后期處理的任務,該系統不僅節約了成本,還使得紙病圖像處理得到了并行加速。具體過程見圖2。

圖2 基于FPGA 的紙病圖像處理系統框圖Fig 2 Block diagram of paper defect image processing system based on FPGA

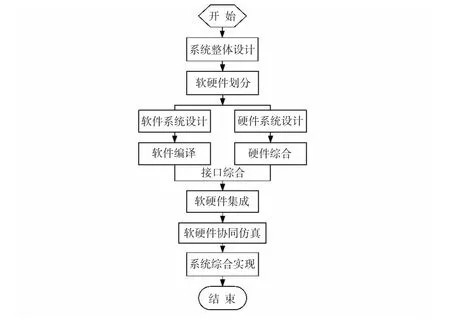

軟硬件協同就是同時設計系統的硬件和軟件部分,使系統間的相互影響因素可以協調地完成需要實現的功能,提高系統的執行速度,同時還增強了系統的穩定性[4],軟硬件協同的設計流程圖如圖3 所示。

圖3 軟硬件協調設計流程圖Fig 3 Flow chart of hardware software coordination design

2.1 硬件模式下的紙病圖像預處理

硬件模式下的紙病圖像預處理是指適合用硬件描述語言(HDL)來完成編寫和實現的圖像處理,圖像預處理一般分為濾波與邊緣檢測等。圖像預處理是圖像識別前的必要步驟,經過預處理后的圖像為后續的處理打好基礎。

2.1.1 紙病圖像濾波

圖像濾波的方式多種多樣,常見的有均值濾波、高斯濾波和中值濾波。通過濾波可以減少圖像的噪聲,凸顯有效信息。一般來說,攝像機在拍攝過程中容易產生椒鹽噪聲,而中值濾波可以有效地去除這種噪聲[5],FPGA 并行的處理方式使處理速度加快,且該方式易于實現。

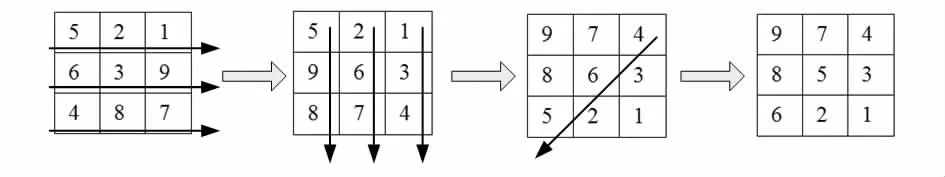

本系統中值濾波選用3×3 模板,利用改進的中值濾波算法進行處理,改進的具體過程以數字1~9 為例,任意填在3×3 模板中進行說明。具體過程如圖4 所示。

在模板中先依次將每一行按照從大到小排列,然后再將每一列按照從大到小排列,最后用第一列的最小值、第二列的中間值、第三列的最大值作比較,得到的中間值即為中值,該方法可以大大縮短運算次數,且適合于在FPGA 上做并行處理。

圖4 3×3 模板下的快速中值濾波Fig 4 Fast median filtering under 3×3 template

2.1.2 紙病圖像邊緣檢測

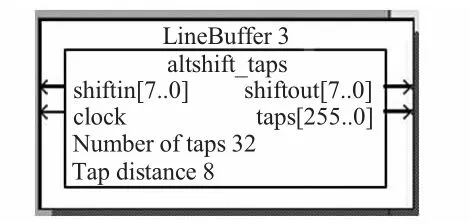

邊緣檢測是為了將紙病圖像中亮度有明顯變化的地方識別出來,Sobel 算子有很強的邊緣性[6],對水平和垂直方向都很敏感,且具有平滑作用,能夠提供較為精確的邊緣方向信息,本系統將Sobel 算子用硬件方式來實現。但值得注意的是,由于是用FPGA 做圖像處理,在保證實時性的同時,SDRAM 只相當于圖像的緩存器,沒有辦法去存取每一個像素的信息,所以,需要一個LineBuffer_3 模塊來緩存圖像數據。在本系統中利用QuartusⅡ工具所提供的參數可設置宏功能Megafunctin 中的移位寄存器宏模塊altshift_taps 實現了緩沖器功能。圖像數據緩存模塊LineBuffer_3通過altshift_taps 配置實現。如圖5 所示。

圖5 LineBuffer_3 模塊配置Fig 5 Module configuration of LineBuffer_3

2.2 軟核模式下的紙病圖像處理

經過預處理可以將紙病圖像區域提取出來,但具體是哪一種紙病還需要進行進一步的處理。紙病辨識是紙病檢測過程中最為核心的部分,辨識結果的準確性將直接影響紙張質量好壞的評定,所以,分類器的選擇十分重要[7]。在本系統中選擇貝葉斯分類器,貝葉斯分類器在給出某些變量的條件下,能使分類所造成的平均損失最小,或分類決策的風險最小。對于待檢測紙病圖像,貝葉斯公式可以計算出該紙病圖像分屬于各類別的概率,即后驗概率。若X 屬于哪個類的可能性最大,就把X 歸于可能性最大的那個類。貝葉斯公式如式(1)

其中,p(wi)為先驗概率,P(X|wi)為條件概率密度,P(wi|X)為在X 出現條件下,樣品wi類的概率。

3 實驗效果與分析

采用FPGA+SOPC 相結合的方法對算法進行分析與分類,其中,適合用FPGA 硬件方式實現的紙病圖像預處理部分為中值濾波與邊緣檢測,而適合用SOPC 的軟件方式實現的紙病圖像處理是特征提取與紙病辨識。

將CCD 相機采集到的紙病圖像進行預處理,這部分因為其邏輯性較強,可以用Verilog HDL 語言編寫。將程序進行Modelsim 仿真,得到的仿真波形如圖6 所示。

圖6 中值濾波仿真波形Fig 6 Median filtering simulation waveforms

從圖6 中可以看到:該系統采用的快速中值濾波方法可以較為準確地得到濾波結果,輸出結果與預期結果相同,說明該方法可行。經濾波的圖像能夠將因相機拍攝而產生的椒鹽噪聲有效去除。

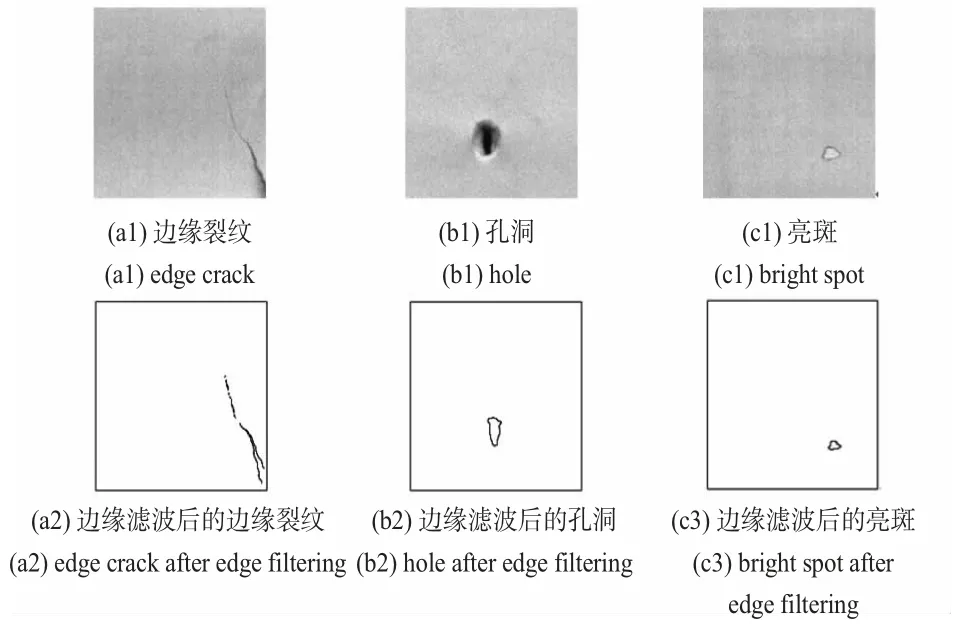

邊緣檢測算子采用的是Sobel 算子,將濾波后的紙病圖像再進行邊緣檢測,得到的紙病圖像如圖7 所示,其中,(a1),(b1),(c1)為預處理前的紙病圖像,分別為邊緣裂紋、孔洞、亮斑;(a2),(b2),(c2)則為經過圖像預處理后的紙病圖像。

圖7 經過圖像預處理后的紙病圖像Fig 7 Paper defect image after image preprocessing

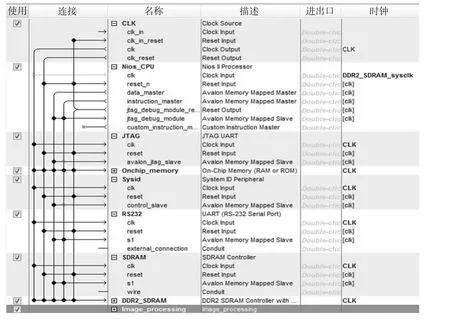

將經過預處理的紙病圖像交由軟件部分進行處理,系統將紙病辨識設計成用戶可自定義的IP 核,可以使用Qsys工具將這些IP 核添加到系統,具體的Qsys 紙病處理系統如圖8 所示。

圖8 Qsys 紙病處理系統配置Fig 8 Configuration of Qsys paper defect treatment system

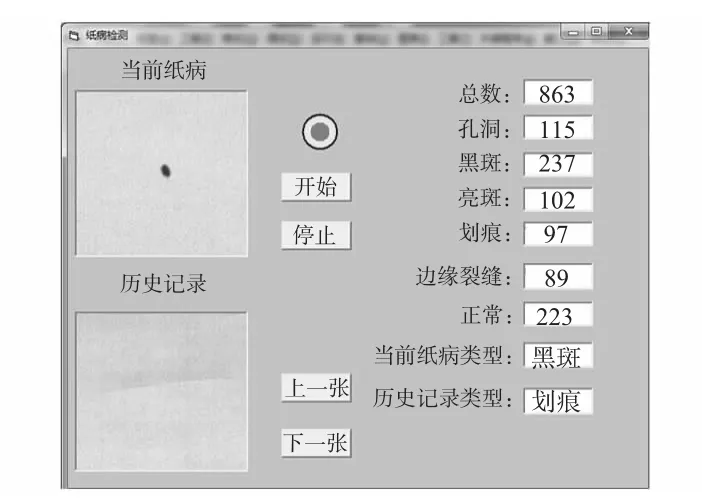

將配置后的系統進行綜合,再將紙病辨識的程序寫入軟核中,經過紙病圖像辨識后上傳給上位機進行顯示,結果如圖9 所示。

圖9 紙病檢測系統界面Fig 9 Interface of paper defect detection system

從圖9 中可以看出:界面左側顯示分為上、下兩部分,上部顯示的是當前辨識出來的紙病類型,而下部顯示的則是之前辨識出的紙病類型,歷史紙病記錄是可以翻閱查詢的。界面右側是紙張總數、不同類型紙病數量、正常紙張數量、紙病類型的顯示。

將在FPGA 硬件平臺上實現的紙病圖像處理過程與PC上用軟件實現的方式進行比較,從而得到本系統與PC 性能的對比表,見表1。

表1 FPGA 與PC 算法時間比較Tab 1 Time comparison of FPGA and PC algorithms

從表1 中可以看出:用FPGA 處理紙病圖像的速度要遠遠小于PC方式,原因在于FPGA是并行處理,不用等到正在運行的算法結束,而PC 則是串行方式來處理。對于更加復雜的算法來說,可使用并行運算的算法越多,越可以體現出FPGA 軟硬件協同處理的優勢。

4 結 論

本文提出了一種基于FPGA 的軟硬件協同實時紙病圖像處理系統,從硬件到軟件詳細概述了該系統的組成、設計及實現。該系統結構清晰,并且可以根據需要進行定制和修改。在紙病圖像處理系統中使FPGA 的利用率最大化,分擔了計算機處理的數據量。通過實驗分析可知:FPGA 的使用大大提高了紙病圖像處理的速度,通過與PC 性能的對比,表明該系統可以滿足紙病圖像處理的實時性要求。

[1] 陳 偉,段發階,董宇青,等.基于DSP+FPGA 分層圖像處理技術的智能相機設計[J].傳感器與微系統,2010,29(12):111-113.

[2] 王炳健,劉上乾.基于FPGA 的紅外焦平面實時圖像處理系統[J].紅外與激光工程,2006,35(6):655-658.

[3] Zahir Larabi,Yves Mathieu.Efficient data access management for FPGA-based image processing SoCs[C]∥IEEE/IFIP International Symposium on Rapid System Prototyping,2009:159-164.

[4] 湯 惟,葛保健.基于FPGA 的SOPC 軟硬件協同設計[J].江漢大學學報,2007,35(3):49-52.

[5] 劉慧中,湯 偉.基于FPGA 的紙病檢測預處理算法的實現[J].中國造紙學報,2014,29(1):53-57.

[6] 楊新華,寇為剛.基于FPGA 的Sobel 算子圖像邊緣檢測算法[J].儀表技術與傳感器,2013(1):102-104.

[7] 院金彪,周 強.基于樸素貝葉斯分類器的紙病離線靜態辨識方法研究[J].中國造紙學報,2014,29(1):58-62.