無源偵察傳感器寬帶信道化接收技術研究

王海濱, 解傳軍, 梁明珅

(1.海軍航空兵學院,遼寧 葫蘆島 125001; 2.哈爾濱工程大學 信息與通信工程學院,黑龍江 哈爾濱 150001)

設計與制造

無源偵察傳感器寬帶信道化接收技術研究

王海濱1, 解傳軍1, 梁明珅2

(1.海軍航空兵學院,遼寧 葫蘆島 125001; 2.哈爾濱工程大學 信息與通信工程學院,黑龍江 哈爾濱 150001)

信道化接收機是無源偵察傳感器系統的核心,研究了基于多相濾波結構的信道化接收機的數學模型,并由此模型設計了一個多信道模擬系統,利用現場可編程門陣列(FPGA)對抽取、濾波、快速傅立葉變換(FFT)等模塊進行了設計,解決了信號高速實時處理與FPGA處理速度之間的矛盾。最后用仿真實驗結果驗證了模型和系統實現的正確性。

無源偵察; 傳感器; 多相濾波

0 引 言

電子偵察是電子對抗中一個非常重要的領域,作為一種新型的無源偵察傳感器,在軍事領域起著至關重要的作用,無源偵察傳感器具有比雷達更大的作用距離,可在更大的范圍內發現目標,已經成為飛機不可缺少的傳感器。隨著雷達技術的飛速發展,電子對抗面臨越來越復雜的信號環境,而作為無源偵察傳感器中的偵察接收機也經歷了幾個發展階段,從早期的模擬接收機發展到窄帶中頻數字接收機[1]。隨著數字信號處理技術和相應器件水平的提高,寬帶數字偵察接收機逐步發展起來,寬帶數字偵察接收機具有設備量小、算法靈活、功能易于擴展等優點[2]。在實現寬帶接收機時,存在最主要的問題就是如何在處理器中實時地處理高速A/D轉換器采集到的輻射源信號。一般傳統的數字信道化接收機采用短時傅里葉變換技術,這種結構的數字接收機在具有高時頻分辨率的需求時,對處理器的處理速度提出了更高的要求。

本文主要研究在傳統接收機的基礎上引入了多相濾波的結構,并給出了基于現場可編程門陣列(FPGA)的系統實現方法。

1 寬帶數字信道化接收機模型

1.1 無源偵察傳感器系統組成

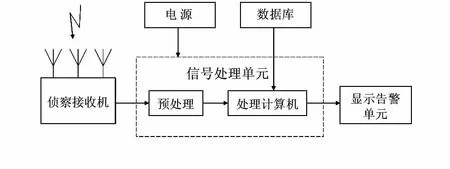

無源偵察傳感器能通過偵收、測量、分析確定輻射源的信號特征,進而確定目標平臺的類型[3]。無源偵察傳感器系統的主要組成如圖1所示,主要包括偵察接收天線、偵察接收機、信號處理單元、數據庫、顯示告警單元以及電源組成。其中,偵察接收機是偵察傳感器中的核心單元,能對天線接收到的信號放大、變頻和參數測量,并經過數字采樣后變成數字信號,作為信號處理機的輸入信號。

1.2 多相濾波的基本原理

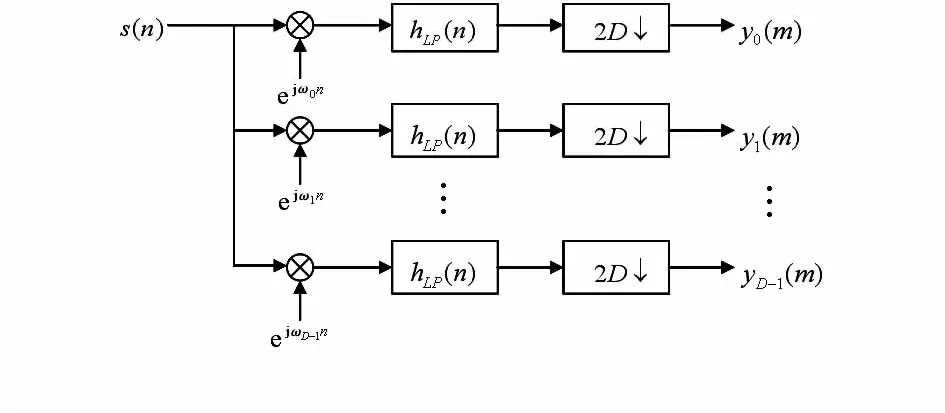

對于信道化接收機而言,其抽取器位于濾波器之后,所以,當抽取率很大或者濾波器的階數很高時,計算效率將成為限制系統性能的重要因素[4]。圖2給出了基于低通濾波器組的實信號信道化接收機的實現結構。

圖1 無源偵察傳感器系統的結構

圖2 基于低通濾波器組的實信號信道化接收機

這里,引入多相濾波器結構,多相濾波結構是從抽取濾波轉換而來的[5],其本質是將傳統抽取濾波中先濾波、再抽取的處理過程,通過數學推導,變換為先抽取,再濾波的過程,這樣就大大降低了計算量。

從圖2中可以看出:多相濾波器是由D組按一定方式抽取而成的通用有限沖擊響應(finite impulse response,FIR)子濾波器組成的。實現多相濾波器設計的步驟為:首先按照抗混疊濾波器的參數要求[6],按照一定的設計準則,根據原型理想低通濾波器的頻率響應確定所需要的濾波器類型和階數N,得到對應沖擊響應h(n),然后根據式(1)確定多相濾波器

hk(n)=h(nD+k),k=0,1,2,…,D-1.

(1)

1.3 改進后的實信號信道化接收機建模

由圖2可得到第k信道的輸出為

(2)

其中,yk(m)為經過抽取后的第k路輸出信號。定義

(3)

則有

(4)

假設

xp(2m)=?Sp(2m)ejωk2mD」·hp(2m),

(5)

則

(6)

(7)

(8)

其中

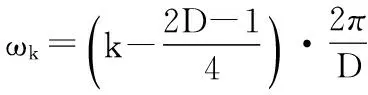

(9)

(10)

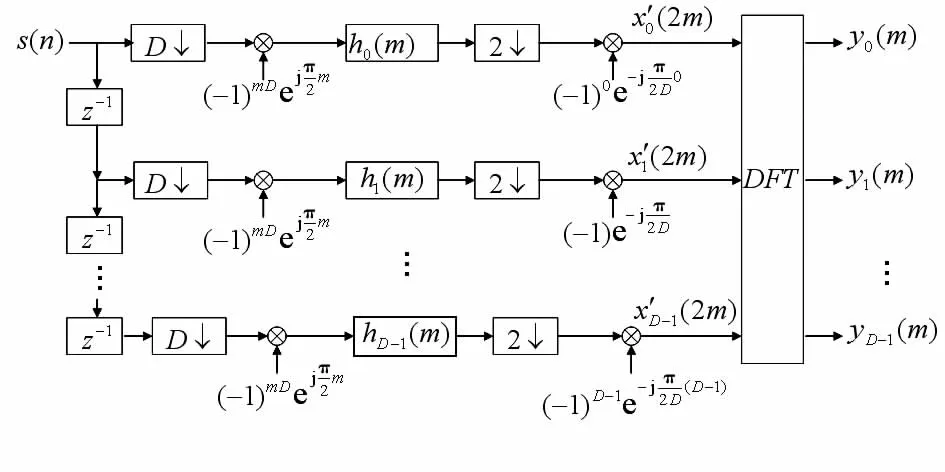

改進后的信道化接收機數學模型可以根據上述公式得出,如圖3所示。

圖3 改進后的信道化接收機模型

2 信道化接收機的FPGA實現方法

對于多通道數字接收機的實現方法,既可以通過多通道數字下變頻來實現,也可以由數字信道化接收機來完成[7]。對應的數字信號處理器件主要有數字下變頻(DDC)芯片和IPCORE,而DDC芯片主要是針對窄帶數字接收機,如INTERSIL公司的HSP50216,其最高輸入數據率為70MSPS,能處理的最大信號帶寬為1MHz,NCO分辨率為0.012Hz,通道數為4,最大抽取數為65 536,可以實現對AM,FM,BPSK,QPSK,FSK和DPSK等調制方式的信號進行處理[8]。一般情況下,DDC芯片的處理速率在100MSPS左右,50MHz帶寬,通道數一般為4,顯然,在雷達信號測量時是滿足不了需求的。IPCORE則可適用于窄帶和寬帶系統,如PENTEK公司的IPC422,可以實現最大處理采樣率296MSPS,最大處理帶寬為148MHz,窄帶系列的信道數為32。盡管IPCORE的使用靈活,指標更高,但適用范圍較窄,且價格昂貴[9]。因此,選用FPGA實現多相濾波數字信道化接收機的功能,此種設計方案具有較好的實用性,并且在類似的設計中具有較強的通用性。

綜合考慮以上因素,采用Altera公司Cyclone系列FPGAEP1C6進行多相濾波數字信道化的硬件設計,開發工具為QuartusⅡ。具體數據流程是將A/D轉換后的數字中頻信號的載波頻段平均分成16個子頻段并分別下變頻到基帶,FPGA主要功能則是實現數據預處理單元、多相濾波器組和快速傅里葉變換(FFT),采用VerilogHDL進行硬件設計,并通過Modelsim工具進行綜合仿真。

通過FPGA來實現多相濾波器組信道化接收機主要根據圖3所示的數學模型進行設計。接收機處理的輸入信號帶寬為100MHz,經過A/D轉換,帶通采樣頻率為200MHz,采用多相濾波技術對數字中頻信號進行信道劃分、下變頻、濾波和降速處理。設計中把信號覆蓋帶寬分成16個子頻帶,每個子頻帶帶寬為6.25MHz,便于后續DFT運算時采用FFT來實現。經過多相濾波器組信道化接收處理,不同頻段的信號被分配到不同指定信道,所接收覆蓋帶寬內的信號被分配到各個不同的信道進行輸出,其余各信道為帶外信號。在系統實現過程中采用QuartusⅡ軟件完成對FPGA的邏輯設計,多相濾波信道化接收機的電路結構主要包括延遲抽取、FIR濾波、FFT模塊,各個模塊均采用VerilogHDL編寫。

FIR濾波模塊主要實現對各信道信號的濾波功能,每個信道的濾波器均是低通原型濾波器的多相分量,系統設計中多相濾波器組由16個子濾波器組成,每個子濾波器為16階,原型低通濾波器參數是:通帶頻率3.2MHz,阻帶截止頻率為3.5MHz,通帶紋波1dB,阻帶衰減60dB,低通原型濾波器階數為256。根據多相濾波器組與低通原型濾波器的系數關系,可以得到多相濾波器的各階系數,濾波器系數量化為16bits。信道化接收機的重點則是FFT設計,系統中實現了32點并行基2復數FFT,對于FFT的設計實現采用流水線結構,根據32點蝶形運算算法,在每一級只設置1個蝶形運算單元,由2個累加器和3個旋轉因子乘法器組成,前兩級運算只涉及加減法運算,后三級運算中涉及到乘法運算,采用流水線結構,能縮短組合邏輯間的延時,從而提高系統信號處理的速率。

3 仿真實驗與分析

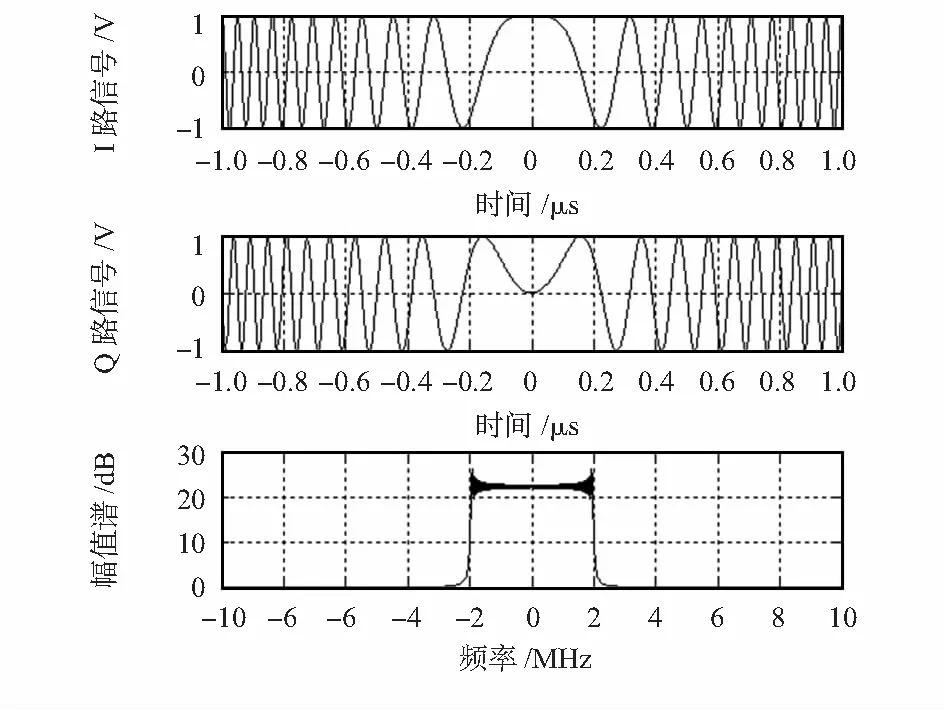

為了驗證無源偵察傳感器信道化接收系統設計的正確性,還進行了仿真實驗。由于要驗證信道化接收是否能完成對前端輸入信號的預期處理功能,因此,需要給系統輸入相應的數字信號,并且數據輸入速率為200MHz,輸入的信號為線性調頻信號,將已調信號作為作為A/D采樣后的數字信號,在QuartusⅡ仿真軟件中作為系統的輸入信號,并進行綜合仿真,得到系統的輸出結果,并將其存入。TBL文件,最后通過讀取.TBL文件中的結果數據,繪制出輸出信號的波形,仿真結果如圖4所示。

圖4 信道化接收機輸出信號波形與幅值譜

圖4給出了第6信道輸出信號,通過輸出結果與輸入信號比對,發現通過多相濾波信道化接收機的波形失真較小,并且沒有輸入信號的其它各信道輸出為零。可見,系統設計的多相濾波信道化接收方法能夠很好地實現對寬帶信號的接收,從而驗證了基于多相濾波寬帶信道化接收技術的正確性和可行性。

4 結 論

本文重點研究了基于多相濾波結構的信道化接收機系統的設計技術,FPGA具有高速數據處理能力和大量的乘法器、存儲器以及邏輯單元,在數字濾波器設計方面有顯著優勢,這些都為無源偵察傳感器寬帶信道化接收技術研究提供了條件。本文建立了寬帶數字信道化接收機模型,給出了采用FPGA對抽取、濾波、FFT等模塊進行設計的具體方法,仿真實驗驗證表明:本文提出的寬帶信道化接收技術是正確的、高效的和靈活的。

[1] 馬昆林,亢春梅.國外機/艦載傳感器的發展現狀[J].傳感器與微系統,2009,28(5):1-3.

[2]TsuiJBY,StephensJPSr.Digitalmicrowavereceivertechnology[J].IEEETransactionsonMicrowaveTheoryandTechniques,2002, 50(3):699-705.

[3] 劉 平,靳成英,陳曾平.一種基于短時FFT的寬帶數字偵察接收機設計[J].信號處理,2008,24(6):988-991.

[4] 周 欣,吳 瑛.基于多相濾波的寬帶接收機信道化算法研究[J].現代雷達,2006,28(11):71-74.

[5] 王旭東,劉 渝.全并行結構FFT的FPGA實現[J].南京航空航天大學學報,2006,38(1):96-100.

[6] 楊小牛,樓才義,徐建良.軟件無線電原理與應用[M].北京:電子工業出版社,2001:21-87.

[7] 胡廣書.數字信號處理(理論、算法與實現)[M].北京:清華大學出版社,2004:179-191.

[8] 吳繼華,王 誠. Altera FPGA/CPLD設計(高級篇)[M].北京:人民郵電出版社,2005.

[9] 王永明,張爾揚,王世練,等.基于多級信道化的超寬帶搜索接收機設計與實現[J].信號處理,2010,26(1):121-126.

Research on wideband channelized receiving technology for passive reconnaissance sensor

WANG Hai-bin1, XIE Chuan-jun1, LIANG Ming-shen2

(1.Naval Air Force College, Huludao 125001, China;2.College of Information and Communication Engineering, Harbin Engineering University,Harbin 150001, China)

Channelized receivers is the core of passive reconnaissance sensor system,a math model for channelized receiver based on polyphase filtering structure and a multichannel simulation system is designed based on this model, the extract, filtering and FFT modules are designed based on FPGA,the contradiction between signal high-speed real-time processing and FPGA processing speed is solved. At last, the simulation experimental results verify the model and system realization is correct.

passive reconnaissance; sensor; polyphase filtering

2014—11—07

10.13873/J.1000—9787(2015)02—0073—03

TN 971

A

1000—9787(2015)02—0073—03

王海濱(1982-),男,內蒙古赤峰人,講師,研究方向為電子對抗、信息對抗等。